王阳元院士:以性能功耗为标尺、以3D集成为方向,以10倍投资强度持续支持集成电路产业

编者按:本文作者王阳元院士,首发于科技导报,集微网经授权发布。

我国集成电路产业短板和市场占有率不高的现状,促使我们要认真思考如何以创新驱动发展。

十九届五中全会提出:“增强机遇意识和风险意识,立足社会主义初级阶段基本国情,保持战略定力,办好自己的事,认识和把握发展规律,发扬斗争精神。”

为此,就“十四五”发展规划和2035年远景目标提出一些建议。

创新驱动发展

“摩尔时代”向“后摩尔时代”转变

随着物联网、大数据、云计算、人工智能和量子计算的发展速度越来越快,对集成电路创新量的需求也越来越多,质的需求也越来越高。

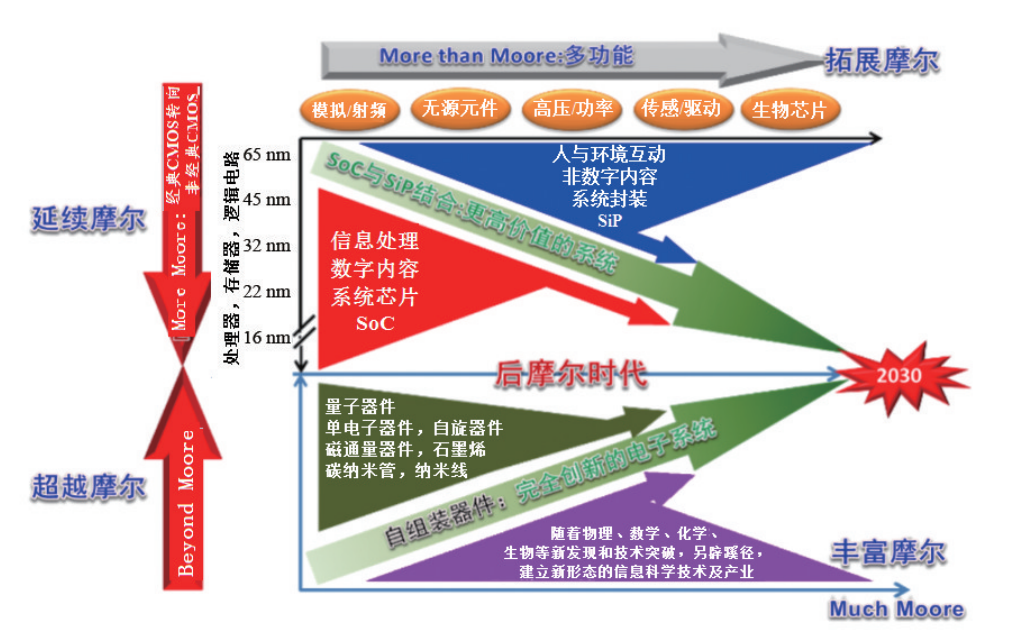

一般来说,人们将16 nm非经典CMOS作为基础器件以后的时代称为“后摩尔时代”。

随着加工尺寸的不断缩小,微电子学科正在转向纳电子学科,“摩尔时代”正在转向“后摩尔时代”,沿着延续摩尔、拓展摩尔、超越摩尔与丰富摩尔的路径不断向前发展。

后摩尔时代集成电路的发展

1)延续摩尔(More Moore)

集成电路加工的特征尺寸以及芯片上集成的晶体管数将继续沿着摩尔预测的规律发展。

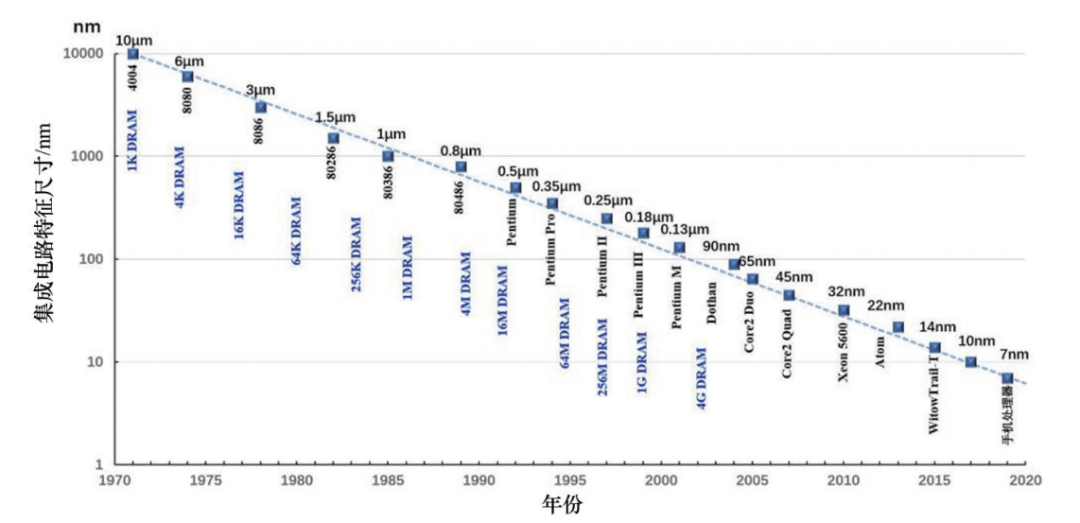

其实,最早的集成电路特征尺寸为10 μm,随着加工技术的进步,集成电路的特征尺寸呈规律缩小,尤其在0.8 μm以后。

特征尺寸继续缩小主要表现在系统芯片SoC(system on chip)上。

特征尺寸每缩小至上一节点的70%,芯片性能可以提高15%,面积减少50%,功耗降低40%,成本减少35%。

2)拓展摩尔(More than Moore)

拓展摩尔的主要表现形式是发展集成微纳系统(如MEMS,NEMS)和系统封装(System in Package,SiP),即将不同工艺、不同功能的器件(模拟、射频、高压、功率、传动、驱动、生物等)封装在一个集成电路中,形成多功能集成系统。

集成电路特征尺寸的缩小及相应典型产品(根据公开资料整理)

3)超越摩尔(Beyond Moore)

主要是各种新器件的研发,包括量子器件、单电子器件、自旋器件、磁通量器件、石墨烯器件、碳纳米管、碳纳米线等。

4)丰富摩尔(Much Moore)

建立新形态的信息科学技术及产业。

增强原始创新能力

2020年9月11日,习近平总书记在科学家座谈会上的讲话中指出:“基础研究是科技创新的源头。在激烈的国际竞争面前,在单边主义、保护主义上升的大背景下,我们必须走出适合国情的创新路子,特别是要把原始创新能力提升摆在更加突出的位置。”

一部集成电路发展史就是一部原始创新的发明史。在材料、器件结构和专用设备的创新中,正在研发、并期待进入量产阶段的关键技术有:

专用材料:高频、高速、高功率、抗辐照、耐高温器件使用的化合物半导体材料,包括III-V族(GaAs、GaN、InP)、II-VI族(ZnS、CdTe)、IV-IV族(SiC)、氧化物半导体(ZnO、Ga2O3、NiO、MoO3)等;新型互连材料(钴Co、钌Ru、碳纳米管);碳基材料(石墨烯,碳纳米管);纳米线材料以及量子线材料等。

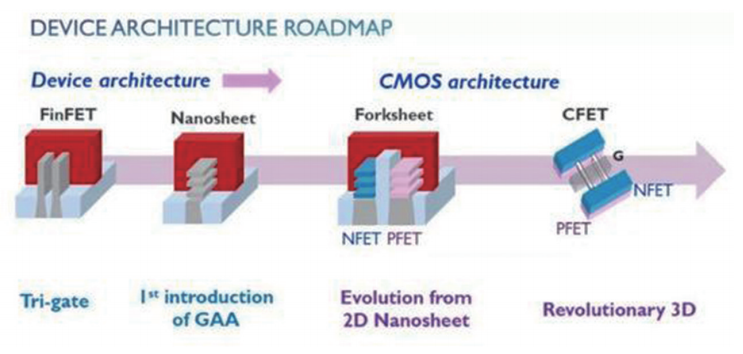

器件结构:垂直场效应晶体管(VFET)、互补场效应晶体管(CFET)、围栅场效应晶体管(GAAFET)、隧道效应晶体管(TFET)、自旋场效应晶体管(SFET)、磁阻存储器(MRAM)、阻变存储器(RRAM)、相变存储器(PCRAM)、量子集成电路(quantum IC)及生物医学芯片(biomedical chip)等。

专用设备:最主要是7 nm以下工艺必备的EUV,且要不断提高EUV的数值孔(numerical aperture,NA)。

集成电路技术与产业的重要发明和预测

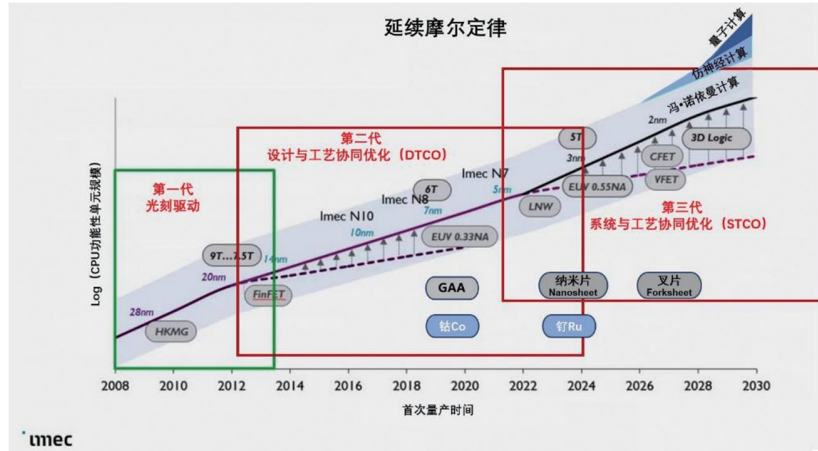

微电子研究中心(IMEC)发布的最新技术路线表明,在28 nm技术节点上,采用了高K金属栅(HKMG)工艺;在16 nm/14 nm节点之后,器件结构开始转向3D的Fin FET,从7 nm/5 nm节点开始,钴代替铜成为互连的新型材料。

同时,0.33 NA的EUV正式投入生产;围栅晶体管结构将部分取代Fin FET结构,成为主流产品结构。

2005年,北京大学微纳电子研究院的年轻团队就对围栅器件结构、基础理论、输运特性和可靠性进行了全面研究,取得了在世界范围内最早的研究成果。

按目前预测,韩国三星公司在3 nm技术和台积电2 nm技术节点上都将采用围栅结构,且在2~3年内实现量产。

北京大学微纳电子研究院还正在进行隧道效应晶体管等多种超低功耗器件的新结构、新原理研究,隧道效应晶体管正在中芯国际进行量产试验,有可能在3~5年内用于低功耗物联网系统中。

清华大学的可重构设计是芯片架构设计的原始创新,已开始在Intel的产品开发中得到应用。

从4 nm/3 nm节点开始,采用“半镶嵌”(semi damascene)技术的钌将成为主流互连材料,EUV的数值孔径将从0.33提升到0.55,纳米片(nanosheet)结构的产品开始进入批量生产流程。

IMEC最新技术路线 根据IMEC在ITF(2017~2020年)上发布的最新路线图多图综合整理

在2 nm技术节点上,将采用叉片(fork sheet)结构,其中n型和p型纳米片紧密地靠在一起,并且其间有一层“绝缘墙”,因其截面类似于餐叉得名。

同时,通过3D堆叠形成的垂直场效应晶体管(VFET)、互补场效应晶体管(CFET)结构将大大减小标准单元的面积,以这种结构设计的集成电路产品开始量产。

而且,作为延续摩尔定律的第一代技术为光刻驱动,第二代技术中加入了设计与工艺协同优化(DTCO)的内容,第三代技术则再加入系统与工艺协同优化(STCO)的举措。

器件结构路线示意 来源:IMEC

加强基础技术研究

1)根据集成电路从研发到批量生产10年跨度的规律,对关键的基础技术研究要提前10年进行部署。

要对“10年坐冷板凳”的基础技术研究人员给予特殊政策,不应追求”急功近利”的结果,更不能以论文论英雄。

2)基础研究要实行产、教、研紧密结合,特别要注重激发企业研发的活力,以扩大基础研究成果的转化渠道和缩短转化进程,实现在人才交流、成果共享等多方面的渗透、交叉与融合,不要让研究成果仅仅停留在论文上。

以Fin FET为例,由于Intel成功应用,从而驱动了全球集成电路技术由2D登上了3D的阶梯。

3)加强低功耗器件研究。

对小于7 nm工艺的逻辑器件而言,要坚持两条腿走路,一方面要加强新结构、新原理、新材料的创新研究,另一方面要看到今后集成电路的技术进步节点将不再以特征尺寸为标尺,而以提高系统的性能/功耗比为切入点,降低功耗成为重要指标。

从经济角度看,也不必单纯地以缩小特征尺寸为唯一追求目标。

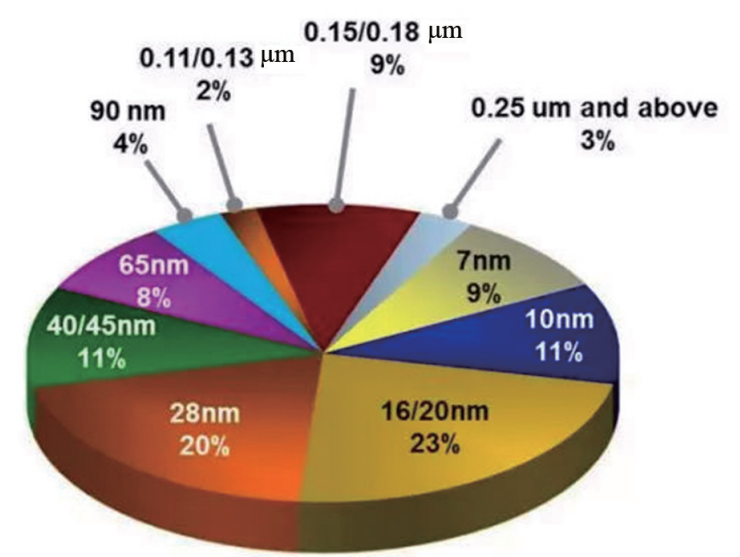

从台积电不同工艺对2018年营收的贡献,可以看出,当前,10 nm以上工艺的贡献为80%。也就是说,从企业经营的角度看,大于10 nm工艺的产品现在仍是对企业营收贡献的主流。

2018年,TSMC不同工艺对营收的贡献

4)延展基础研究的广度,争取在模拟电路、数模混合电路、射频电路、功率电路、微纳机电系统等领域取得技术和市场的领先地位。

5)加强基础研究的国际合作,融入国际化的集成电路产业链中。

以中芯国际的创建为例,1999年以前,中国的集成电路产业投资者单一,无锡工程、908工程、909工程均为国家投资;市场单一,仅为国内市场;人才单一,绝大多数技术专家和企业管理者均为国内人员。

2000~2009年,笔者在和张汝京博士创建中芯国际和任董事长期间,与海内外同仁一道,使中芯国际真正在机制、市场、技术、投资和人才各个方面都实现了国际化。

迈向产业强国

发展目标预测

预测到2035年,发展目标达到以下水平。

1)以2019年世界半导体市场4123.06亿美元,中国集成电路产业销售额(三业叠加)7562.3亿元(1096亿美元)为基数进行测算:

2019~2035年,世界集成电路市场年平均增长率设为5%(2009~2019年为6.18%),至2035年,市场总额达到9000亿美元;

2019~2035年,中国集成电路产业销售额年平均增长率设为10%(2009~2019年为21.04%),至2035年达到5037亿美元(设计、制、造封装三业叠加),其值为世界市场的56%(非占比)。

按WSTS的统计标准,中国集成电路产业的销售额占世界市场的比例由5%提高到30%,跻身集成电路产业强国的行列。

2)国民经济领域需求的芯片自给率提高到80%。

3)能够独立自主地设计和生产国家安全及国防建设所需的重要与关键集成电路产品,自给率达到100%。

4)拥有大量的微电子技术专利、自主知识产权产品标准,建成具有中国特色的集成电路研发体系,为本土企业提供知识产权保护。

5)以关键设备和主要材料为标志的集成电路支撑行业能够基本满足产业发展需要,集成电路产业专用设备不再受制于人。

6)集成电路大生产技术水平与国际先进水平同步,实现2~1 nm技术节点工业化大生产技术突破。

7)在基础研究领域,原始创新能不断地涌现,在新器件结构、新材料、新工艺研发和生产的某些领域引领世界发展潮流。

对实施举措的建议

1)以10倍于当今的投资强度,持续加大对集成电路产业的投资力度。

一是在世界半导体市场增长率下降的低谷期进行投入;二是要加强创新投入,尤其是对基础研究的、不求短期回报的投入。

要加强对国家投资的调控能力,必须将有限的资金在有限的时间和有限的空间内集中使用,切不可在地域或部门的利益分配中,避免造成资金的游移、分散和迟延现象,坚决杜绝低水平重复建设。

2)以性能功耗比作为标尺,以3D集成为发展方向,沉下心来进行器件结构、材料、EDA算法等基础研究工作,使其能够产生革命性的创新成果。

要扩展研究成果转化为生产力的渠道,缩短研究成果转化为生产力的时间,使其在产业发展中产生价值,同时要注重科研成果的知识产权保护工作。

3)以举国之力攻克最重要的材料(硅圆片、电子气体)、设备(曝光机)难关,努力提高国产EDA软件的系统集成水平,扩大其在国内外市场的占有率。

4)建设1~2家IDM型企业,缩短设计与制造间的流程,缩短产品与系统应用的距离。

该企业能够在3~5年内做到生产线装备和生产材料来自多元和自主可控,不再受任何霸凌者的制约。

5)国际合作是大趋势,对于一般材料和设备的研发或采购,要融入国际产业链和生态链,构建国内国际双循环的发展格局。

6)加大贯彻执行《新时期促进集成电路产业和软件产业高质量发展的若干政策》的力度,各地区、各部门要尽快出台《若干政策》中关于财税、投融资、研究开发、进出口、人才、知识产权、市场应用以及国际合作的实施细则。尤其要对从事集成电路产业和研发等相关工作的人才所得税提供优惠政策。

7)结合集成电路科学与工程学科的建立,将集成电路专业人才的培养规模扩大到当前培养人数的10倍。

改革教育和培养方式,在培养理科博士的同时,加强工程博士的培养,尤其要注重复合型、创新型人才的培养。给予创新领军人才更大的技术路线决定权和经费使用权。

要建设一支来自产业和学校共同组成的教师队伍,与产业发展进一步融合。

改变对专业人才的评价体系,破除“唯论文、唯帽子、唯职称、唯学历、唯奖项”的观念,要强调人才对科学前沿、国家战略需求和经济主战场上的贡献,创造一种留住人才、保护人才的机制和环境。

实现强国梦想

在人类发展的历史上,迄今国家与国家之间的竞争从未终止,无论是表现为和平方式的巧取,还是表现为战争方式的豪夺。

为了维护国家利益,核心技术已经成为国家间竞争最重要的砝码。为此,任何一个国家都不会向他国出售本国的以核心技术构成的核心竞争力。

在以集成电路和软件为基础的信息时代,在全球已经联网的智能社会,集成电路正在成为国家安全的重要屏障。

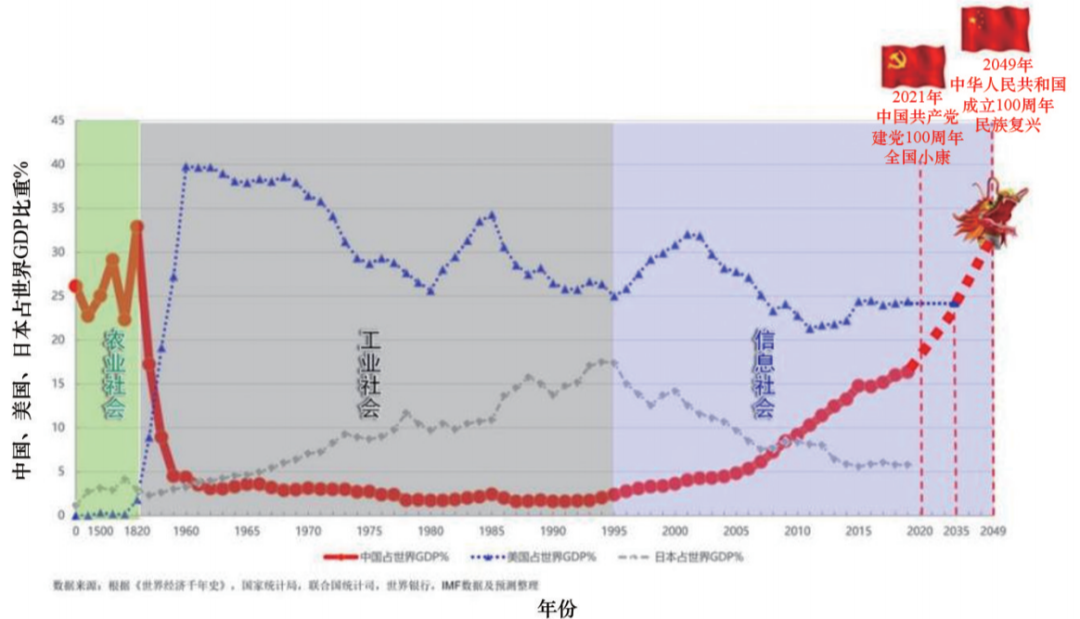

“强自立,弱被欺”,是历史、也是现实世界的真实写照。1820年,中国是世界第一大国。由于没有跟上工业社会发展的步伐,1840年鸦片战争以后,在中国上演了无数被外夷凌辱和欺侮的悲剧。

进入21世纪后,中国的经济飞速发展,中国的国际政治地位不断提高,中国的和平崛起,实现以合作共赢为目的的国际外交政策,中华民族的复兴已成为当今中国发展的主旋律。

相信历经200年的马鞍型曲折,在驾驭信息社会的浪潮中,一定能够在中华民族的复兴之路上实现强国的梦想,中华民族的才智将展现更加灿烂的辉煌。

中国、美国和日本占世界GDP的比重

王阳元,微纳电子学家,中国科学院院士。现任北京大学教授,北京大学微纳电子学研究院首席科学家,IEEE Life Fellow,IEEF ellow,工业和信息化部电子科学技术委员会顾问,国家集成电路产业发展咨询委员会副主任。研究方向为微纳电子学的新器件、新工艺技术和新结构电路。

原始报告请点击《掌握规律,创新驱动,扎实推进中国集成电路产业发展》

高通胜诉!无需支付Arm芯片设计许可费用

专利申请

专利申请

知识产权质押融资

知识产权质押融资

专利地图分析

专利地图分析

版权登记

版权登记

集成电路布图设计

集成电路布图设计

商标交易

商标交易

商标申请

商标申请

专利交易

专利交易

专利无效

专利无效

热门评论