Virtuoso Studio:Device-Level 自动布局布线已成现实!

基于 Cadence 30 年的行业知识和领先地位,全新人工智能定制设计解决方案 Virtuoso Studio 采用了多项创新功能和新的基础架构,实现无与伦比的生产力,以及超越经典设计界限的全新集成水平。在本文中,您将了解优异的模拟设计工具如何变得更好,并助您解决挑战性的设计问题。

半导体产业正在快速发展,对模拟/混合信号设计的需求也在迅速增加。然而,由于需要创建既符合设计规则又符合设计意图的布局,设计流程的周转时间很长。模拟布局创建基本需要依靠纯人力,因为其很难针对用户意图实现自动化以满足设计约束。此外,分组和匹配这些重要需求也非常耗时且难以实现,对先进工艺节点的追求迫使用户需要从可制造性和可靠性的角度考虑许多复杂的要求。Virtuoso Studio 中的定制化自动布局布线(APR)解决方案能从整体上看待这些问题,为解决上述瓶颈提供了自动化的解决方案。

应对先进工艺技术

除了复杂情形的设计规则外,先进节点还对模拟电路的传统设计方法增加了额外限制。虽然模拟电路通常需要广泛的器件尺寸以实现精度和性能,但由于密度和制造原因,现在的版图布局需要更加均匀性。由于功能性密度的增加和器件的统一化,器件分组与阵列也变得更加复杂,满足用户对布局布线的预期也更具挑战。

因此,我们需要新的工具和方法,来自动实现这些节点上模拟版图的布局:处理工艺的复杂性和 LDE 效应,确保一致性,保留设计意图,并允许用户轻松和重复创建同类布局,且无需冗长的学习时间。

简介:Virtuoso Studio Device-Level 自动布局布线(APR)解决方案

识别基于网格基础架构的结构化布局方法,是处理工艺复杂性的关键。利用 Virtuoso Studio 可以将先进工艺节点的挑战转化为机会,反过来有助于从自动化的角度弥合定制和数字设计解决方案之间的间隙。通过一个基于器件尺寸和工艺规则且支持不同宽度和间距网格的系统,为自动布局、填充和布线引擎生成复杂的 DRCs 规则,同时遵守拓扑约束以及设计和电气意图。

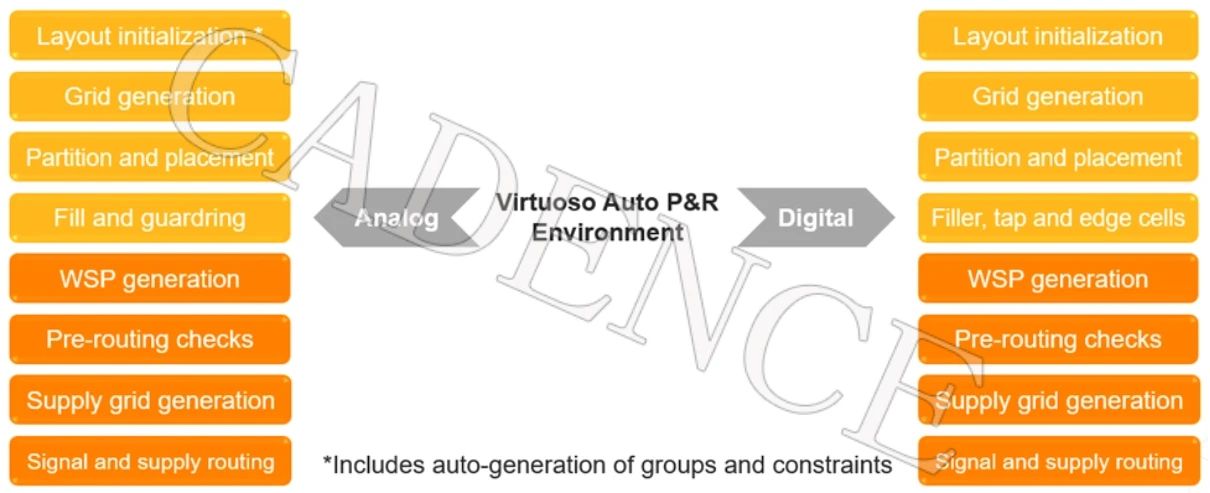

Virtuoso Studio 中的 Device APR 解决方案与全新的 Stdcell APR 解决方案互补,该解决方案将数字引擎无缝集成到 Virtuoso Studio 中。在这些节点中,自动化模拟解决方案与数字解决方案没有太大区别,用户可以在 Virtuoso Studio 各项功能间无缝切换。

Virtuoso Studio Device APR 从功能性维度提供了这一领域最全面的解决方案,涵盖了布局设计流程的各个方面,并实现了增强和自动化。具体包括:

1.自动化节点和设计相关设置开箱即用的解决方案

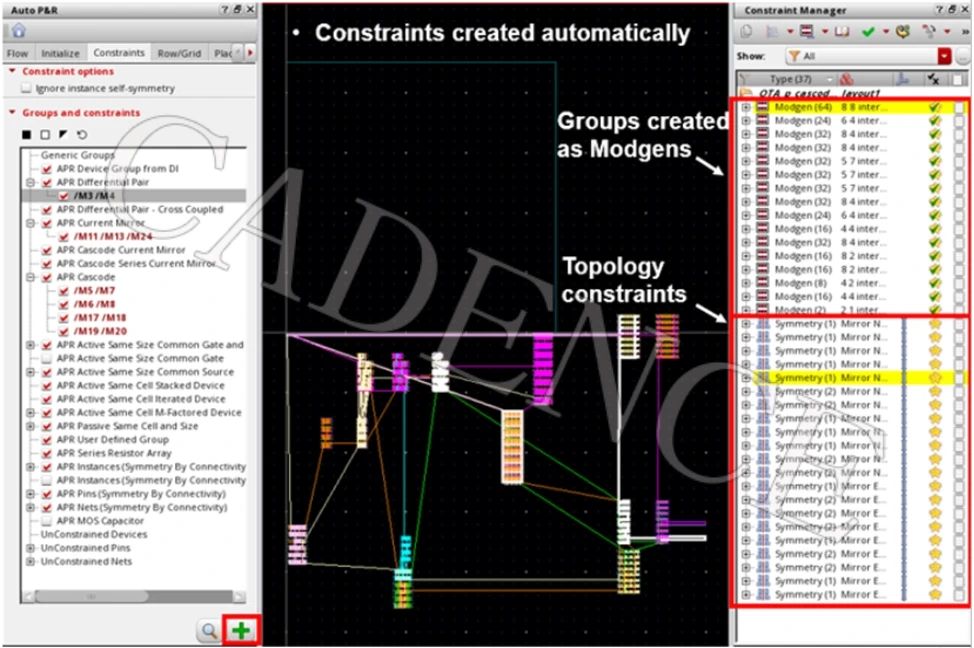

2.根据模拟设计要求和用户意图自动分组和创建约束

3.布局图驱动的群组自动重塑,保留用户意图

4.自动生成布局布线网格,并将设计中的非统一器件考虑在内

5.基于网格的分组和约束驱动的自动布局,包括填充和隔离插入

6.自动生成基于网格的电源输送网络

7.具备高性能和 QoR,基于网格的约束驱动自动布线

8.支持特殊布线拓扑以实现电气正确性

9.允许用户通过辅助编辑进行干预,帮助设计师实现更优的模拟布局质量

10.通过统一的基于任务的 GUI 改善和简化用户体验

11.完整的布线环境,采用类似电子表格的界面,管理和检查所有布线约束、计划、运行和分析布线

总结

Virtuoso Studio 的 Device Level 自动化布线布局解决方案是模拟布局设计的转折点。该解决方案可以逐步引导工程师完成对各项功能的探索,最终实现完整的自动化布局。为了易于使用,此用户界面经过专门设计,为布局和电路设计师创造最佳体验,而自动化引擎也能支持先进工艺节点的大量器件。凭借诸如智能器件分组、精确的器件模态控制、分组和匹配驱动的自动布局、自动填充和隔离、自动生成电网以及自动布线控制以满足电气需求等功能,Virtuoso Studio 器件级 APR 为模拟布局设计提供了最全面的自动化解决方案。模拟布局自动化的未来已至,Virtuoso Studio 则是通往它的途径。

【个股价值观】新洁能:四大平台功率全系覆盖,车规应用提振业绩回暖

专利申请

专利申请

知识产权质押融资

知识产权质押融资

专利地图分析

专利地图分析

版权登记

版权登记

集成电路布图设计

集成电路布图设计

商标交易

商标交易

商标申请

商标申请

专利交易

专利交易

专利无效

专利无效

热门评论