专家解读|硬件调试的复杂性 — 第 2 部分

by Ariel Hershkovitz|CEVA’s Senior Manager of Customer Solutions

介绍

在上一篇文章(硬件调试的复杂性 — 第 1 部分)中,我介绍了程序员将软件嵌入芯片的复杂性,及其在调试时将面临的挑战。我谈到了程序员在将其软件移植到这个复杂环境中时可能会遇到的各方面困难,这通常会涉及很多手工制作的软件和硬件组件。在这篇文章中,我将更深入地探讨 CEVA 软件开发工具及其提供的功能,以帮助管理 DSP 编程和调试所面临的挑战。

CEVA 软件开发工具

CEVA 软件开发工具(统称为 SDT)包括软件工程师所需要的全部工具,可轻松有效地对 CEVA DSP 平台进行编程:在软件模拟平台或硬件上对 DSP 应用程序进行编译、链接、调试和分析。另外,还可通过这些工具对目标硬件上软件和硬件的内部状态进行可靠、清晰和便捷的观察和控制。下面的图 1 显示了 SDT 与各种工具之间的关系,我将在下文中进一步论述。

图 1:SDT 基本组件框图。SDT IDE 可触发构建过程,通过编译器和二进制工具生成 DSP 应用程序。它还可以调试实际芯片或通过软件模拟调试 DSP。

编译器

由于 CEVA DSP 具有不同的硬件功能,这些处理器进行编程所采用的汇编语言必然是 CEVA 所独有的。CEVA 的 C/C++ 编译器将从用户源代码生成优化的汇编操作,从而产生紧凑且快速的汇编码。许多情况下,编译代码的执行时间与手动优化汇编码的执行时间相当;但是,您也可以添加自己的汇编码,在这种情况下,您可能需要在应用程序中手动调整代码。

链接器

CEVA 链接器可收集 C/C++ 编译器和汇编器生成的所有二进制对象文件,链接静态库(由 CEVA 或第三方提供),解析所有地址引用并生成一个可随时在 CEVA DSP 目标上执行的应用程序。目标可以是软件模拟器,也可以是实际硬件。可以使用 CEVA 调试器控制执行,也可以在无外设模式下运行(例如,从板载闪存引导时)。CEVA 链接器的特点是能够执行全局程序优化,最大限度地减少代码存储器中符号引用所使用的内存量。

调试器和分析器

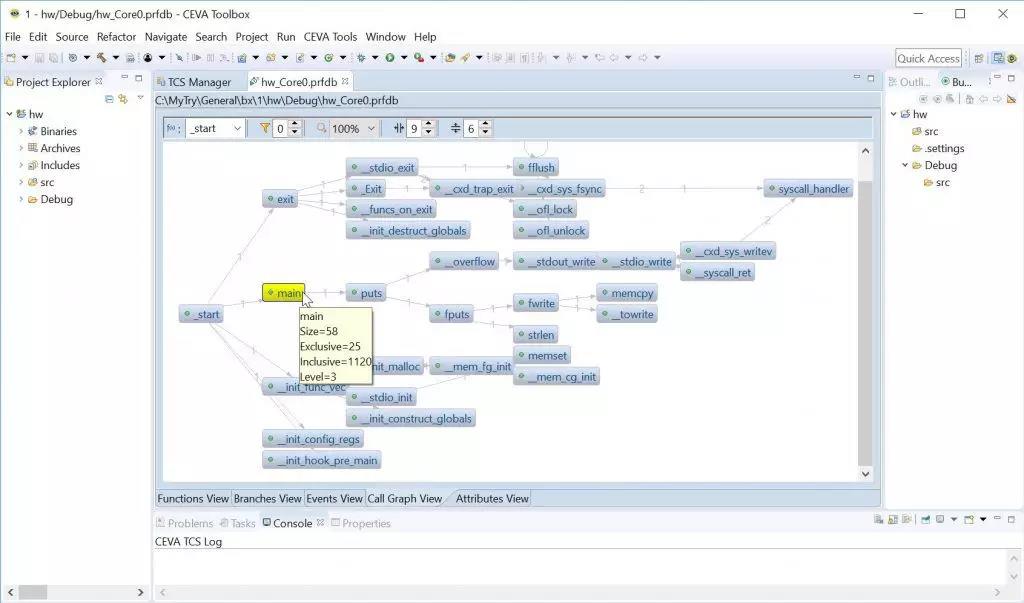

CEVA 调试器作为 Eclipse IDE 插件或标准 SystemC API 提供,允许您在 CEVA DSP 模拟器或实际目标硬件上执行应用程序。除了调试功能外,调试器还可在执行期间收集分析反馈信息,以发现性能瓶颈、执行时间或内存使用情况。此分析信息以图形方式显示,以便查看。

图 2:CEVA SDT ToolBox IDE 分析结果调用图视图:程序流的可视化。

图 3:CEVA SDT ToolBox IDE存储器事件分析结果视图:延迟导致的存储器事件的详细信息。

调试器自动化可通过 Eclipse ISE 内置脚本支持程序 (EASE) 提供支持,也可通过将调试器集成到 SystemC 环境中来支持。这两种方法都可以简化执行多方案测试的自动化,并实现软件的高覆盖率,满足安全关键应用程序的要求。可使用 CEVA 的目标连接服务器 (TCS) 管理器为调试器配置目标。这样就把 CEVA 在硬件调试连接问题和故障的经验进行了封装,并通过图形用户界面简化了对目标选择、连接配置和状态检查的访问。

CEVA 硬件调试配置界面

要求

经验丰富的程序员都知道,在硬件上进行调试是很困难的。CEVA 目标连接服务器 (TCS) 旨在帮助您轻松配置调试目标和首选通信机制。此外,配置界面还可即时指示硬件连接的基本状态或硬件版本不匹配问题,并能够轻松对存储器访问进行限制,以避免因访问不存在的存储器而导致无限等待。

驱动器配置

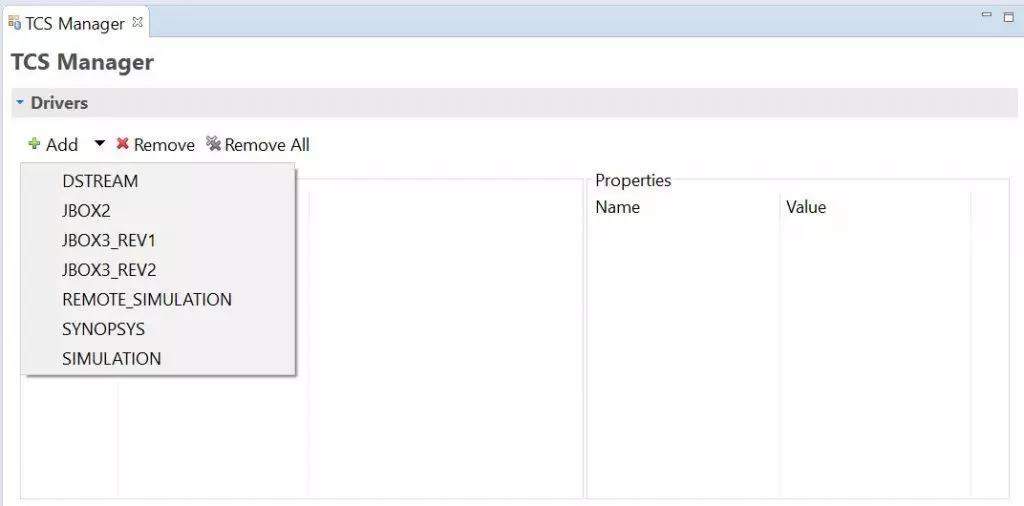

您可以通过设置目标连接服务器的驱动器来选择提供实际硬件连接的组件。调试器所在的机器通过网络连接到驱动器,并且驱动器采用 JTAG 协议与所选硬件进行通信。以下图 4 显示了通过 TCS 接口选择驱动器的过程。

图 4:TCS 驱动器选择菜单

当您选择好驱动器后,还可以直接从同一个界面选择配置选项(图 5)。

图 5:TCS 驱动器配置选项

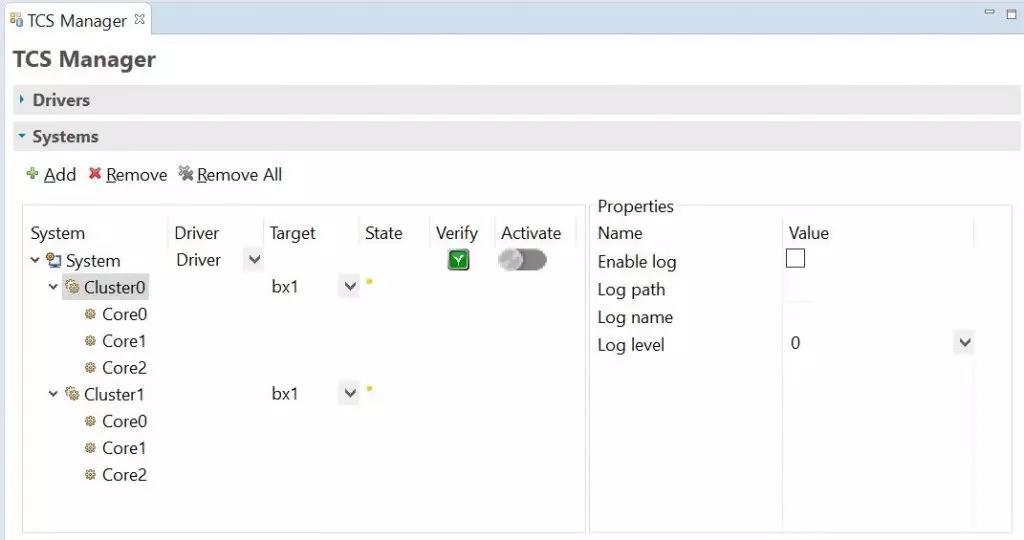

系统设置

在硬件方面,您可以对想要调试的系统组件进行控制。TCS 提供了一种为硬件系统结构中每个组件设置特定配置的机制(图 6)。

图 6:TCS系统描述用户界面

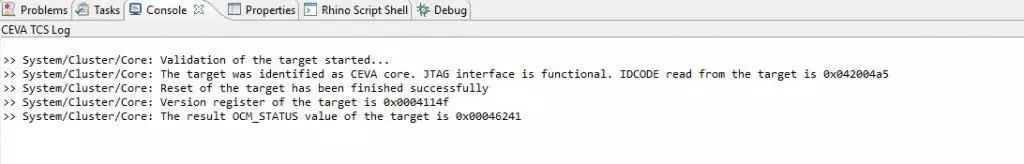

TCS 一个非常重要的功能是当您按下“验证”按钮时,会立即检查系统连接。这样会触发一系列健全性检查器运行基本测试,以确保所有元素准备就绪随时进行成功的连接和有效的调试会话。这样可确保驱动器被实际连接并激活,执行受支持的固件版本,目标硬件被连接并通电,CEVA 处理器的版本与实际硬件相对应,以及更多此类测试顺利进行。运行这些健全性测试有助于避免在初启和调试中浪费大量时间。

图 7:TCS:验证按钮执行结果

您可以通过 TCS 配置其他功能。例如,复杂的问题并不总是表现出明显的硬件漏洞症状。为了帮助隔离这些问题,在 TCS 用户界面(每个集群)中嵌入了一个内置的日志机制,它允许您捕获调试器和驱动器之间的完整通信。在许多情况下,这可以很快帮您找到导致故障的根本原因。

另一个非常有用的配置选项是根据确定的核心群集来定义专用内存屏障。通常,此类核心群集会映射到有限范围的物理存储器中。在这种情况下,可能存在对此群集无效的存储器范围,访问超出范围的存储器位置可能会导致无休止的等待。这些无效的存储器单元会不经意间被触发访问;仅仅滚动存储器视图窗口都可能导致这样的错误。内存屏障有助于防止这些问题,因此,对无效存储器范围的访问请求将被调试器忽略,不会发送给驱动器。

最后,CEVA 调试器提供了许多您熟悉和喜欢的基于 PC 的功能,精心设计可与基于 CEVA 的硬件紧密相连。

总结

我们在本系列文章中回顾了芯片编程和调试所面临的挑战,并列举了 CEVA 通过与硬件平台实现安全有效连接,使得程序员能够采用更加轻松的方法完成工作。CEVA 一直致力于提升您的开发体验,在开发现实生活产品的同时,将用户与我们自身的实践和努力封装在一起。

推荐阅读:

专家解读|硬件调试的复杂性 — 第 1 部分

*此内容为集微网原创,著作权归集微网所有,爱集微,爱原创

【IPO价值观】产品结构单一,环动科技业绩高度依赖埃斯顿

专利申请

专利申请

知识产权质押融资

知识产权质押融资

专利地图分析

专利地图分析

版权登记

版权登记

集成电路布图设计

集成电路布图设计

商标交易

商标交易

商标申请

商标申请

专利交易

专利交易

专利无效

专利无效

热门评论