【专利解密】长鑫存储在堆栈式DRAM中的技术改进

【嘉德点评】长鑫存储买下了奇梦达留下的1000万份关于DRAM技术的文件,其中就包括奇梦达的Buried Wordline堆叠式技术。

动态随机存储器(Dynamic Random Access Memory,DRAM) 是计算机中常用的半导体存储器件,由许多重复的存储单元组成。DRAM 技术其实有沟槽式(Trench Dram)和堆栈式(Stack Dram)两种,虽然堆栈式技术的竞争力相对较好,但是由于早期的市场原因,该技术被搁浅,同时发明Stack Dram的奇梦达 Qimonda 公司也宣布破产。

在当前市场上DRAM主要被韩国的三星、SK海力士以及美国的美光科技等国外公司的垄断,而国内的长鑫存储公司为了突破国外这一封锁线,买下了德国奇梦达 Qimonda早期关于Stack DRAM的1000万份技术文件。

在Stack Dram中随着采用埋入式字线结构的动态随机存储芯片的制程微缩,字线的结构也在不断缩小,同时电子迁移率衰减和饱和速度限制了驱动电流的提高,器件性能的改善变得非常困难。为了解决这一问题,长鑫存储申请一项名为“半导体存储器件结构及其制作方法”的发明专利(申请号:201711440259.8),申请人为长鑫存储技术有限公司。

该发明提供了一种半导体存储器件结构及其制作方法,用于解决现有技术中动态随机存储芯片性能的改善越趋困难的问题。

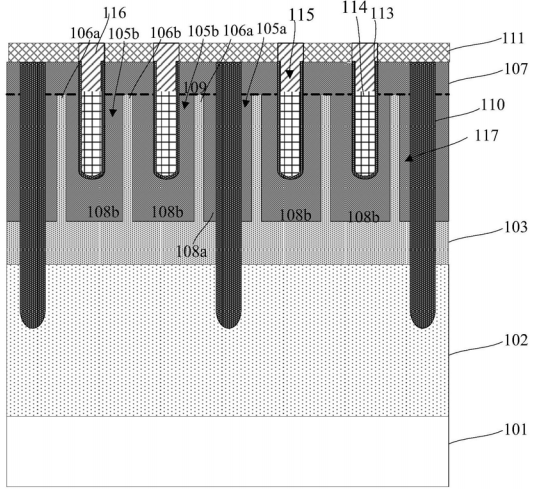

图1

图1是该发明专利中提的一种半导体存储器件结构的,首先我们提供一种硅基底101,它是包含单晶硅衬底(Si)及绝缘体上硅衬底(SOI)所组成群组中的一种,在硅基底101的表面采用外延生产工艺,可以形成锗硅渐变缓冲层102,其厚度介于500纳米~1000纳米之间。在锗硅渐变缓冲层102上是锗硅弛豫层103,为了保证锗硅弛豫层103与后续外延的单晶硅之间具有较大的晶格常数差,从而提高后续制作的埋入式字线结构的沟道应力,并提高器件性能,该层的锗含量会远大于锗硅渐变缓冲层102的锗含量。同样我们也可以用相同的方法在锗硅弛豫层103上形成硅外延层107,然后采用化学机械抛光工艺(CMP)对所述硅外延层107表面进行抛光,以获得平滑表面。

我们采用双重曝光(Double Patterning)、间距倍增(Pitch Doubling)及四重曝光(Quadruple Patterning)组成群组中的一种,用来形成顶层部109中埋入式字线结构的掩膜图案111。

另外,锗硅弛豫层103还包括中央弛豫侧壁106b,其位于两相邻的填充沟槽105b之间,周边弛豫侧壁106a以及中央弛豫侧壁106b也可以为埋入式字线结构的沟道提供应力。

此发明设计的半导体存储器件的结构中,是将两条埋入式字线结构分别设置在锗硅弛豫层填充沟槽内的有源区中,通过这种设计弛豫侧壁会对其内的有源区产生应力,以提高沟道内部电子的迁移率,进而提高器件性能。同时在本发明中还巧妙的设计了锗硅渐变缓冲层及锗硅弛豫层的锗硅比例,可以有效提高锗硅弛豫层的质量,并藉以提高外延硅外延层的生长质量。

长鑫存储在继承了 Stack Dram 优良传统的同时,又提出了新的技术创新和改进,有效克服了现有技术中的种种缺点,并且使该动态随机存储器具高度产业利用价值。

(校对/holly)

*此内容为集微网原创,著作权归集微网所有,爱集微,爱原创

产业观察:Wi-Fi 8在路上

专利申请

专利申请

知识产权质押融资

知识产权质押融资

专利地图分析

专利地图分析

版权登记

版权登记

集成电路布图设计

集成电路布图设计

商标交易

商标交易

商标申请

商标申请

专利交易

专利交易

专利无效

专利无效

热门评论