《集微公开课》第八期笔记:紫光同创详实解读FPGA的DDR实操经验

{{isPaused?'播放中':'播放音频'}}

{{isPaused?'播放中':'播放音频'}}

集微直播间自开播以来获得了大量来自行业的关注与好评。其中“集微公开课”栏目联合行业头部企业,通过线上直播的方式分享精彩主题内容,同时设立直播间文字提问互动环节。集微网希望将“集微公开课”栏目打造成中国ICT产业最专业、优质的线上培训课程,深化产教融合,助力中国ICT产业发展。

4月29日(本周三)上午10点,第八期“集微公开课”邀请到深圳市紫光同创电子有限公司AE技术专家、高级FPGA应用专家黄如尚,带来了以《FPGA开发应用DDR实战指南》为主题的精彩演讲。

FPGA软硬兼施

在国内FPGA阵营中,深圳市紫光同创电子有限公司可谓是国内FPGA的翘楚。紫光同创系紫光国微下属公司,专业从事FPGA、CPLD等可编程逻辑器件的研发与生产销售,致力于为客户提供完善的、具有自主知识产权的可编程逻辑器件平台和系统解决方案。

紫光同创注册资本4亿元,总投资超过15亿元,是国家高新技术企业,拥有高中低端全系列产品,产品覆盖通信、网络安全、工业控制、视频监控、汽车电子、消费电子、数据中心等应用领域。

紫光同创立足中国大陆,总部设在深圳,拥有上海、北京、成都等分公司,公司人数超过450人、研发人员占比超过85%,拥有专利近200项、核心专利占比超过85%。在产品布局和研发方面处于领先水平。

黄如尚介绍,紫光同创的FPGA产品主要有三大类:Compact系列为CPLD产品,主打低成本低功耗;Logos系列FPGA拥有高性价比;高端的Titan系列FPGA是中国第一款自主知识产权千万门级高性能FPGA。这三大类产品覆盖了高中低端的市场需求,广泛应用于通信、工业控制、视频监控、汽车电子、消费电子等领域。

除FPGA器件性能之外,配套软件也至关重要。黄如尚着重说,紫光同创历经10多年研发锤炼,已突破大规模 FPGA 全套软件的核心研发技术,提供了全套自主配套的Pango Design Suite开发套件。这一套件集成了从设计输入、综合、后端布局布线到位流下载的全流程。同时还提供了DebugCore在线调试工具、后端手动布局布线工具、时序分析工具、功耗分析工具以及IP核生成器,包括常用的一些基础IP如FIFO、PLL、APM等IP和系统级IP如HSST、以太网、DDR等IP。PDS软件具有运行速度快、时序收敛性能较好、操作简单易用等特点。

探秘DDR工作原理

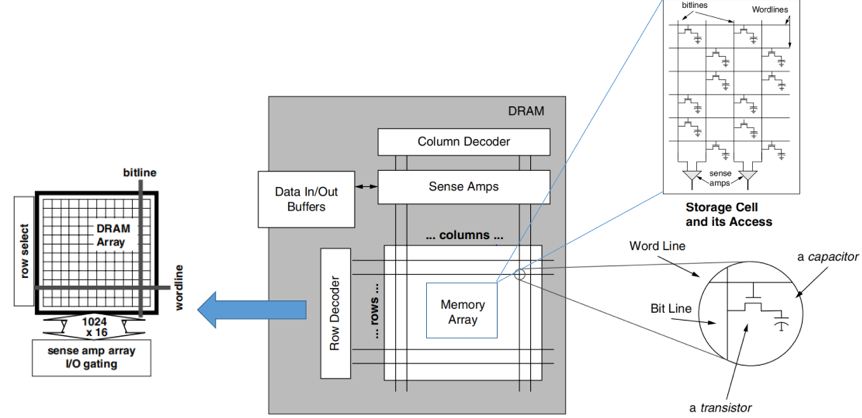

SDRAM内存广泛应用于现代数字系统中,具有低成本、容量大、访问速度快等特点。SDRAM的存储核心为若干个表格式阵列、使用行、列、BANK地址寻址。SDRAM的基本存储单元非常简单,仅由一个电容和一个晶体管组成,主要利用电容的电荷存储能力实现数据的存储,利用晶体管实现不同存储单元的选通,具有低成本、容量大等特点。然而这种简单的结构却带来了诸多使用上的限制,其读写操作也变得比较复杂。

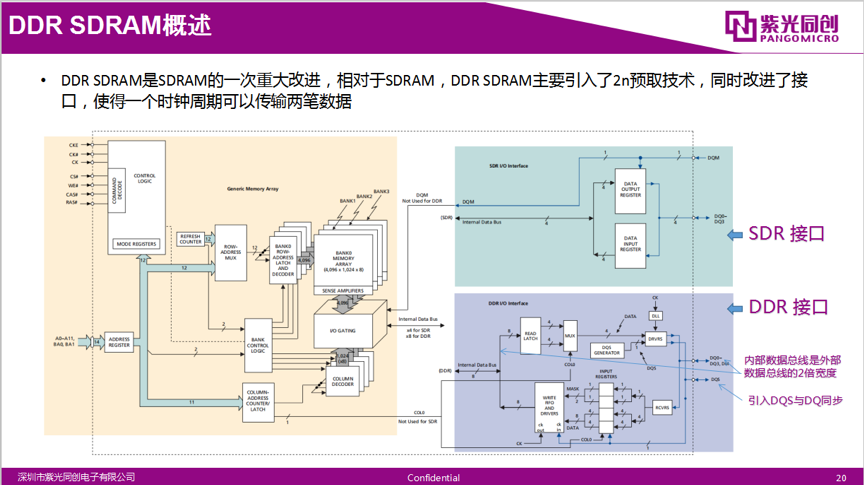

DDR SDRAM即双倍速率同步动态随机存储器,简称DDR。相对于前代的SDR (Single Date Rate)SDRAM,DDR内存在一个时钟周期内传输两次数据,它能够在时钟的上升沿和下降沿各触发一次数据传输,因此称为双倍速率同步动态随机存储器。DDR内存可以在与SDRAM相同的总线频率下达到更高的数据传输率。

对于FPGA的设计而言,DDR接口作为FPGA一个非常重要的子系统,是大多数FPGA应用工程师所必须掌握的。同时,随着DDR接口速率的不断提升,如何实现高可靠性设计成了新的挑战。

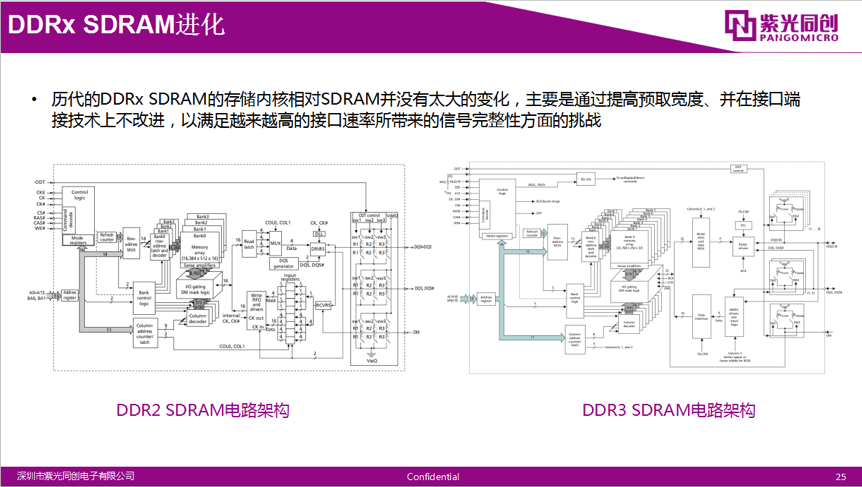

黄如尚指出,历代DDR SDRAM和前代的SDR SDRAM的架构都基本相同,基本由时钟电路、命令控制逻辑、存储阵列、行列地址逻辑、刷新计数器、I/O电路等主要部分构成。而DDR内存的每一次更新换代,主要都是围绕提升I/O电路的性能进行。

黄如尚以从SDR SDRAM演进到DDR SDRAM为例,举例说明了如何通过引入差分时钟、2n预取技术、双向DQS同步以及引入SSTL电平标准等方式,实现从SDR到DDR的跨越式升级。

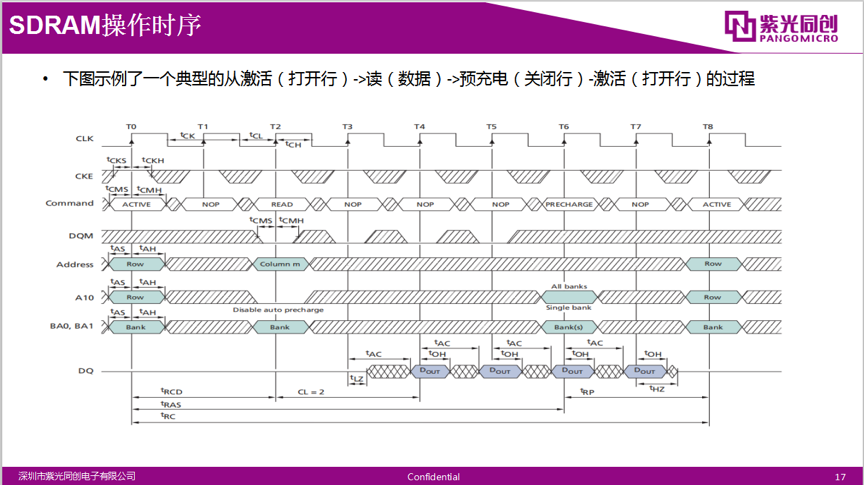

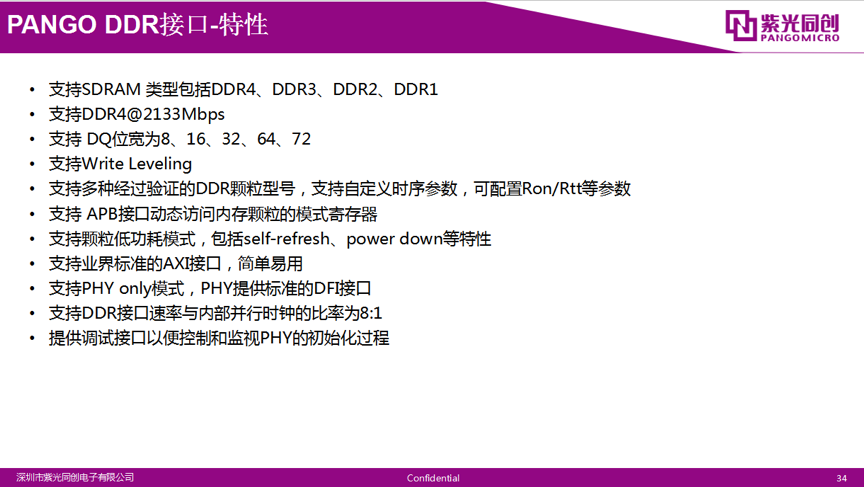

在介绍了DDR的存储原理、基本命令术语、访问流程之后,黄如尚示例了DDR典型的读写时序图。同时他也指出,不必对DDR复杂的操作时序望而生畏,紫光同创的DDR IP已经帮用户屏蔽掉了这些复杂的接口命令、操作时序以及读写校准过程,面向用户提供了一个业界标准的AXI接口,用户只需要掌握AXI接口的应用方法就可以实现内存颗粒的访问。

紫光同创DDR接口方案优势显著

提及紫光同创的DDR接口方案,黄如尚介绍说,紫光同创的FPGA提供软核或硬核DDR控制器IP,其中软核控制器由DDRC和DDRPHY两个独立的部分组成,DDRC与DDR PHY通过标准的DFI接口连接;支持PHY only模式,用户可以使用自行定制的DDRC;DDR PHY由底层的专用硬件单元和软逻辑构成,专用的硬件单元保证了PHY的性能;使用软核的方式管脚分配更灵活,可以支持多个控制器。

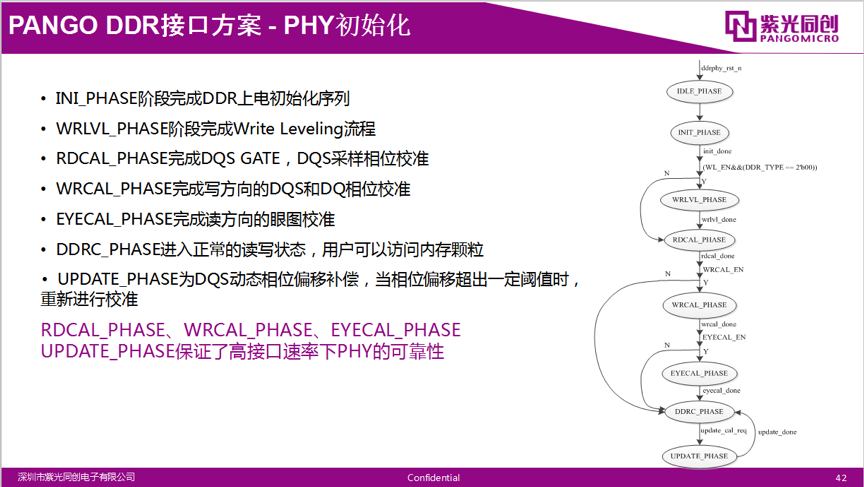

紫光同创的DDR PHY层包含了不少亮点,其包含DQSL、DLL等DDR专用底层单元,可实现DQS GATE、高精度的DQS相位调节等功能。黄如尚在详细解读PHY工作流程时指出,PHY初始化过程中RDCAL_PHASE(读校准)、WRCAL_PHASE(写校准)、EYECAL_PHASE(眼图校准)、UPDATE_PHASE(动态校准)等流程保证了高接口速率下PHY接口工作的可靠性。

在时钟方面,黄如尚指出,紫光同创的每个I/O BANK包含了一个PPLL,从而可为ISERDES、OSERDES提供高速、低偏斜的I/O时钟。在写方向,OSERDES工作在SDR模式,避免了在DDR模式下时钟占空比变化造成的影响。在读方向,一次传输周期的上升数据和下降沿数据,分别使用DQS和DQS#的上升沿采样,同时分别进行采样校准,避免了DQS占空比失真的影响。

总结来看,除了PHY的创新电路架构和初始化流程上的可靠性设计保证了高速率和高可靠性得以兼顾之外,黄如尚认为紫光同创的DDR控制器也有一些独到之处,保证了访问效率。一是针对刷新影响效率的问题,紫光同创的控制器具有较好的刷新管理算法,会根据接口流量的变化选择在空闲的时候进行刷新而不是机械地按周期刷新,有利于提升带宽;二是具有比较优秀的BANK管理算法,能够尽可能屏蔽掉行地址频繁切换所引起的效率损失;三是具有命令排序功能,可以灵活地调整读写命令的顺序,以消除读写频繁切换带来的效率损失。从这些方面来看,紫光同创在性能指标、访问效率、使用灵活性上有优势。

对于未来的挑战,黄如尚指出,随着DDR接口速率不断提升,需要FPGA厂商不断地提升I/O技术,同时需要在优化访问效率上继续做文章。对于应用工程师,除了掌握DDR接口的应用方法之外,还建议学习一些信号完整性方面的知识。

深圳市紫光同创电子有限公司:

电话:86-755-66886188

地址:深圳市南山区高新技术产业园高新南一道15号

邮箱:marketing@pangomicro.com

网址:www.pangomicro.com

集微直播间自开创以来获得了大量来自行业的关注与好评。5月7日-9日(周四-周六)上午10:00,集微开讲、集微公开课轮番上阵,让你过足瘾!

如果想与爱集微平台合作,或是了解相关活动问题,皆可与集微网徐伦联系(微信/电话同15021761190)。

(校对/Yuna)

*此内容为集微网原创,著作权归集微网所有,爱集微,爱原创

【个股价值观】新洁能:四大平台功率全系覆盖,车规应用提振业绩回暖

专利申请

专利申请

知识产权质押融资

知识产权质押融资

专利地图分析

专利地图分析

版权登记

版权登记

集成电路布图设计

集成电路布图设计

商标交易

商标交易

商标申请

商标申请

专利交易

专利交易

专利无效

专利无效

热门评论