集成电路布图设计登记的布局策略——你所不知道的集成电路布图设计登记

1月25日,国家知识产权局发布数据,在2020年我国集成电路布图设计发证11727件,同比增长77.3%,提交申请集成电路布图设计登记的企业数量达到5600余家,超过上年数量的2倍。集成电路布图设计登记应该采用什么样的策略进行布局呢?

在国内,作为解决卡脖子领域的重点行业,再加之近来作为热点话题的知识产权,因此集成电路相关的知识产权问题尤为活跃。如笔者前文(商业秘密还是专利?以存储芯片为例讲述芯片知识产权布局策略)所述,除了专利、技术秘密之外,集成电路布图设计登记作为集成电路特有的知识产权保护方式,在国内愈来愈受到关注。

此消彼长的集成电路布图设计登记

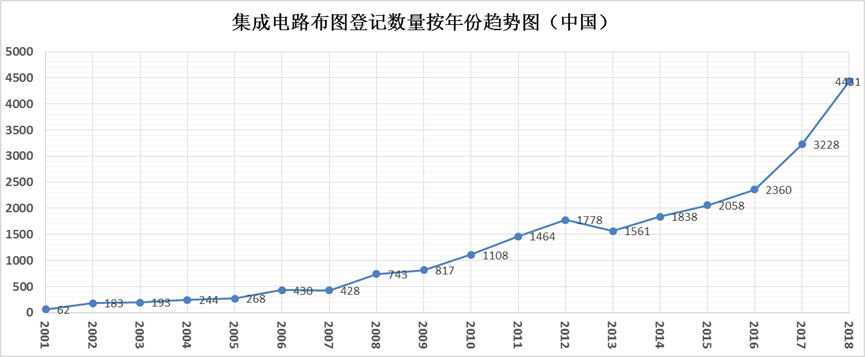

如下图1是2001年以来国内集成电路布图设计登记申请数量的趋势图。可以看出申请数量基本上是逐年递增,尤其是2016年之后急剧上升。

图1

根据2020年的数据,我国2019年集成电路布图设计登记申请8319件,跟2018年的4431件相比又大幅度提升了87.7%!而在1月25日,国家知识产权局发布数据显示,在2020年,我国集成电路布图设计发证11727件,同比增长77.3%,提交申请集成电路布图设计登记的企业数量达到5600余家,超过上年数量的2倍!

但是对于产业相对成熟的国家,集成电路布图设计登记的情况又是何种状况呢?如下图2是美国和日本的集成电路布图设计登记申请数量的趋势图。可以发现美日的情况与国内大相径庭。自上世纪90年底末甚至更早,美日的集成电路布图设计登记申请数量就逐渐下降,在2010年之后日本的数量甚至下降为个位数,美国也逐步下降为小几十件左右。

图2

EDA工具的大规模应用,难以再产生布图的艺术

造成上述现象的原因究竟是何?其实可以从技术和知识产权角度进行分析,即可略窥一二。

正如前面所述,从技术角度看,随着技术的发展芯片集成度越来越高,越来越多的功能和器件被集成到一个芯片中,集成电路版图的设计更多的趋向于采用计算机辅助工具(EDA工具)进行的自动布局布线(APR)设计,尤其是渐成主流的数字电路更是如此。既然是机器自动设计,就很难再称之为“艺术”;即使是更可能被认为是“艺术”的模拟电路,也逐渐掺杂了更多的数字电路,逐步趋向于数模混合电路或芯片,以至于模拟集成电路的自动布局布线设计成为业内更多探讨的热点和方向。

对于知识产权而言,最重要的特点是能够有效的保护所有人的权利,同时少则几千万多则上百亿的器件集成到一个芯片中,这么巨大规模的版图设计难体现出“艺术”的一面,很难简单有效的判断是否被侵权,因此通过集成电路布图设计登记很难进行有效的保护和维权。

笔者查阅了近几年的《最高人民法院知识产权案件年度报告》发现,最高人民法院知识产权庭每年接收的案件已超过千件,但是涉及到集成电路布图设计相关的案件,每年仅为寥寥几件,某些年度甚至没有。集成电路布图设计诉讼案件的数量的稀缺从侧面或许反映出了集成电路布图设计登记的对于所有人保护的困难。从一些典型的案例(比如14年上海知识产权十大典型案件中集成布图设计案例)中可以看出,即使进入诉讼程序,侵权判定过程也需要涉及非常繁杂专业知识的认定和论证过程。可见集成电路布图设计登记的保护和维权相当之困难。这也间接说明产业相对成熟的国家美日等国集成电路布图设计登记越来越少的原因;而国内与之相反,或许恰恰说明国内的芯片产业处于蓄势待发迎头追赶的阶段。

集成电路布图设计登记的四大处理策略

既然如前面讲到对于集成电路布图设计登记所有人的权利保障很困难,存在着众多的困境,是不是就说明集成电路布图设计登记就没有意义了?对于此的回答当然是否定的。只不过为了更好的发挥集成电路布图设计登记的作用,只不过在进行登记申请时需要进行必要的策略和方式。

下面结合笔者的芯片研发设计经验及其知识产权的工作体会,谈一下对于上述困境的一些应对策略。

首先,注重局部保护

现如今的芯片规模变的越来越大,所包含的器件和功能越来越多,通过对芯片的整体布局(Floor Plan)进行布图设计的申请保护是非常困难的。所以应该注重局部保护,即对能够体现电路功能和独创性设计的模块区域进行单独或重点保护。

正如《集成电路布图设计保护条例》所规定的“受保护的布图设计应当具有独创性,即该布图设计是创作者自己的智力劳动成果,并且在其创作时该布图设计在布图设计创作者和集成电路制造者中不是公认的常规设计”。

对芯片中的重点模块区域进行保护,既能保护芯片布图设计中的关键模块,又能在侵权判断时容易取证和做出认定。当然,如果是面积和规模很小的芯片,例如简单功能的模拟电路还是应当可以把整个芯片进行布图设计保护。

其次,运用结合保护

这里所说的结合保护,是指依据所设计的集成电路布图的创新改进部分的特点,灵活的将集成电路布图设计登记和发明或实用新型专利。比如某些更小范围的局部布局、单个或简单器件的组合布局等,这些更适合结合保护。因为专利的格式内容形式(权利要求描述的方式、说明书的解释说明等)集成电路这样多层结构的布图形式不一定能很清楚的界定和保护;而集成电路布图设计登记能够很好的利用图形备案能够相对准确的界定相应的图形结构。例如DRAM存储器存储阵列中的字线结构(开放字线Open-bitline,折叠字线Folded-bitline)、NAND flash存储器中三维存储单元的结构、带隙基准电压模块中产生负温度系数电压的PN结布局结构等。需要说明的是,这样的简单器件的组合布局的创造性往往不高,所以通过结合实用新型专利保护或许更合适。

例如2018年国知局发布的专利复审无效十大案件之苹果-高通系列发明专利权无效宣告请求案中,高通的专利“ZL201480013124.1具有高密度的局部互连结构的电路及其制造方法”涉及深亚微米工艺节点中集成电路多层金属互连结构。这个专利就是简单器件组合布局的改进,如果能够这个专利同时申请集成电路布图设计登记的话,对于这个技术的权利所有人(高通)来说,应该会起到更加严密和完善的保护作用。

再次,适当性登记

因为集成电路布图设计登记在申请时需要提供芯片版图的不同层的图案图片。而这些层的图案最终都是会被制作成相应的掩膜版(Mask),再由光刻机通过这些掩膜版对硅片进行加工最终制造芯片的关键信息。而在上述申请时还需要对不同层进行工艺的说明和介绍。这些信息一定程度上又是各大芯片厂商(比如台积电、三星、中芯国际等)的关键技术信息。这些信息的提供就有可能存在技术秘密泄露的风险。所以为了既能合理进行集成电路布图设计登记的申请保护,又能避免技术秘密泄露的风险,可以在不同层的提供上进行取舍。

比如:这些层大致可以分为连线结构层、器件结构层、器件调节层。连线结构层和器件结构层主要是在芯片中形成各种金属层的连线结构和器件的形状结构;器件调节层主要是进行各种离子杂质的注入和生长,目的是为了调节器件的各种参数,比如MOS管的不同阈值电压、电阻电容的性能参数等。对于后者(器件调节层)在芯片制造完成后是很难观察到的,也就是说它对于侵权判定是没有什么用处的,所以说在进行集成电路布图设计登记的申请时,这些在芯片中不能体现在结构中且很难观察到的层,就可以不必要提供。这样既不影响侵权的判定又能避免技术秘密泄露。

最后,侵权判定

对于集成电路布图设计来说,判断侵权是非常困难的。很多时候在面积巨大、数目庞杂的芯片中寻找侵权的证据无异于大海捞针。除了对芯片的研发人员、公司、项目等人为因素做更多的背景调查外,还应该从芯片的功能、参数、特性等多比对分析。同时,因为集成电路布图设计的侵权分析技术门槛很高,也因此催生出很多专门的知识产权分析鉴定服务机构(比如因IPO而被人关注的芯愿景),它们会利用专门的仪器设备以及专门的人员进行相应的布图设计侵权分析等。

总之,集成电路布图设计登记,作为芯片领域特有的知识产权类型,需要结合实际特点进行灵活多样的处理,才能更好的保护创新、保护技术进步。

作为我国亟待发展的卡脖子产业,芯片领域还有太多的工作要做,知识产权是必不可少的一环。虽然在这个领域我们还备受“欺凌”,但是努力掌握合适的知识产权规则,增加知识产权质量水平,必定会事半功倍的提升我国在芯片产业的话语权。

*此内容为集微网原创,著作权归集微网所有,爱集微,爱原创

“群舟结阵来,AI舞芯潮”,2026半导体投资年会在沪圆满举行

专利申请

专利申请

知识产权质押融资

知识产权质押融资

专利地图分析

专利地图分析

版权登记

版权登记

集成电路布图设计

集成电路布图设计

商标交易

商标交易

商标申请

商标申请

专利交易

专利交易

专利无效

专利无效

热门评论