【专利解密】杰发科技新专利改善低压差分信号发送器的时钟偏移

【嘉德点评】杰发科技发明的低压差分信号发送器,该方案利用物理层芯片进行信号的处理以及输出,使得串行低压差分的数据信号与串行低压差分的时钟信号的相位差满足要求,保证了数据信号与时钟信号的同步,改善了时钟偏移。

四维图新日前发布公告称,公司全资子公司合肥杰发科技有限公司获得了一项美国专利商标局颁发的发明专利证书,该专利中的方案有效提高了杰发科技在车载 低压差分信号(LVDS)接口数据传输质量和采样准确率的技术壁垒。

目前,由于低压差分信号可以减少电磁辐射以及提高抗干扰能力,串行可以节省信号线,因此,车辆所用液晶显示屏(LCD)的接口以LVDS接口为主。

现有技术中,利用两个锁相环(PLL)来实现LVDS接口,其分别利用系统PLL和端口物理层芯片(Phy)的内部PLL来产生时钟信号,像素时钟信号需经过内部PLL的处理,而数据信号经过Phy芯片中的并行输入串行输出模块处理,因而数据信号与像素时钟信号经过的路径不同。

这样的设计方案就使得输出的时钟信号和数据信号之间容易有相位差,在同步对齐性方面有所欠佳,主要体现在时钟偏移参数比较差,尤其是双链路,且由于同步性差致使展频后的时钟信号的跟随能力受限。

因此,杰发科技在2019年5月8日申请了一项名为“一种低压差分信号发送器以及数据传输设备”的发明专利(申请号:201910381532.7),申请人为合肥杰发科技有限公司。

根据该专利目前公开的相关资料,让我们一起来看看这项低压差分信号发送器方案吧。

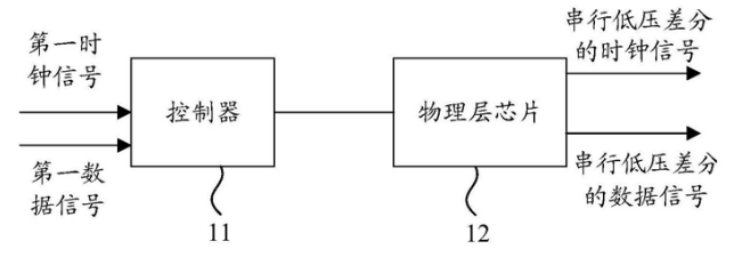

如上图,为该专利中发明的低压差分信号发送器的结构示意图,该发送器主要包括控制器11和物理层芯片12,控制器用于接收第一时钟信号,并对第一时钟信号进行处理以得到第二时钟信号,在第二时钟信号的驱动下读取第一数据信号,并输出第三时钟信号和第二时钟信号。

物理层芯片与控制器连接,用于接收第一时钟信号以及控制器输出的信号,并利用第一时钟信号对第三时钟信号和第二数据信号进行采样处理,输出串行低压差分的时钟信号和数据信号,并且二者信号的相位差会控制在预设的范围之内。

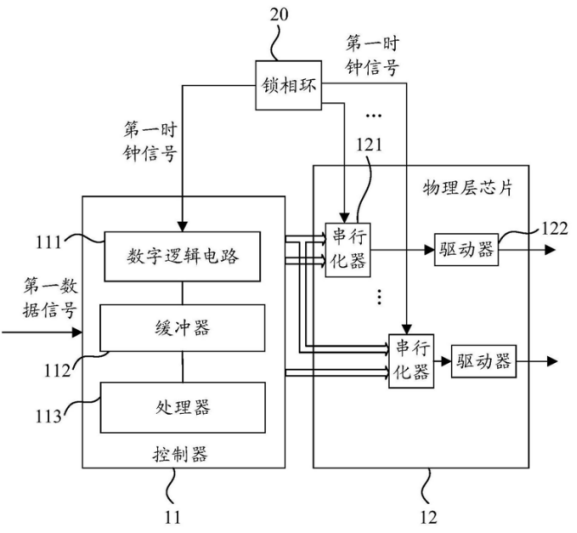

其后,该方案利用一个锁相环产生时钟信号,将控制器输出的第三时钟信号当做一路特殊的数据被采样输出,在第一时钟信号的驱动下利用物理层芯片对控制器输出的第三时钟和第二数据信号进行处理,以保证数据信号与时钟信号的同步性以及提升时钟偏移指标,具体的低压差分信号发送器如下图所示。

如上图,第一时钟信号为采样时钟信号,可以对预设时钟信号进行展频处理;第二时钟信号为像素时钟信号;第三时钟信号和串行低压差分的时钟信号的频率相同且占空比相同,其信号为常量时钟串,对于单链路而言,需要一路常量时钟串,而对于多链路而言,就需要多路常量时钟串。

第一数据信号为外部图形处理器输出的信号,包括RGB三个通道的数据信号,例如,控制器可以对前级的图形处理器输出的RGB数据集进行映射处理以满足LVDS格式的要求,还可以实现信号线交换等调试功能。

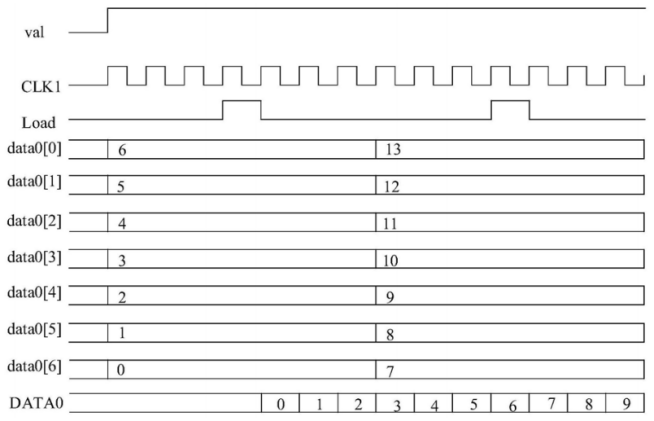

如上图,为该电路对应的时序示意图,像素时钟信号CLK用于控制器内部的缓冲器,从前端图形处理器中读取第一数据信号,在缓冲器存储有第一数据信号时,有效输出信号val为高电平。

在有效输出信号val为高电平,且一个像素时钟内数据已稳定了3个采样时钟周期,加载信号Load被拉高并持续一个采样时钟周期,这样以后每一个像素时钟周期内都会有一个加载信号Load的下降沿,可用于锁存并行数据。

以上就是杰发科技发明的低压差分信号发送器,该方案利用物理层芯片进行信号的处理以及输出,使得串行低压差分的数据信号与串行低压差分的时钟信号的相位差满足要求,保证了数据信号与时钟信号的同步,改善了时钟偏移。由于仅使用了一个锁相环来产生时钟信号,因此还可以简化整体方案的设计,节省了硬件资源的成本。

关于嘉勤

深圳市嘉勤知识产权服务有限公司由曾在华为等世界500强企业工作多年的知识产权专家、律师、专利代理人组成,熟悉中欧美知识产权法律理论和实务,在全球知识产权申请、布局、诉讼、许可谈判、交易、运营、标准专利协同创造、专利池建设、展会知识产权、跨境电商知识产权、知识产权海关保护等方面拥有丰富的经验。

(校对/holly)

*此内容为集微网原创,著作权归集微网所有,爱集微,爱原创

沪上盛典!2025半导体投资联盟年会 34大奖项+30份榜单揭晓

专利申请

专利申请

知识产权质押融资

知识产权质押融资

专利地图分析

专利地图分析

版权登记

版权登记

集成电路布图设计

集成电路布图设计

商标交易

商标交易

商标申请

商标申请

专利交易

专利交易

专利无效

专利无效

热门评论