【提升】国产EDA助力复杂软硬件协同验证效率提升;大规模留抵退税政策实施后,首月8015亿落地;中国科学技术大学未来技术学院揭牌

1、运行速度提高5倍以上 国产EDA助力复杂软硬件协同验证效率提升

2、大规模留抵退税政策实施后,首月8015亿元“落地”

3、潘建伟院士担任院长,中国科学技术大学未来技术学院揭牌

4、两院士领衔揭榜“岷山行动”计划项目,微电子先进封测方向揭榜项目已获融资

5、概伦电子与北京大学共建的EDA创新联合实验室揭牌

6、5月第一周上海进出境货机航次明显增长,集成电路供应链稳步恢复

7、建设方案获通过,安徽大学牵头的重要集成电路研究院迎新进展

1、运行速度提高5倍以上 国产EDA助力复杂软硬件协同验证效率提升

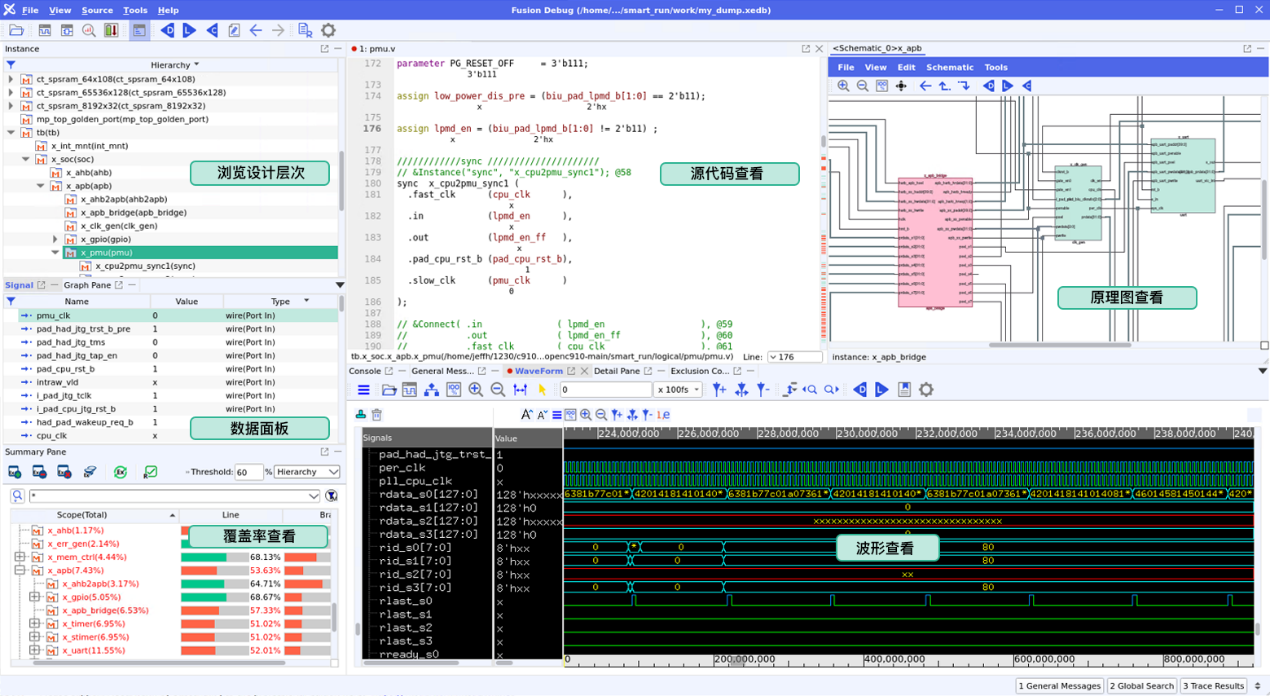

2022年5月11日,EDA(集成电路设计工具)智能软件和系统领先企业芯华章正式发布基于创新架构的数字验证调试系统——昭晓Fusion DebugTM 。该系统基于芯华章自主开发的调试数据库和开放接口,可兼容产业现有解决方案,提供完善的生态支持,并具备易用性、高性能等特点,能够帮助工程师简化困难的调试任务,有效解决难度不断上升的设计和验证挑战。

在芯华章研讨会暨产品发布会上,芯华章科技软件研发总监黄世杰详细介绍了昭晓Fusion DebugTM产品的完整解决方案,并且用实际项目演示了工具的典型应用场景。合肥市微电子研究院院长陈军宁、电子科技大学电子科学与工程学院副教授黄乐天、中兴微电子有线系统部部长贺志强、平头哥上海半导体技术IP验证及软硬协同验证负责人张天放、燧原科技资深架构师鲍敏祺等行业专家与学者也受邀出席,共话半导体产业发展及验证EDA技术趋势。

谈及前端验证面临的挑战时,鲍敏祺表示:“一方面芯片验证场景日益复杂,从单纯的功能验证到今天面对整个系统级、场景级的验证;另一方面,面对激烈的市场竞争,芯片集成规模不断扩大,研发周期却不断缩短,验证的重要性日益突出。”

据了解,在典型的SoC芯片研发项目中,工程师通常需要花费四成左右的时间进行调试,工程复杂且费时费力。好的调试系统不仅可以确保项目的成功,更可以有效提高SoC芯片的设计和验证效率,降低芯片设计成本。

作为国内率先发布的数字验证调试系统,昭晓Fusion DebugTM 的发布填补了多项国产技术空白。相比于国际主流数字波形格式,芯华章的昭晓Fusion Debug TM 采用完全自研的高性能数字波形格式XEDB。该波形格式借助创新的数据格式和架构,具备高性能、高容量、高波形压缩比等特点,其提供的高效编码和压缩方案,在实际测试中可以带来比国际主流数字波形格式超8倍的压缩率。与其它商业波形格式相比,XEDB的读写速度快至3倍,并支持分布式架构,可充分利用多台机器的物理资源来提升整体系统的性能,实测中表现出的波形写入速度可以比单机模式提高5倍以上,这对复杂的软硬件协同验证与调试至关重要。

在提供完整调试解决方案的同时,昭晓Fusion DebugTM由创新的设计推理引擎和高性能分析引擎提供动力,能够支持统一且高性能的编译,快速加载仿真结果和信号显示,轻松进行信号连接跟踪和根本原因分析。根据实际项目数据显示,在完整的设计及原理图模块化加载中,昭晓Fusion Debug TM 的速度比其他商用EDA工具快至5倍,能满足大规模SoC 设计调试的需求,并大大提高了验证效率,从而加速芯片设计创新。

Fusion DebugTM GUI界面

除了性能与效率上的突破,芯华章昭晓Fusion DebugTM 还针对行业实践痛点,提供了不同于一般调试工具的创新解决方案。

“在实际应用中,各个芯片的产品调试特征不同,对调试会产生非常多样化的细分需求。”张天放在谈到一般调试工具在应用中的挑战时表示,“我们希望能够在国产EDA工具里面看到一些开放的接口,便于进行二次开发。”

对此,芯华章科技首席市场战略官谢仲辉表示,“昭晓Fusion DebugTM提供丰富、可编程的数据接口,让用户可针对不同调试场景进行定制化,并能贯通芯华章智V验证平台及支持用户现有的EDA工具,为用户带来更加客户一体化的调试解决方案,从而提供更加普惠的生态支持和用户体验。”

近年来,芯片设计的规模越来越大,摩尔定律逐渐走向极限,芯片验证的难度也随之提高。在谈到下一代设计验证工具时,陈军宁与黄乐天均从不同角度指出,下一代EDA工具需要增强工具间的融合以及更智能化,在减少人力投入的同时,进一步充分利用机器学习、云计算等创新技术,从而提高芯片验证与设计效率。

贺志强也表示:“国产EDA公司拥有高技术起点和贴近本地市场的优势,能够基于客户的痛点进行开发,将经验与解决方案集成到工具当中。作为国产 IC企业,中兴是国产EDA工具天然的天使用户,我们会全力支持国产EDA的发展。”

芯华章科技研发副总裁林扬淳表示:“昭晓Fusion Debug TM融合了先进的机器学习框架,带来更高的验证效率和更智能化的操作体验,致力于解决当前产业调试方案缺乏创新、数据库碎片化以及性能局限等多重挑战,让芯片设计更简单、更高效。”

2、大规模留抵退税政策实施后,首月8015亿元“落地”

5月10日,财政部、税务总局、人民银行三部门联合举行的留抵退税新闻发布会。

图片来源:国家税务总局

发布会上介绍,今年4月1日起实施的大规模留抵退税政策,首月全国已有8015亿元增值税留抵退税款退到145.2万户纳税人账户上,再加上一季度继续实施的此前出台的留抵退税老政策退税1233亿元,1-4月共有9248亿元退税款退到纳税人账户上,助企纾困的政策效应已经开始显现。

从数据来看,小微企业和制造业受益最为明显。今年实施的大规模增值税留抵退税政策,除了“两聚焦”(聚焦小微企业和制造业)之外,还有“三加力”。

国家税务总局党委委员、副局长王道树介绍,一是在扩大范围上加力。进一步退还存量留抵税额,对小微企业和制造业等六个行业,不仅允许其退还增量留抵税额,而且允许其退还存量留抵税额。二是在提高比例上加力。将小微企业和制造业等六个行业增量留抵税额退还比例由60%提高到100%,和先进制造业保持一致。三是在加快频次上加力。对所有小微企业和制造业等六个行业纳税人均按月退还增量留抵税额,比照先进制造业,取消“连续6个月增量留抵税额均大于零,且第6个月增量留抵税额不低于50万元”的限制条件。

财政部预算司司长王建凡表示,财政部多渠道筹措资金,制定实施支持基层落实减税降费和重点民生等转移支付政策,加大对地方特别是基层财力支持。其中,安排专项资金1.2万亿元,支持地方落实留抵退税政策,保障县区财政平稳运行。

人民银行国库局局长董化杰介绍,人民银行靠前发力,根据退税进度,加快向中央财政上缴利润的节奏,2022年以来,已累计上缴结存利润8000亿元,全年上缴利润将超1.1万亿元,直接增强财政可用财力,进一步激发微观主体活力。

3、潘建伟院士担任院长,中国科学技术大学未来技术学院揭牌

5月7日,中国科学技术大学未来技术学院揭牌仪式举行。

图源:中国科学技术大学

仪式上,未来技术学院执行院长、合肥微尺度物质科学国家研究中心主任罗毅介绍未来技术学院概况。中国科学技术大学校长包信和,常务副校长、未来技术学院院长潘建伟为未来技术学院揭牌。

包信和表示,当今,以量子计算、量子通信、量子精密测量等为代表的量子科技,已成为世界瞩目的新兴战略技术焦点,未来技术学院要培养一批推动量子科技浪潮的世界级弄潮儿。期待未来技术学院早日产出高质量的教学科研成果,培养出引领未来技术发展的顶尖人才,为建设中国特色、科大风格的世界一流大学做出重要贡献。

据悉,2021年,教育部公布首批未来技术学院名单,涉及北京大学、清华大学、天津大学、哈尔滨工业大学、上海交通大学、东南大学、中国科学技术大学、华中科技大学、华南理工大学和西安交通大学等12所高校。

4、两院士领衔揭榜“岷山行动”计划项目,微电子先进封测方向揭榜项目已获融资

5月10日,成都高新区发布“岷山行动”计划第二批揭榜项目,包括电磁环境适应、柔性电子、智能传感、生物芯片、新航电等5个方向新型研发机构,高新区将给予揭榜团队产业扶持资金约4.4亿元。

其中,电磁环境适应技术方向由中国工程院院士、北京航空航天大学苏东林教授牵头;柔性电子技术方向由中国科学院院士、南京邮电大学黄维教授任技术咨询专家,有机电子与信息显示国家重点实验室执行副主任赖文勇教授领衔实施;智能传感技术方向由国家智能传感器创新中心副总裁郑政博士牵头,项目依托国家智能传感器创新中心在工信部指导下成立,已打造出一条全球领先、国内唯一的12英寸智能传感器中试线;生物芯片技术方向由重庆大学教授刘雳宇与华西精准医学中心副主任胡文闯联合牵头,主要依托国家精准医学产业创新中心,联动开展科技创新。

同时,第三批20个需求榜单发布,涉及信息存储、脑科学、核酸药物、工业软件、前沿储能、量子计算等多个新兴领域及未来产业,邀请海内外顶尖团队“揭榜挂帅”。

2021年1月,成都高新区启动实施“岷山行动”计划,计划5年投入300亿元建设50个新型研发机构。“岷山行动”计划实施一年多来,首批揭榜项目已聚集产业专家、技术专家等各类人才189人,其中全职人员63人,微电子先进封测方向揭榜项目已获得数千万元融资,功率半导体、细胞工程、医疗手术机器人3个方向揭榜项目正在抓紧融资对接,预计年内融资将超亿元。

图片来源:成都高新区

功率半导体揭榜团队负责人白杰先表示,在“岷山行动”计划政策支持下,已聚集30位全职人员、20位兼职人员,其中研发人才占比超过75%,正在申报及撰写知识产权数量达到11个,有望上半年实现首轮融资。

5、概伦电子与北京大学共建的EDA创新联合实验室揭牌

5月11日,概伦电子与北京大学共建的EDA创新联合实验室揭牌。依托EDA创新联合实验室平台,双方将聚焦设计-工艺协同优化(Design-Technology Co-Optimization,简称DTCO)和DTCO驱动的定制电路设计流程/方法学(DTCO-enabled Custom Design Flow/Methodology)等相关EDA领域。

据悉,2022年4月概伦电子与北京大学签署合作协议,双方共建EDA创新联合实验室,将贯彻落实国家产教融合的方针,结合双方的产业优势与科研实力,促进EDA技术创新发展和推动国产EDA全流程解决方案的建设和推广,培养更多高精尖的产业人才。

北京大学集成电路学院院长蔡一茂表示,成立EDA创新联合实验室,能够将学术界与产业界进一步紧密连接,基于底层创新产出更多科研成果,在推动EDA生态建设的同时培养更多优秀的专业人才。

6、5月第一周上海进出境货机航次明显增长,集成电路供应链稳步恢复

据文汇报报道,5月第一周上海浦东机场海关已累计监管进出境货机共计731架次,环比增长36.4%。

报道称,浦东机场海关为保障长三角地区集成电路等重点产业生产运转,专门开辟了绿色通道,确保最短时间验放通关。

保税区内的近铁国际物流(中国)有限公司的半导体全球分拨中心负责人表示,其进口的集成电路物料“整个审批验放过程相当快捷”,据介绍,3月28日以来,近铁国际一二线出入区货物已达4151票、4.5万箱。

7、建设方案获通过,安徽大学牵头的重要集成电路研究院迎新进展

5月7日,“合肥综合性国家科学中心集成电路先进材料与技术产教研融合研究院”发展战略研讨会在安徽大学举行,国内相关科研领域15位院士及专家参加会议。

图源:安徽大学

安徽大学官网5月8日消息显示,由安徽大学牵头,“高校—院所—企业”联合共建的“集成电路先进材料与技术产教研融合研究院”,获得安徽省省“三重一创”专项支持,正式入列合肥综合性国家科学中心。

安徽网报道显示,该研究院建设单位为安徽大学,合作单位包括:中电集团第38所、第43所、华东光电集成器件研究所、知名集成电路企业、中科院合肥物质科学研究院等。参与研究院建设的团队20余个,教学科研人员200余人,并通过双聘和特聘方式引入集成电路领域的高级专家。

参会专家组认为,研究院的建设,将加快建立覆盖从基础材料研究、芯片封装工艺以及测试技术和产品的转化及产业化的集成电路全产业链的公共技术服务平台体系,有利于培养涵盖集成电路全环节、工程和创新能力兼具的集成电路中高端人才,解决人才培养的质量与数量和集成电路产业需求不匹配的问题。专家组一致通过“合肥综合性国家科学中心集成电路先进材料与技术产教研融合研究院”建设方案。

此外,该研究院通过“四平台一中心”,建成基础材料与电子材料原创设计、研发到验证的共享研发平台;培养贯穿“本—硕—博”全过程的集成电路领域高端人才,形成面向集成电路产业的人才培养体系,推动产教研融合发展等。

*此内容为集微网原创,著作权归集微网所有,爱集微,爱原创

【IPO价值观】产品结构单一,环动科技业绩高度依赖埃斯顿

专利申请

专利申请

知识产权质押融资

知识产权质押融资

专利地图分析

专利地图分析

版权登记

版权登记

集成电路布图设计

集成电路布图设计

商标交易

商标交易

商标申请

商标申请

专利交易

专利交易

专利无效

专利无效

热门评论