台积电先进封装大解密:超越摩尔计划延续竞争力

【编者按】本文作者曲建仲,内容来自曲博科技教室,集微网经原作者授权转载。

缩小晶体管的制程节点(7纳米、5纳米、3纳米)可以缩小芯片(Chip),缩小芯片可以缩小印刷电路板(PCB:Printed Circuit Board),而缩小印刷电路板就可以缩小电子产品的尺寸,因此制程节点是朝向愈来愈小的方向发展,但是先进制程发展到3纳米以下开始接近极限,一般认为「极紫外光(EUV:Extreme Ultraviolet)」的极限是1纳米,因此1纳米以下的制程发展会遇到瓶颈,该怎么办呢?

什么是系统单封装(SiP:System in a Package)?

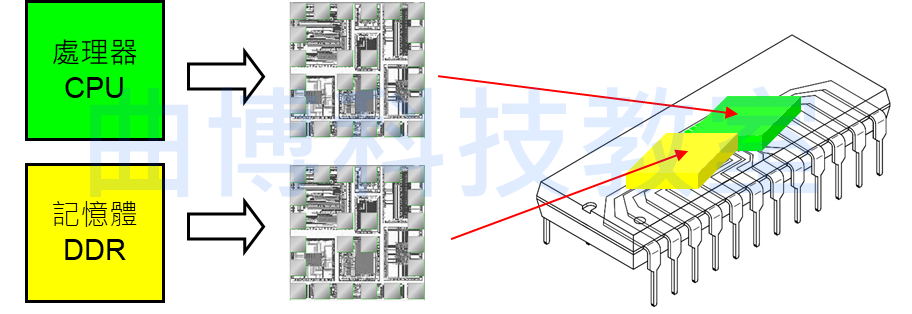

将数个功能不同的芯片(Chip)直接封装成具有完整功能的「一个」集成电路(IC:Integrated Circuit),称为「系统单封装(SiP:System in a Package)」。例如:将计算机的处理器(CPU)与内存(DDR:Double Data Rate SDRAM)封装在一起,如图一所示,此时仍然是两个独立的芯片,只是封装在同一个外壳而已,比发展先进制程更简单,在某些特别的应用上甚至可以将被动组件、连接器、天线等一起封装进去,先进封装就是一种系统单封装技术。

图一 将计算机的处理器(CPU)与内存(DDR)封装在一起。数据源:曲博科技教室。

先进封装的前段(FE)与后段(BE)

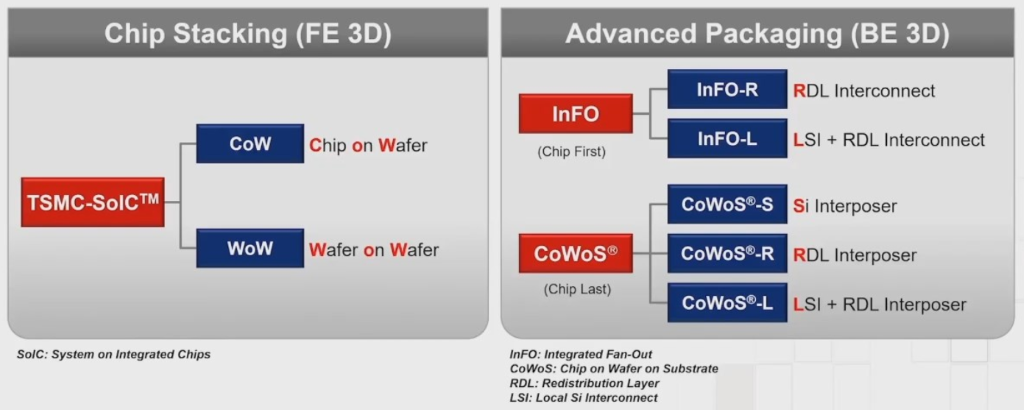

先进封装是指使用左右水平或上下垂直的方法将芯片堆栈起来,同时缩小集成电路的一种技术,可以再细分为前段与后段如图二所示:

立体封装前段(3DFE:3D Front End):也就是集成电路内部的芯片堆栈技术,如何把许多芯片堆栈起来?又可以分为「芯片堆栈晶圆(CoW:Chip on Wafer)」与「晶圆堆栈晶圆(WoW:Wafer on Wafer) 」两种。

立体封装前段(3DBE:3D Back End):也就是集成电路外部的导线分布技术,如何分布导线才方便接下来和印刷电路板(PCB)连接。

传统的封装都是在「封装厂」中进行,有点像是传统的精密机械工业,但是先进封装大部分是利用「晶圆厂」的技术直接在晶圆上进行,由于这种技术更适合晶圆厂来做,因此台积电大部分的先进封装都是自己做的。

图二 台积电先进封装分类图。数据源:台积电。

晶圆级晶粒尺寸封装(WLCSP:Wafer Level Chip Size Package)

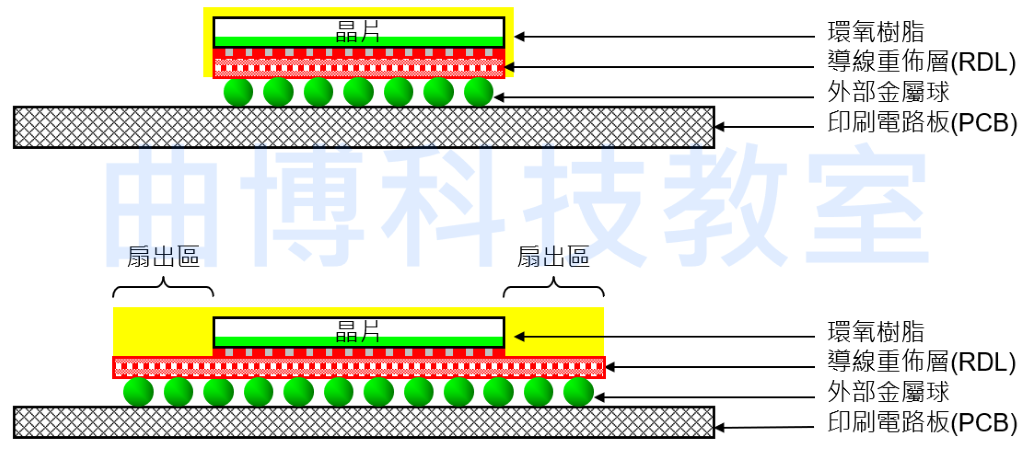

所谓「晶圆级(Wafer level)」是指先将「整片晶圆」或「许多芯片」封装好以后,再进行切割的动作,如果封装以后体积比封装前增加少于120%,则称为「晶粒尺寸封装(CSP:Chip Size Package)」。使用晶圆级封装主要是可以将大量的芯片一起封装制作,因此可以提高产能降低成本,晶圆级封装又分为「扇入型(Fan-in)」与「扇出型(Fan-out)」,如图三所示:

扇入型晶圆级封装(Fan-in WLP):可以将整片晶圆封装好以后再进行切割的动作,但是必须把外部金属球制作在芯片面积内,因此只适合接脚数较少的集成电路,例如:电源管理集成电路(PMIC:Power Management IC)。

扇出型晶圆级封装(Fan-out WLP):先将晶圆上的芯片切割以后,芯片之间拉开一段距离形成「扇出区(Fan-out area)」,再转移到一片暂时性的玻璃板,许多芯片一起封装好以后,再进行切割的动作,可以把外部金属球制作在芯片面积外的扇出区,适合接脚数较多的集成电路,例如:苹果的处理器大部分是使用这种封装技术。

使用扇出型晶圆级封装也可以将多个不同的芯片封装在一起,这种技术台积电称为「整合扇出型封装(InFO:Integrated Fan-out)」。

图三 扇入型(Fan-in)与扇出型(Fan-out)封装。数据源:曲博科技教室。

先进立体封装技术

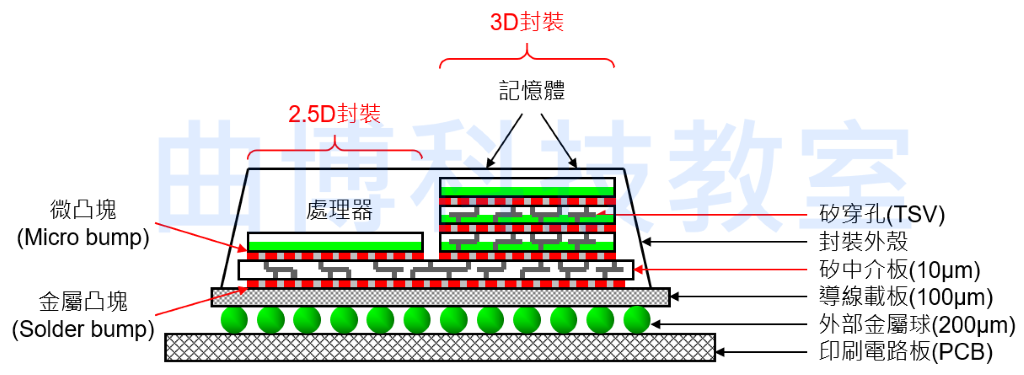

将数个功能不同的芯片(Chip)切割后再用「硅中介板(Silicon interposer)」整合起来,称为「芯片堆栈晶圆(CoW:Chip on Wafer)」,硅中介板上有许多微小的「硅穿孔(TSV:Through Silicon Via)」填入金属,然后再整合在「导线载板(Laminate substrate)」上。

由于硅中介板上的金属线路比较细 (大约10微米),导线载板上的金属线路比较粗(大约100微米),因此用这种方式封装可以让芯片靠得更近,不但缩小面积也加快讯号在不同芯片之间流动,这种技术台积电称为「芯片堆栈晶圆堆栈基板(CoWoS)」,如图四左半边所示,其中Wafer是指「硅中介板」, Substrate是指「导线载板」,因为使用硅中介板来「左右水平」堆栈芯片,不算是真正的3D立体堆栈,因此称为「2.5D封装」。

直正的3D封装必须「上下垂直」堆栈芯片,如图四右半边所示,图中绿色代表芯片的正面,也就是含有晶体管的那一面,要达到这个必须将「硅穿孔(TSV)」制作在含有晶体管的芯片上,这个难度很高,目前主要应用在内存堆栈,这种内存称为「高带宽内存(HBM:High Bandwidth Memory)」。

图四2.5D与3D立体封装技术。数据源:曲博科技教室。

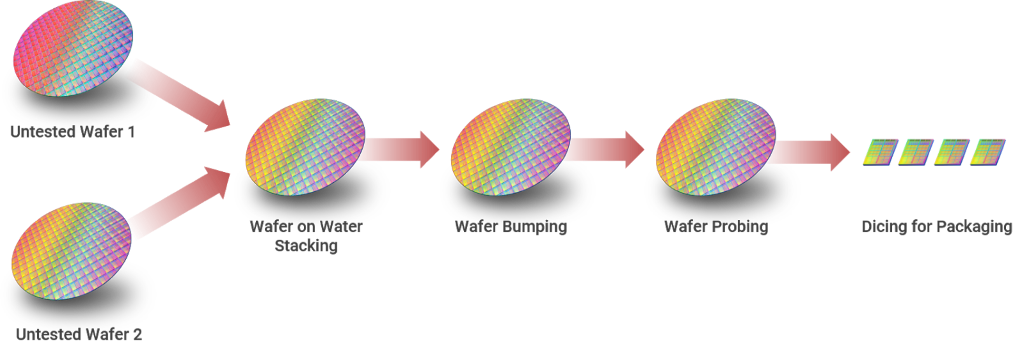

晶圆堆栈晶圆(WoW:Wafer on Wafer)

立体封装技术还有另外一种方法,将「硅穿孔(TSV)」制作在含有晶体管的芯片上,再将不同的晶圆「上下垂直」堆栈起来,最后再切割后就成为集成电路,如图五所示。这样制作难度很高但是可以大量生产,是未来可能的发展方向,台积电把前面介绍的这些先进封装技术整合起来称为「系统堆栈芯片(SoIC:System on Integrated Chips)」,有了这些技术,即使先进制程遇到瓶颈仍然能够持续缩小集成电路。

图五 晶圆堆栈晶圆(WOW)技术示意图。数据源:台积电。

小芯片(Chiplet)成为集成电路发展新趋势

最早期的电子产品是将主动组件晶体管与被动组件电阻、电容、电感等独立的电子组件分别焊接在印刷电路板(PCB)上的,后来发明了「集成电路(IC)」,将所有晶体管整合缩小制作在一个硅芯片(Chip)上,再封装成一个集成电路(IC)。整合愈多晶体管功能愈完整,虽然使得芯片(Chip)与集成电路(IC)的面积变大,但是印刷电路板(PCB)上的电子组件大幅减少使得电子产品的体积大幅缩小,这是过去50年来集成电路产业的发展方向。

后来走火入魔整合的晶体管愈来愈多,开始发展「系统单芯片(SoC:System on a Chip)」,将多核心中央处理器(CPU)、图形处理器(GPU)、射频(RF)等都整合到单一芯片,使得芯片(Chip)的面积变大,内部的通讯联机也很复杂,而且芯片变大良率降低成本变高。

如图六所示,假设同样是六颗灰尘掉在晶圆上,当芯片较大共计12个,坏了6个,好的6个,良率为50%,当芯片较小共计24个,坏了6个,好的18个,良率为75%,显然芯片愈小良率愈高,成本愈低,因此最近又开始朝向「小芯片(Chiplet)」的方向发展。

图六 芯片愈大,良率愈低成本愈高;芯片愈小,良率愈高成本愈低。

将多核心中央处理器(CPU)做成一个小芯片,图形处理器(GPU)做成一个小芯片,射频(RF)做成一个小芯片,这样可以降低成本,问题是三个小芯片(Chiplet)如果各自封装,会形成三个集成电路(IC),结局又使得印刷电路板(PCB)变大,那么该怎么辨呢?

因此业界开始使用前面介绍的2.5D或3D立体封装,将三个小芯片(Chiplet)封装成一个集成电路(IC),不同的小芯片(Chiplet)可以各自成为不同的模块(Module),变成不同的知识产权(IP)来进行转移或交易,这样的「模块化(Modularized)」可以减少设计的时间和成本。

超越摩尔(More than Moore)计划

摩尔定律(Moore's law)是由英特尔(Intel)创辨人之一的戈登摩尔提出,主要内容是集成电路上可容纳的晶体管数目,大约每隔两年就会增加一倍,芯片的效能也会提高一倍,但是受限于制程的物理极限,晶体管缩小的技术发展日渐困难,成本也愈来愈高,因此有必要利用其他手段缩小集成电路的尺寸同时降低成本。所谓的「超越摩尔(More than Moore)」是指以系统应用的概念为出发点,不执着在晶体管的制程点缩小的摩尔定律,而更应该将各种技术进行异质整合,其中最重要的方法之一就是前面介绍的先进封装技术,而台积电的整合扇出型封装(InFO)、芯片堆栈晶圆堆栈基板(CoWoS)、系统堆栈芯片(SoIC)等先进封装技术目前都领先业界,超越摩尔计划延续竞争力。

此外,在<台积电用一流人才做二流工作?>一文中曾经提到,台积电有三大弱点,或者应该说是台湾半导体产业共同的弱点:先进制程所使用的材料与特用化学品大部分是进口的;先进制程所使用的制程设备大部分是进口的;先进的内存制程落后三星。因此台积电在先进制程领先全球之后,台湾应该利用这个机会进行产业升级,培植相关的半导体供应链,包括先进制程所使用的材料、特用化学品、制程设备研发等,由于先进制程的设备是纳米等级,开发的难度较高,相对先进封装的设备只有微米等级,开发的难度较低,因此培植本土的设备研发可以由先进封装开始是一个不错的方向。

产业观察:上市潮来临,国产GPU还需面对五大挑战

专利申请

专利申请

知识产权质押融资

知识产权质押融资

专利地图分析

专利地图分析

版权登记

版权登记

集成电路布图设计

集成电路布图设计

商标交易

商标交易

商标申请

商标申请

专利交易

专利交易

专利无效

专利无效

热门评论