长存创始人杨士宁提出三维异构集成发展三大建议:软硬件共筑生态、持续技术创新、成立自主组织

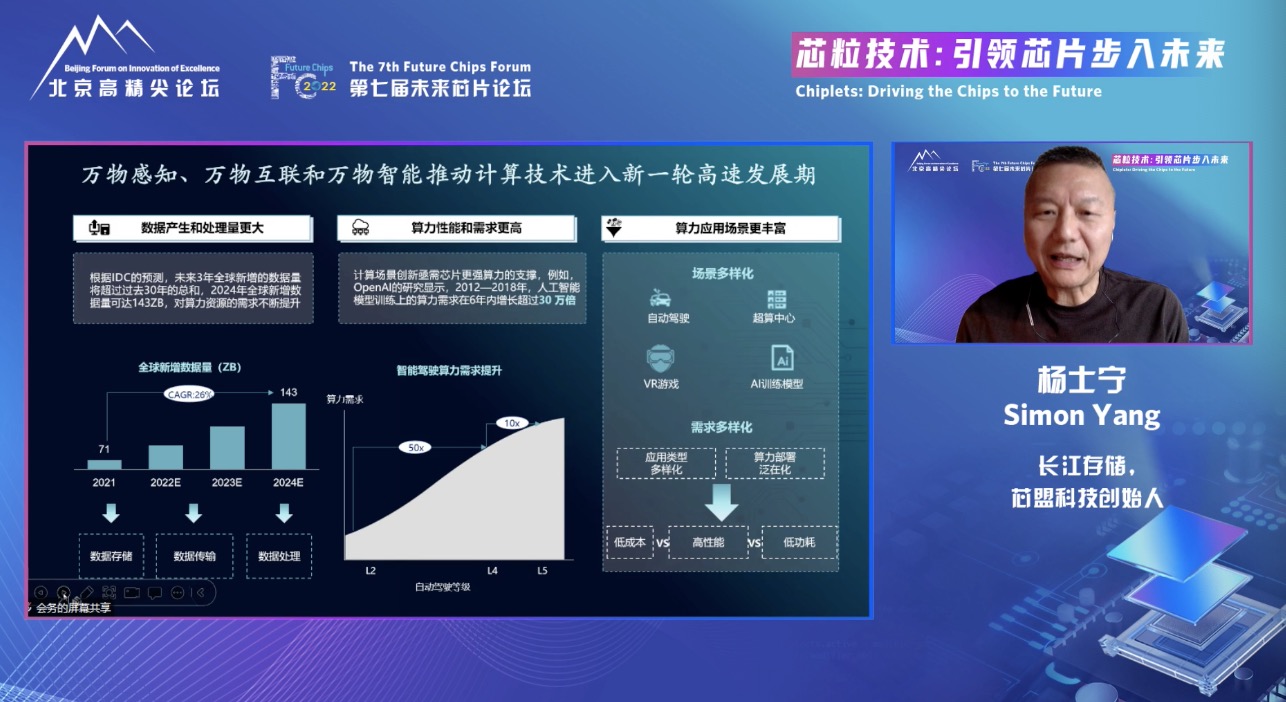

1月15日,在清华大学集成电路学院集成电路高精尖创新中心主办的第七届未来芯片论坛上,长江存储、芯盟科技创始人杨士宁在第七届未来芯片论坛上发表了以《芯粒技术:引领芯片步入未来》为主题的演讲稿。

杨士宁指出,大数据、物联网、云计算、元宇宙等应用对数据和计算能力需求极大,整个应用端对集成电路的集成度、性能的提高速度没有丝毫减弱的迹象。然而摩尔定律已经趋缓,业内都在思考使得芯片性能跟上应用端需求的解决方案。

“从1965年到2015这50年间是摩尔定律的辉煌时期,但到2015年,即40纳米到28纳米工艺节点时,摩尔定律发展速度变缓。2015到2025年将是一个过渡期,需要大量的结构、材料创新来勉强支撑摩尔定律的发展。到了2025年以后,高性能芯片对集成度、性能的要求极高,三维异构集成将必然发展趋势。”他解释说道。

杨士宁表示,“芯粒现在很火热,并不是说它是一个新事物,实际上是三维异构集成有了新能力。整个行业本来就是从小芯片开始,只是我们推进到SoC做大芯片了,现在走不下去了,又要退回去把Soc拆开。最终我们要推动的方向是要有能力把多颗小芯片集合成一颗单芯片,因为单芯片才有很快的通道、很低的运算数据传输,芯片和芯片之间可以直接互联,而且互联的节奏是在百万级以上。”

据他介绍,三维异构集成的应用非常广泛,包括高性能计算、自动驾驶、元宇宙等。“它不仅是存算一体化,实际上还是逻辑和逻辑,如果逻辑芯片之间的工艺、成本差别很大,最后可以用维异构集成把它对接成同一个工艺。”

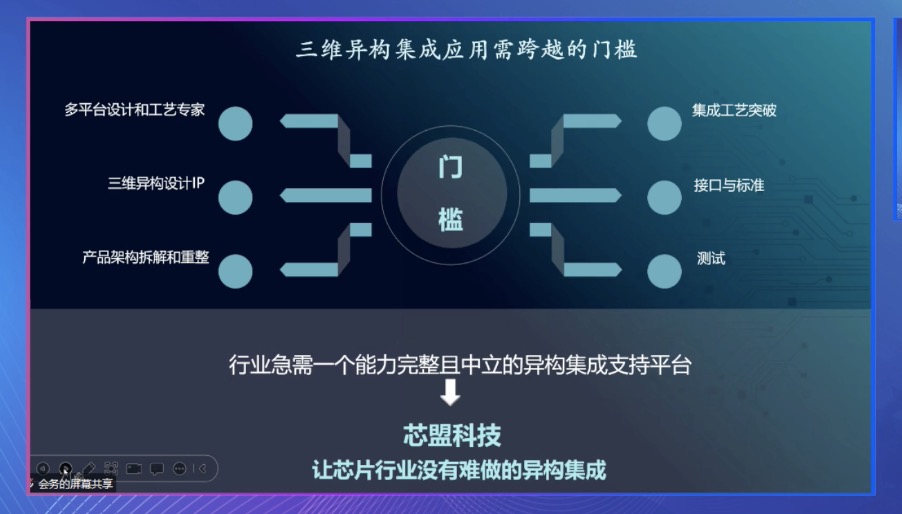

杨士宁同时指出,三维异构集成应用仍需跨越六大门槛。一是需要多平台的设计和工艺的专家;二是集成工艺突破;三是三维异构设计IP,特别是要解决数据怎么对接,存储器怎么控制的问题;四是接口的标准化;五是产品的整体架构的拆解和重组;六是不同阶段测试如何到位。

基于此,行业急需一个能力完整且中立的异构集成支持平台。芯盟科技三维异构集成已有4年发展历程,能够提供三维异构集成设计+制造全周期一整套服务,包括IP开发和授权、基于HITOC技术的集成设计以及后续方案等。

最后杨士宁提出了对异构集成发展的几点建议。一是实际上异构集成是需要设计、软件、硬件、制造协同合作的一个生态,所以行业内的互相交流非常重要;二是这个领域比较新,需要不断进行技术创新、不断投入;三是要成立类似“UCle”的自主组织,协调业内在硬件、设计的创新以及架构的重组。

(校对/王云朗)

*此内容为集微网原创,著作权归集微网所有,爱集微,爱原创

【个股价值观】新洁能:四大平台功率全系覆盖,车规应用提振业绩回暖

专利申请

专利申请

知识产权质押融资

知识产权质押融资

专利地图分析

专利地图分析

版权登记

版权登记

集成电路布图设计

集成电路布图设计

商标交易

商标交易

商标申请

商标申请

专利交易

专利交易

专利无效

专利无效

热门评论