从芯片最初的架构设计到最后的流片,验证工作贯穿了整个设计流程,整个芯片设计70%左右的工作量已经被验证所占据。

其中,版图验证是必不可少的一个环节,主要包括设计规则检查 (DRC) 、电路图版图对照检查 (LVS) 、版图的电路提取 (NE) 、电学规则检查 (ERC) 和寄生参数提取(PEX) 。

而设计规则检查(Design Rule Checking,DRC)是版图验证中的重要工具,包括设计规则检查,检查连线间距、连线宽度等是否满足工艺要求。它在版图几何图形上执行检查,确保版图数据能够进行生产,并在给定的集成电路工艺技术上得到高成品率。

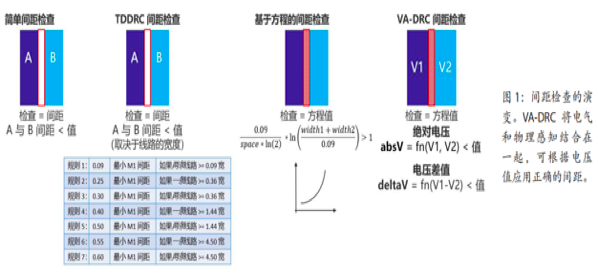

随着集成电路规模和复杂度不断增大,验证的难度、工作量也急剧增加,设计规则检查(DRC)间距检查的复杂性更显著增加。目前,简单的间距检查已演变成需要采用表格驱动式DRC(TDDRC)方法的检查,以便考虑走线长度和线路宽度的影响。尽管TDDRC 有助于简化海量参数组合的读取和维护,但要涵盖参数之间的连续关系,还需要开发基于方程的DRC,便于更准确地评估曲线和复杂方程。

除上述情况外,因当今设计通常具有许多电源域,使得高压网络与低压网络在其中紧密相连。尽管这类布线在以往的设计中并不罕见,但现在紧凑的布局加上电压域之间存在复杂的交互作用,可靠性便会受到影响。为了符合工艺、可靠性和电源管理要求,我们采用基于方程的检查,使用被称为电压感知 DRC (VA-DRC) 的新验证方法满足对现有节点和新节点的可靠性要求,VA-DRC 检查会根据绝对电压或差值电压 (DV) 值灵活调整要求,进而确定间距要求。

间距检查的演进

尽管电压感知 DRC (VA-DRC) 的新验证方法能满足对现有节点和新节点的可靠性要求,但是VA-DRC间距准确性却实难把控。

原因是VA-DRC 检查的关键一环将电压信息纳入检查之中。早期的 VA-DRC 流程需要使用手动标记,用电压域信息标注多边形。该方法针对老节点仍是可行的解决方案,但是随着行业生产的多电压设计变得更为复杂,以及设计人员在设计中寻求更多空间,手动标记的复杂性可能会呈爆炸性增加。人类不可避免地会犯错,因此标注过程也会变得容易出错。有时标记会被遗漏,或者标记会触及错误的多边形。某些标记或属性也有可能相互矛盾,这在多层层次整合之后的后期设计阶段十分常见。

为消除人为错误并提高当今复杂设计中VA-DRC 间距的准确度,Calibre® PERC™ VA-DRC流程中新增了自动感知情景的电压传导和标注功能。凭借可以基于静态传导规则传导准确电压值的自动化流程,Calibre PERC 增强的 VA-DRC 功能在准确度方面超过了传统的纯几何检查和手动标注VA-DRC。

此外,在传统的可制造性设计(DFM)DV 间距结果中,仅显示多边形之间的间距违规。对于设计人员而言,若没有这些违规所涉及的网络或电压域条件,调试这些错误将是一项耗时且令人头疼的任务,并且修复经常需要猜测。

然而,Calibre PERC增强的VA-DRC 调试结果显示在这些多边形的网络之间,与传统的调试技术相比,具有明显优势。Calibre PERC增强的结果为边对中的每个边附加一个网络名称属性,让设计人员能够获得所需的电气信息,根据源网络和实例名称,在 Calibre RVE™ 结果查看器 GUI 中跟踪和调试违规行为(基于源的流程)。

Calibre PERC增强的VA-DRC流程能够使用 Calibre RVE 结果查看界面之类的 GUI 进行跟踪和调试,从而支持更强大的调试和错误修复功能。增强VA-DRC检查的情境感知,可为设计人员提供可采取行动的反馈,帮助他们在调试期间实施更有针对性的修复。此外,设计人员还可以根据自己的需求自定义结果报告。

在现有节点和新节点上设计高压和多电源域应用的公司需要严格的准确度,才能实现高可靠性和高良率。Calibre PERC增强的情境感知 VA-DRC可以帮助实现更高的准确度,确保高设计可靠性和制造良率。这对于像汽车电子、稳压器等高压应用的可靠性验证非常重要。

有了这种高准确度和可采取行动的情境感知结果来支持明智调试,工程师可以使用 Calibre PERC 增强的VA-DRC 流程保证生产率、精确度和可靠性。这些是在时间紧凑且创新不断的市场中取得成功的关键因素。

如果您想进一步了解Calibre PERC先进的电压感知DRC的相关信息,就请点击这里下载白皮书查看原文。

(校对/范蓉)