几十年来,IC 行业一直试图跟上摩尔定律的步伐,即每 18 到 24 个月将芯片中的晶体管密度翻一番。一个普遍性的看法是,传统的制程缩放地位终将动摇,行业急需其他路线的帮助,以保持在摩尔定律的增长路线上。于是,先进制程范畴的晶体管结构和支撑结构范畴的封装技术都开始通过维度升级,为推动芯片性能提升提供额外的支持。Chiplet作为一种异构集成形式,极大地发挥出了3D架构的优势,我们注意到,多条2D-3D的技术升维之路,纷纷指向了Chiplet。

晶体管结构升维

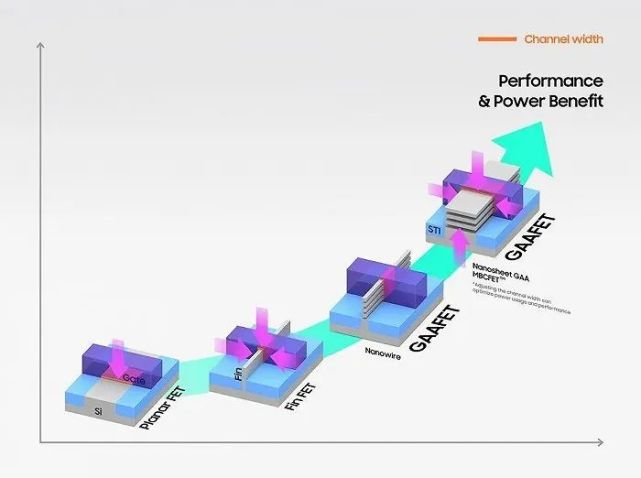

Process roadmap:Planar FET-FinFET-GAA

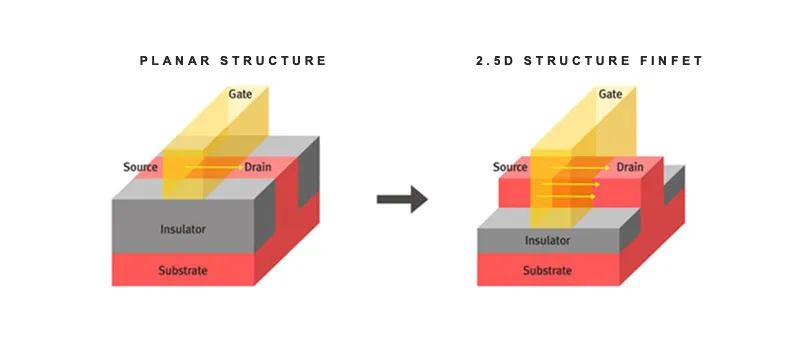

2D:Planar FET

传统的2D平面结构晶体管Planar FET,已在多个制程节点上延续多年。但在2011年,制程演进至20nm节点时,Planar FET结构遭遇了瓶颈,这种2D结构的平面晶体管结构开始出现短沟道效应(Short-channel effects)。短沟道效应可以理解为:如果将晶体管看作一个开关,则开关应当完全关闭时,晶体管的源极和汲极却在漏电。于是,2011年以后,芯片制造商开始用FinFET取代平面晶体管。

来源:samsumg

2.5D:FinFET

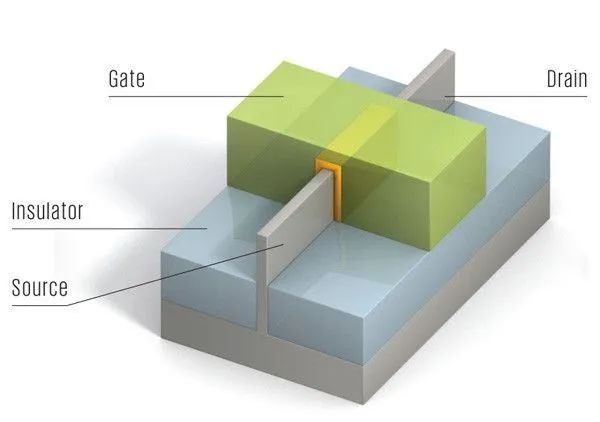

1999年,FinFET诞生于加州大学,FinFET结构主要为突破芯片25nm进程,解决MosFET由于制程缩小伴随的隧穿效应而研发,目前在先进工艺下的FET大多为FinFET。

FinFET结构形似鱼鳍,也被称作鳍型结构。这种结构主要有两大优势:Gate三面环绕D、S两极之间的沟道(通道),沟道变宽,导通电阻降低,流过电流能力增强;漏电情况大幅减少,这种结构的晶体管结构一直广泛沿用至今。

FinFET典型结构

但是,随着制程进一步缩小,FinFET结构同样开始出现漏电问题,原本制程演进的功耗和性能红利不再,FinFET逐步让位于3D结构的GAAFET。

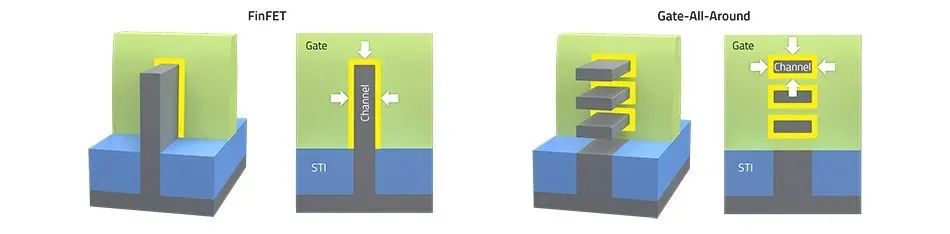

3D:GAAFET

GAA的中文全程为全环栅晶体管,其结构在本质上就是把FinFET的fin转动90°,再把多个fin横向叠起来,这些fin都穿过gate,或者说被gate完全环抱,所以叫做gate all around。此外,由于每个翻转过的fin都像是一片薄片(sheet),它们都是channel,因此GGAA也被称为Nanosheet FET。

从结构上来看,GAAFET电晶体的gate与channel的接触面积变大了,且每一面均有接触,相比FinFET结构可以实现更好的开关控制。同时,相比FinFET,GAAFET的sheet宽度与有效通道宽度更为灵活。更宽的sheet能够达成更高的驱动电流和性能,更窄的sheet则占用更小的面积。

来源:semiengineering

作为接替FinFET的晶体管结构,GAA的出现被视为晶体管从2.5D到3D的巨大演进和3nm之后的芯片制造方向。今年6月,Samsung 已经正式开始以 GAAFET架构量产3nm 制程芯片,并首度采用了MBCFET技术,三星称其“突破了过去 FinFET 的效能限制”,可以通过降低电压水平的方式提高电源效率,同时还能靠增加驱动电流能力来提升效能。三星官方数据表示,相比7nm FinFET制造工艺,3nm GAA FET技术逻辑面积效率提高35%以上,功耗降低50%,逻辑面积减少45%。

Samsung 3nm GAAFET

一代代先进工艺和晶体管架构的进步,推动着进展迟滞的摩尔定律继续前行。然而,对晶体管架构的3D化探索依然无法填补算力需求与实际性能提升间的鸿沟,行业探讨的重心逐渐转向了先进封装工艺。

封装技术升维

我们正在进入一个先进封装的时代。人们不再一味追逐光刻尺寸的极致微缩,而试图在不改变半导体制程工艺节点的前提下,借助先进封装技术,将异质、异构的芯片通过并排或垂直堆叠的方式集成至同一封装内,以实现更高的集成度,更好的电气性能、更低的时延,以及更短、更垂直的互连要求。近年来,半导体封装的创新步伐也大大加快,逐渐从传统技术的扩展到新出现的技术,如2.xD封装、2.5D、3D封装转变。

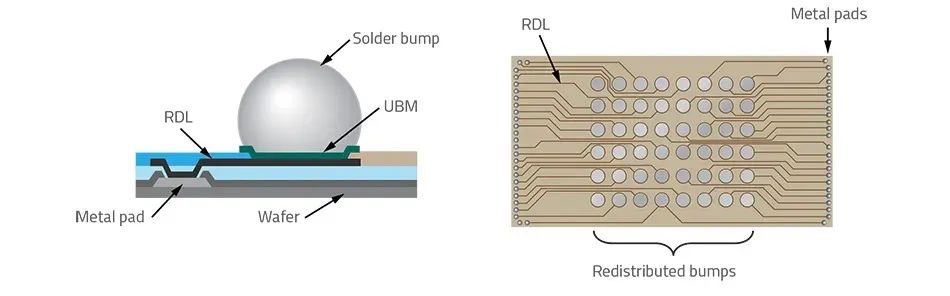

2.xD:RDL

2.xD封装,是指基于基板(Organic substrate)上的RDL再分布层(Redistribution layer),将不同的裸片连接在一起。RDL是芯片上的额外布线层,可以从芯片上的不同位置进行键合,从而使芯片到芯片的键合更加简单。如今,RDL技术已经成为2.xD/2.5DIC/3DIC封装方案中不可或缺的一部分,使芯片可以通过中介层相互通信。

Source: Lam Research

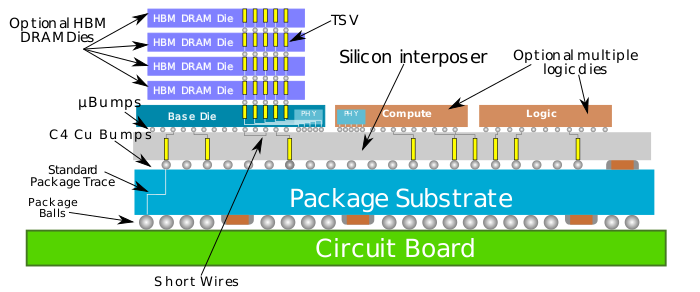

2.5D:Passive Interposer

为了突破Reticle limit的限制,封装开始转向2.5D结构。在2.5D结构中,两个或更多的chiplet被并排放置在Interposer上,以实现极高密度的互连。相比2.xD封装,2.5D封装的关键在于在chiplet的底部增加了一层薄薄的Passive interposer(中介层)。

「Passive Interposer」

是封装中多芯片模块或电路板传递电信号的管道,也是插口或接头之间的电接口,可以将信号传播更远,也可以连接到基板上的其他插口。Passive interposer通常由硅和有机材料制成,充当多颗芯片与电路板之间的桥梁。

Interposer structure in 2.5D packaging. Source: Lam Research

「CoWos」

2.5D封装技术以特尔的EMIB、台积电的CoWoS、三星的I-Cube为代表。CoWoS封装技术最早是从2012年由台积电开始推行。作为一种2.5D晶圆级多晶片封装技术,一方面进行side-by-side的多die封装,另一方面则通过CoW技术把芯片3D垂直堆起来。CoWoS能够实现较高的互连密度和性能,其上的每个die 或chiplet通过micro-bump键合到interposer上:

图源:台积电

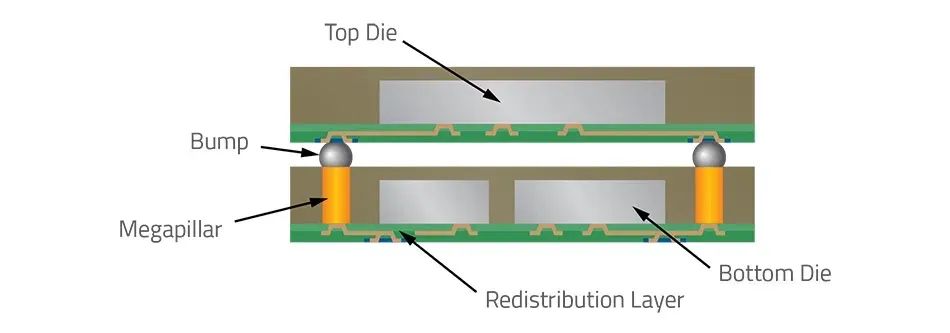

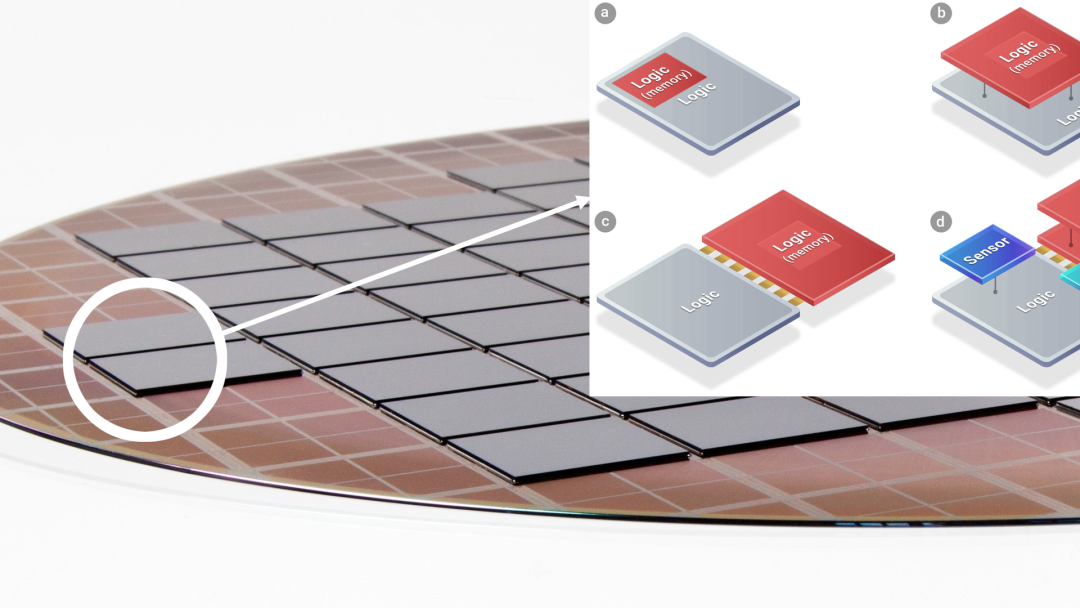

3D:3D Stacking

3D封装技术,是指堆叠多颗不同芯片成为一个单一的封装以节省空间。3D封装和2.5D封装的主要区别在于:2.5D封装是在Interposer上进行布线和打孔,而3D封装是直接在芯片上打孔和布线,通过TSV技术电气连接上下层芯片。相较于2.5D封装,3D封装能显著缩小芯片尺寸、增进芯片的性能和运转速率,CoW和WoW是目前两种主流的3DIC封装技术。

WoW「Wafer on Wafer」

简单来说,就是将多个芯片堆叠起来,从以往的2.5D封装在晶圆上水平放置模块的方式,改为垂直放置两个或以上的模块。通过WoW技术,可以把更多的模块放到相同面积的晶圆中,并能使每个芯片以极高的速度和极低的延迟通信,从而实现芯片性能和能耗比的全面提升。不过,WoW也存在着问题:晶圆被粘合在一起后,一荣俱荣、一损俱损。哪怕只有一个坏了,另一个没坏,也只能把两个都丢弃掉。

CoW「Chip on Wafer」

是一种在硅晶圆上堆叠Chiplet的技术,将多个Chiplet通过封装制程连接至硅晶圆。相较于CoWoS和WoW,SoIC更倚重CoW设计。对于芯片业者来说,采用CoW设计的芯片,生产上会更加成熟,良率也能得到大幅提升。

Chip on wafer。来源:TSMC

「3D Stacking on Chiplet」

如今,将一个大芯片切割为多个Chiplet已成为业界提升芯片性能及良率的热门选择。

Chiplet 在一颗采用先进工艺制程的芯片中,将一些通用的模块以较低的工艺制程集成至Base Die(相对于Passive interposer,Base Die中不只有电路,还可以有其他的模块,通过RDL和TSV技术进行水平和垂直方向的互连)上,可以减少芯片对高工艺制程的依赖。此类代表产品如Intel的LakeField、Ponte Vecchio、AMD的Zen3+。

「Future of 3D Stacking」

相较传统封装技术,3D堆叠技术具备集成度、性能、功耗等多方面的优势,并可以实现更高的设计自由度,开发时间更短。当前,3D堆叠的主流技术为双层堆叠,但随着先进封装技术的发展,3D堆叠技术也在不断的实现新的突破。在2021年,IMEC的研究人员首次实现了多达四个半导体层的堆叠,允许不同模具之间通信。

未来,随着高性能运算、人工智能等应用的不断拓展,以及用于多个晶圆垂直通信的TSV技术的愈发成熟,相信3D堆叠技术会更广泛地应用在逻辑芯片领域,实现多种芯片之间(如CPU和GPU芯片、逻辑和存储)的多层堆叠。

互连技术升维

通过先进封装,将芯片沿3D方向进行堆叠,可以显著缩减封装尺寸,提高封装结构的空间利用率,实现芯片性能和速率的进一步提升。其中,互连技术的突破至关重要。

Bump

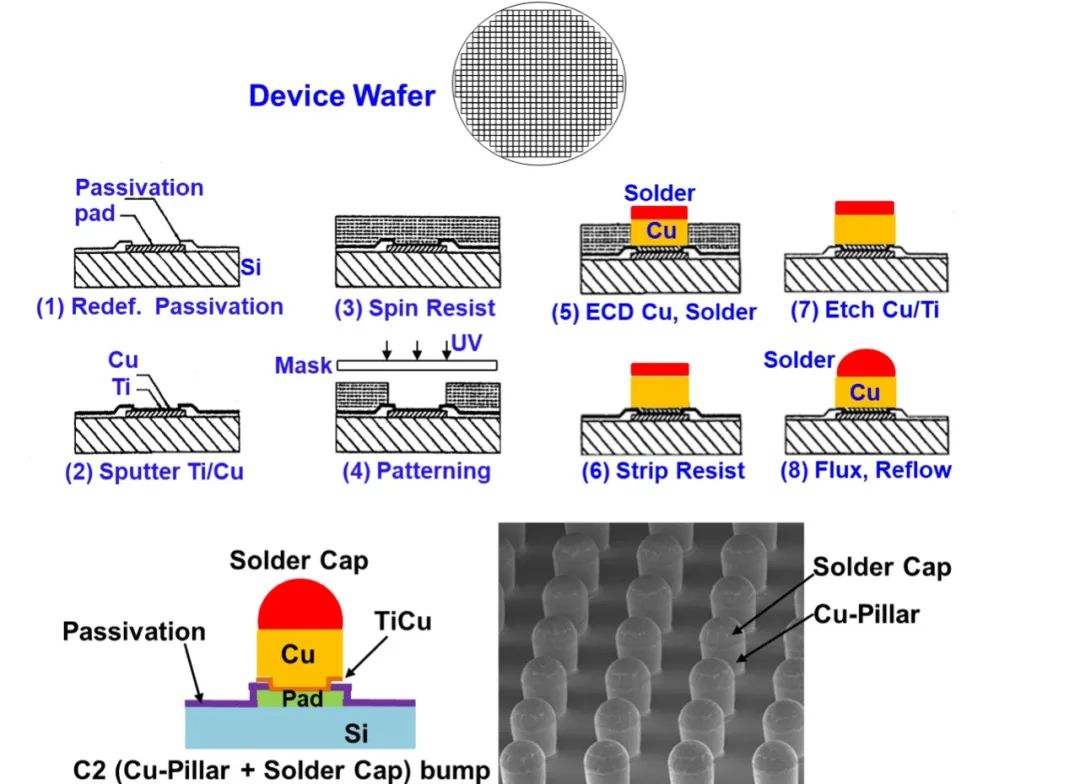

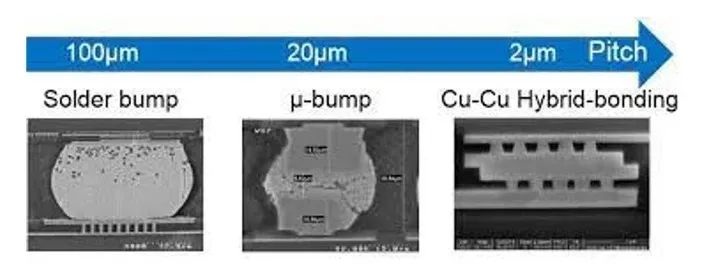

早在 1960 年代,业界就开发了倒装芯片技术来提高封装中的 I/O 数量。倒装芯片是一种互连方案,提供从芯片到芯片、芯片到电路板的连接。在倒装芯片流程中,Bump被安装在单独的芯片或电路板上,形成电气连接。Bump直径从75µm至200µm。由于尺寸原因,Bump的用途受到了限制。从2005年的65nm节点开始,芯片企业开始转向更小的Microbump。

Microbump

与Bump相比,Microbump能以更小的间距和更好的导热性实现更多的 I/O,这也是它们成为许多中高端封装的主流互连技术的原因所在。同时,为了实现更快速的连接,Bump的尺寸还在不断缩减。

Microbump 工艺流程。资料来源:John Lau,Unimicron

Hybrid Bonding

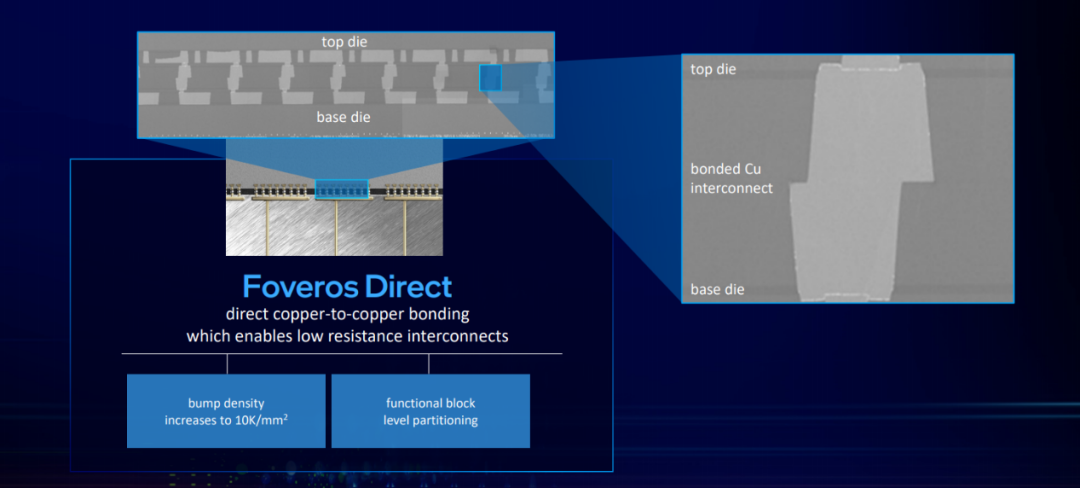

2020年,Hybrid Bonding(混合键合技术)由英特尔推出。该技术最鲜明的特点是没有凸点(no-Bump)的键合结构,因此具有更高的集成密度和性能。这种不用Bump而是TSV铜铜直连的封装技术,能实现10倍以上的集成密度。

从技术的角度来看,使用Microbump、Hybrid Bonding之间有明确的界限。Microbump的间距约为 10 至 20µm 及以上,而Hybrid Bonding为 10µm 及以下。由于凸点消失,硅片间没有了空隙,无需填充胶,并具有更好的热性能。

Imed Jani. Test and characterization of 3D high-density interconnects.

当下,Hybrid Bonding技术已被广泛地应用在3D Chiplet领域,与3D堆叠封装技术结合,更比现有的3D封装方案高出超过15倍的密度,进一步减少缓存与芯片的数据传输距离,缩短延迟时间。

Foveros Direct,来源:Intel

趋于停滞的摩尔定律已成为时代的隐痛。而全社会的数字化转型、AI对算力的贪婪需求、自动驾驶技术的突飞猛进,都在要求半导体制程持续加速演进。在延续、乃至超越摩尔定律预测的道路上,多条2D-3D的道路纷纷汇聚到Chiplet技术中,并还在不断的更新,相信未来,我们将会看到越来越多的Chiplet设计,并最终重塑芯片设计和制造格局。