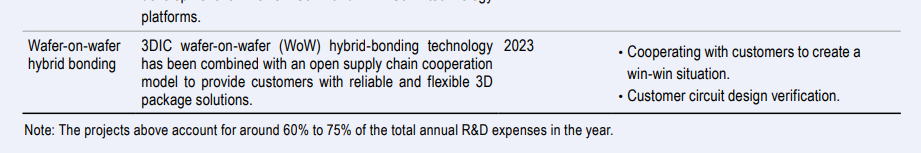

集微网消息,继台积电与三星之后,全球第三大晶圆代工企业联华电子(UMC)近日也在3D IC领域有了新动作。该公司将与EDA巨头西门子携手,为其客户提供芯片-晶圆(C2W)、晶圆-晶圆(W2W)键合所需的三维集成电路规划、组装验证和寄生参数提取工作流。

联电此番动作,应是为其年报中提到的、拟于2023年推出的3D IC混合键和工艺进行铺垫。而将视野进一步放宽,又一家集成电路前端制造环节“大厂”在3D IC领域拓展布局,则标志着这条“赛道”进一步迫近大规模产业化阶段,不同厂商布道的理念愿景与演示的技术能力,将越来越难“豁免”真实商业世界检验。

掌握制造技术不等于商业成功

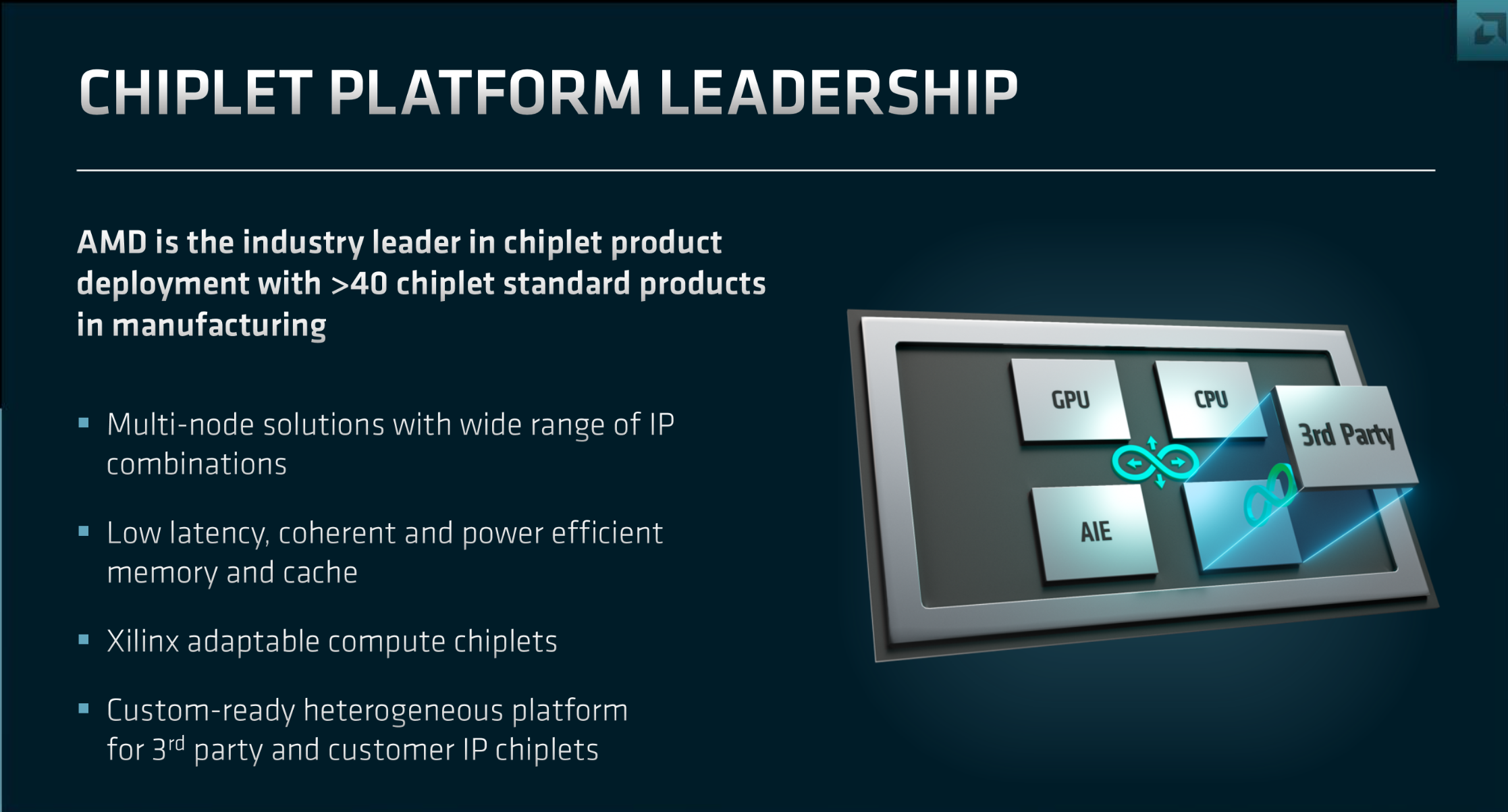

以2.5D/3D堆叠多个裸片/芯粒(chiplet)构成的3D IC,由于可以实现传统SoC各片上模块的“解耦”,为芯片功能、性能、成本、开发周期的综合优化提供了全新想象空间,其效果也已经通过AMD等公司的先驱性产品得到验证。

凭借“续命”摩尔定律的技术愿景和助力大陆厂商“换道超车”的产业前景,3D IC相关概念的影响力业已“破圈”,甚至在A股市场还催生了所谓的“Chiplet板块”,反映出外界对大陆相关厂商的期待之高。

与这样的期待相呼应,大陆厂商在相关领域也已积极布局,以创建芯粒间互连行业标准为宗旨的UCIe联盟中,目前就已吸纳了包括长电科技、通富微电等在内的十余家大陆地区会员。

不过,3D IC或许一如千禧年之初勃兴的SoC理念,尽管其所揭示的增量市场空间看似广阔,先发厂商与后来者的身位差距也看似接近,但新形态产品的基础技术与潜在客户资源,依然相当程度上掌握在传统巨头手中,因此对于大陆厂商而言,增量机会往往“看到”却不容易“吃到”,与其醉心于“换道超车”的愿景,更重要的课题或许是怎样避免被优势厂商加速甩开。

不可否认,目前大陆厂商在3D IC所需的TSV、减薄、键合等关键技术上已经有一定建树,但是3D IC产品要从概念具体落地,实现大规模产业化,除了埋头攻关关键技术,大陆厂商还必须通过对EDA工具的认证推广,打造外部设计公司与制造、封测企业之间的“接口”,在3D IC对芯片逻辑设计、物理设计、制造、封装提出更紧密协同要求的情况下,这样的做法尤其必要。

芯华章科技首席市场战略官谢仲辉就向集微网表示,最近火热的Chiplet概念包含了很多EDA相关的新技术:“比如说跟制造相关的包括封装里面功耗分析、散热分析等,Chiplet芯片的设计验证也对传统EDA提出了新的要求。特别是在验证技术和工具方面,实际上已经成为Chiplet发展的瓶颈之一。目前,Chiplet还以单一公司完成全系统为主,但未来多厂商合作的新型Chiplet模式会把传统SoC流程打破,并在IP建模、互连架构分析等系统级性能(Performance)、功耗(Power)和功能(Function)验证方面,提出新的验证需求,而不仅仅是解决了制造问题,就能实现全新的Chiplet产业结构。”

从这个角度看,联电此次携手西门子无疑显示出了“大厂”的老道,联电方面负责人郑子铭(Osbert Cheng)就谈到,“我们共同的客户对高性能计算、RF 和 AIoT 等应用的 3D IC 解决方案越来越感兴趣,与西门子的合作有助于加快其集成产品设计的上市时间。”

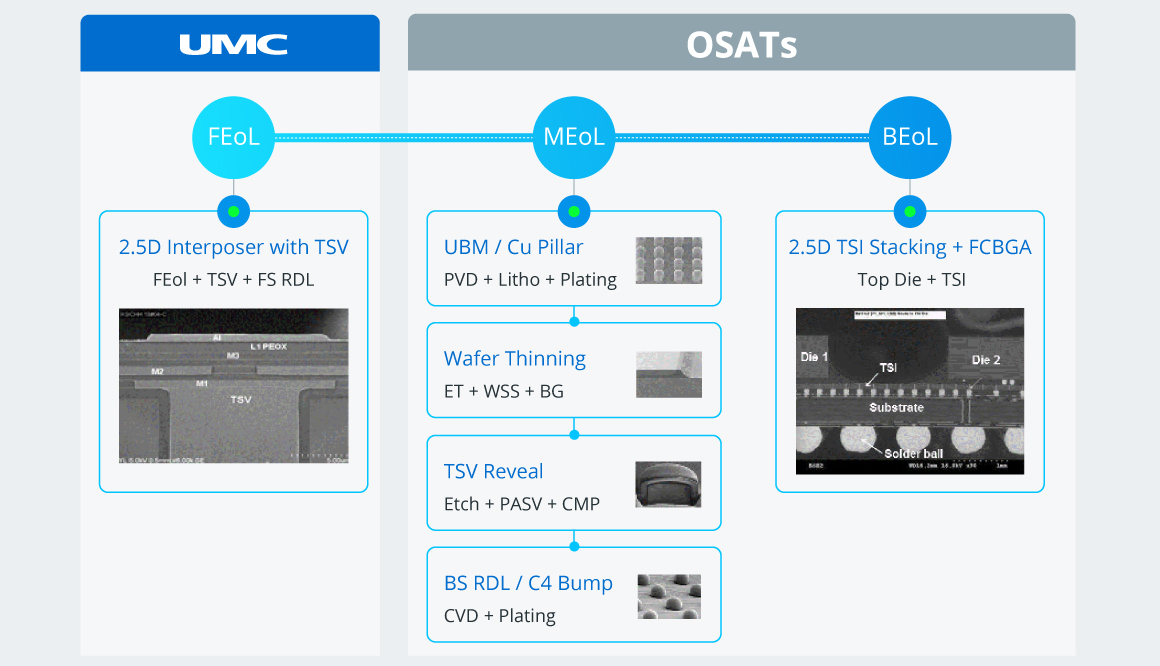

值得一提的是,联电早在2013年即推出过3D IC产品,由联电完成TSV制作,在合作OSAT厂商完成键合、减薄、露出等工序,而此次联电推出混合键和工艺,无疑显示出向中道、后道制程进一步扩展布局的意图。

3D IC开辟国产EDA新机遇

相较从前道环节向后扩张的联电等代工厂,大陆在3D IC技术研发上往往以从后道向前布局的封测企业更为热心,而不少封测企业在传统产业生态下,还习惯于通过自建团队和内部工具为客户进行简单的电、热、力特性仿真分析,以客户为中心的设计服务流程、工具、体系建设相对滞后。

一位国内EDA业界人士也向集微网表示,3D IC制造封装技术上大陆厂商“差距也不是那么大,但是确实在这个设计平台上面是有一些差距”。

该位人士分析,导致这一现状的原因一方面是大陆厂商面向的客户群体中,有相关需求的客户较少;另一方面,国内面向3D IC的商业EDA工具链也尚不完善。

事实上,即便在全球范围内,尽管目前已有多种单一工具可用于设计3D IC,但设计团队相当程度上仍然需要自行摸索设计方法、整合开发流程,积累经验数据,很难达到理想中的开发效率。单一工具在架构设计、布局规划、物理实现、参数提取、分析仿真、测试验证等各环节上依然处于较早期发展阶段,存在一系列有别于SoC的艰巨技术挑战,3D IC高密度堆叠的特征,也决定了其在初始设计阶段就需要来自OSAT乃至PCB等跨领域工程师的深度协同,以实现全局优化。

有鉴于EDA生态对3D IC走向大规模产业化的关键性意义,大陆厂商在这一领域理应有所作为,而3D IC设计方法学和工具链未臻完善的现状,对于本土EDA厂商也创造了一些细分机会。

立芯软件科技CEO潘培琛在接受集微网采访时表示,3D IC所需要考虑的物理因素更为复杂,对EDA工具提出了新的需求,例如IC/封装的协同优化,TSV通孔、硅中介层等的引入都会产生新的约束,需要着眼于系统整体性能进行综合;再如不同裸片高密度细节距互连,对于布局及布线规划也需要开发新的工具以实现最优化。

潘培琛指出,从客户角度看,3D IC设计人员当然会希望将所需的功能集成在同一个设计环境,单点工具之间还需要有统一的数据格式、接口,从而保证设计意图与数据传递的一致性,本土EDA厂商可以发挥在单一工具上的竞争力,借助统一标准实现联合。

采访中,潘培琛还分析了3D IC对EDA/IP商业生态的深远影响,当硬IP成为物理形态的chiplet,将有助于更多系统公司、IT公司踏足IC设计,直接采购集成chiplet有望成为代工厂流片的替代选择,而作为裸片/芯粒的供应方,一部分芯片公司可能向一站式解决方案平台的方向演进,通过向客户提供经验证的base die以及其上丰富的自有或第三方功能芯粒组合,进一步降低客户业务启动门槛。以AMD公司的Infinity Architecture模块化架构为例,就规划在保留CPU、GPU核心的情况下,允许客户引入其自研或第三方功能模块,快速实现定制芯片开发,这符合很多互联网大厂在数据中心业务上的需求。

不过新的商业生态、商业模式终点虽然已形成一定程度的共识预期,但产业结构重塑的具体路径仍然充满未知,潘培琛就认为,从IP到IC设计,未来以何者为核心重构商业模式尚难预料,摸索尚需时日,这可能也正是产业变革期百舸争流的魅力所在。

结语

总体而言,随着传统SoC方法暴露出越来越多的局限性,产学研用各方面的变革合力,正推动3D IC技术与商业模式实践不断积累,日益迫近大规模产业化的爆发点,联电等成熟制程代工厂的实质性布局,正是其生命周期临近新阶段的明显信号,在这一方兴未艾的领域,已经具备更扎实基础的中国集成电路产业界,当有更大的担当与作为。(校对/武守哲)

登录

登录