RDL技术大揭秘:决胜扇出型板级封装的利器

从晶圆代工厂、封装厂到IC设计公司和系统厂商,都开始将先进封装作为突破摩尔定律的一个方向。先进封装作为晶圆制造的后道工序,在持续压缩芯片体积、提高加工效率、提高设计效率和减少设计成本方面不断发挥重要作用。

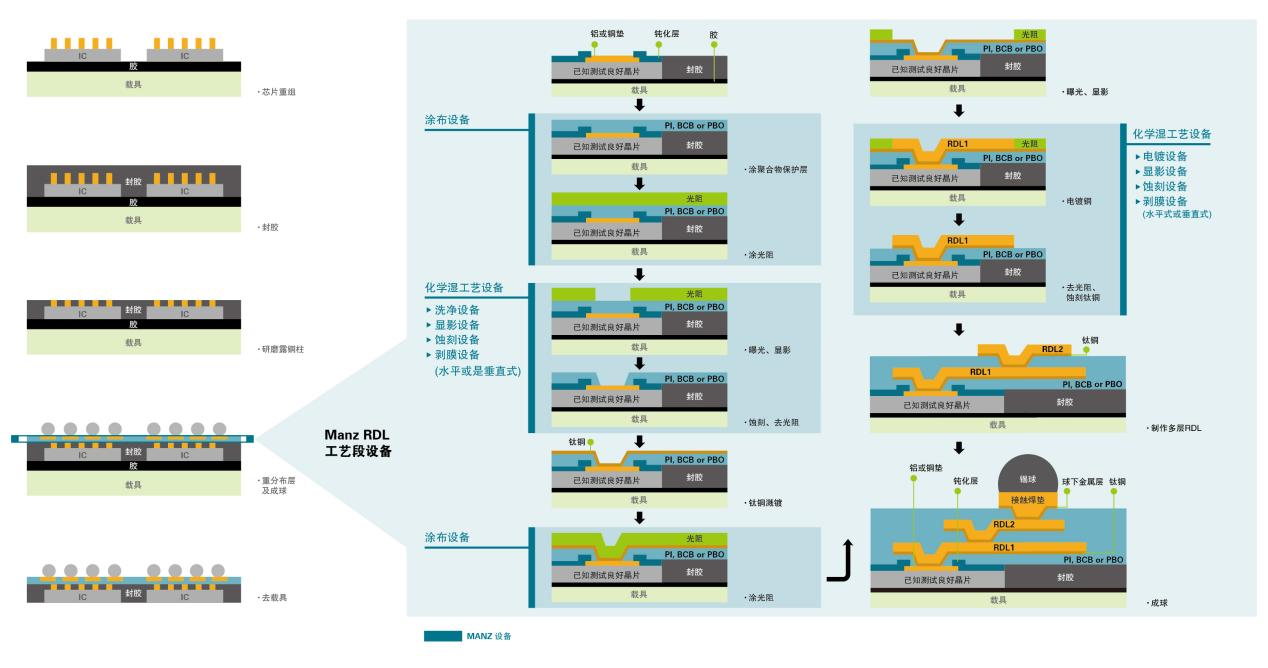

相比于传统封装,先进封装具有提升芯片功能密度、缩短互联长度和进行系统重构三大功能。这其中,RDL(Re-distributed layer,重布线层)技术的运用功不可没。也正是这项技术的兴起,使得封装厂得以在扇出型封装技术上与晶圆厂一较高下。

先进封装催生RDL

RDL是将原来设计的芯片线路接点位置(I/O pad),通过晶圆级金属布线制程和凸块制程改变其接点位置,使芯片能适用于不同的封装形式。

高精密设备制造商Manz亚智科技技术处长李裕正指出,如何将尺寸极小但功能强大的芯片放到印刷电路板上做成一个系统,需要封装技术进一步发展,必然依赖互联技术的微缩化。而RDL可以把不同种类的芯片连接在一起,所以是一个非常重要的互联技术。

RDL的优势主要有三点:首先是芯片设计者可以通过对RDL的设计代替一部分芯片内部线路的设计,从而降低设计成本;其次是采用RDL能够支持更多的引脚数量;第三是采用RDL可以使I/O触点间距更灵活、凸点面积更大,从而使基板与元件之间的应力更小、元件可靠性更高。

扇出型封装的成熟促进了RDL的发展。在扇入型封装中,RDL只能向内走线,当I/O数量达到200左右,层间间距在0.6mm时,往往就力不从心了。但在扇出型封装中,RDL既可以向内走线,也可以向外走线,从而可以实现更多的I/O,以及更薄的封装。

扇出型封装又分为扇出型晶圆级封装(Fan-Out Wafer Level Packaging;FOWLP),以及扇出型面板级封装(Fan-Out Panel Level Packaging;FOPLP)。两者虽工艺路线及应用不同,但皆可让产品达成轻薄外型。

厦门云天半导体科技有限公司董事长于大全表示,FOPLP技术的雏形是埋入基板式的封装,将一些无源器件或功率器件埋入在基板里面进行RDL互连,形成一个小型化的解决方案。随后业内发现相比FOWLP,它的封装尺寸更大,成本更低,很快就成为封装领域的研发热点。

FOWLP擅长于CPU、GPU、FPGA等大型芯片,FOPLP则以APE、PMIC等为主。通过RDL技术将不同的芯片整合在单一封装体中,可以使FOPLP实现更细线宽线距,达到与FOWLP相同的效果。

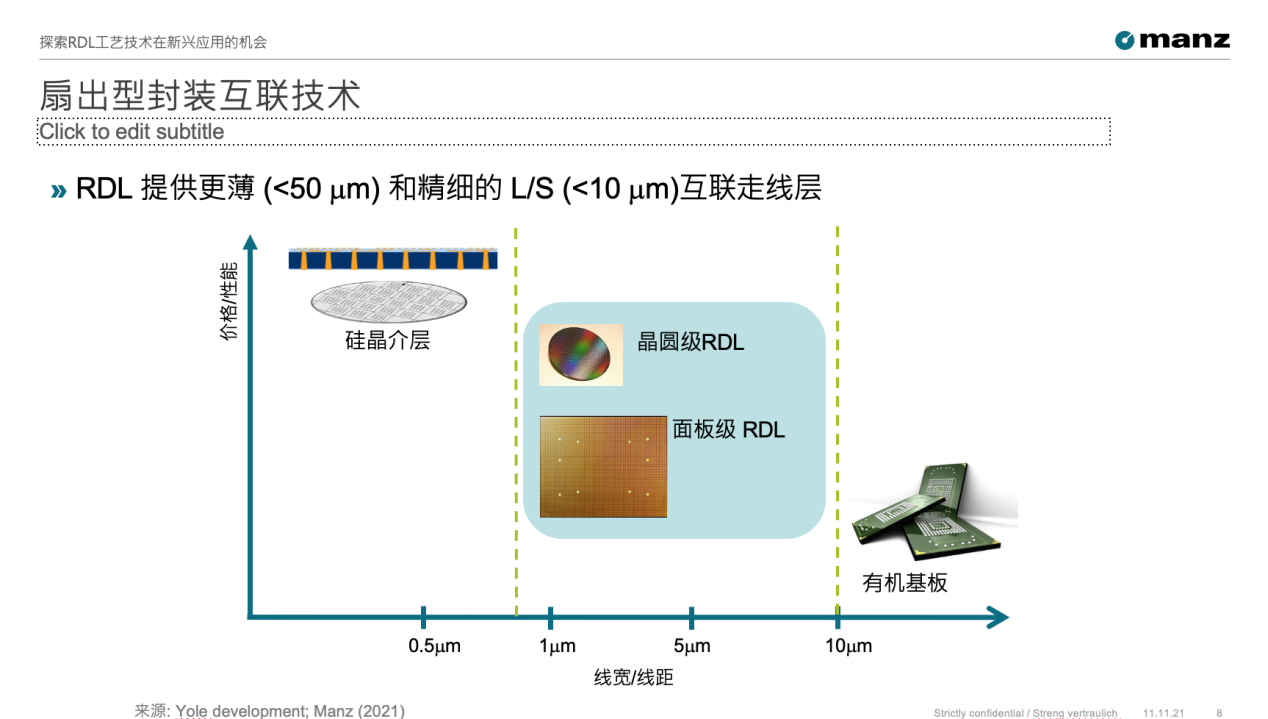

李裕正表示,RDL工艺制作的线宽符合晶圆和板级封装1~10μm之间的范围。同时,RDL层使用了高分子聚合物(Polymer)为基础的薄膜材料来制作,可以取代硅中介层跟封装载板,不仅省下大量成本,也让芯片的封装厚度明显降低。

以工艺细节的演进来看,RDL的出现也是一个必然现象。深圳中科四合科技有限公司 CTO丁鲲鹏表示:“晶圆上的焊盘大部分是铝焊盘,无论是做晶圆级封装还是板级封装,因为铝金属不易做后续处理,都需要用另外的金属来覆盖铝,RDL就应运而生。”

于大全认为RDL研发占比会在先进封装中进一步提升,“像Wire bonding在传统封装里的应用一样,未来RDL在芯片封装里肯定会得到更多的应用。”

应用爆发带来RDL进一步扩展

伴随着工艺成熟度不断提升,RDL应用空间正在进一步拓展。

首当其冲的就是在异构集成中的应用。这种将不同工艺单独制造的芯片封装在一起的工艺,要通过RDL来进行I/O的变换,最终实现多芯片的堆叠。当接下来几年出现外观、性能、功耗和完整性更高水平的异构集成时,RDL就是不同芯片之间相互通信的最好实现途径。

其次是采用SMT技术的被动元器件,如果要适应系统微缩的趋势,就会将RDL整合到工艺中,形成一个系统电路。

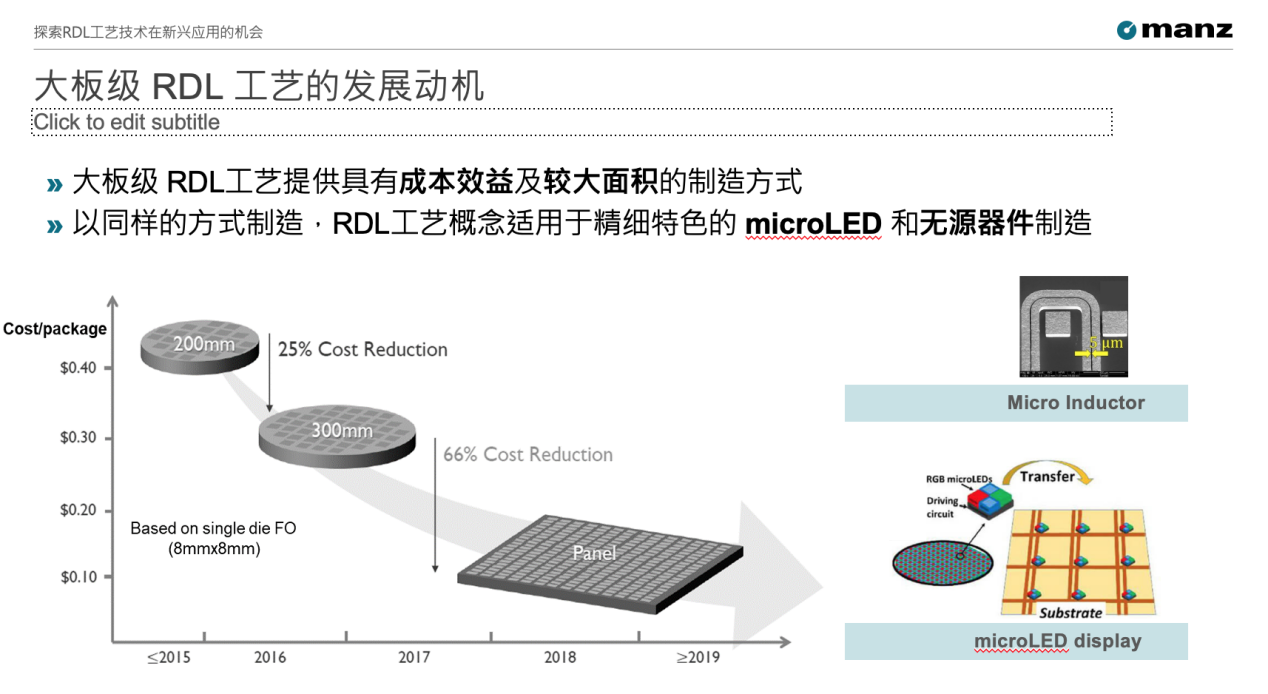

再者,mini LED或Micro LED的封装也适合采用RDL。这些应用多采用类似IC一样的载板进行封装,同样面临材料短缺的困境。当采用板级RDL之后,就可以制作高品质的精细线路,形成一个大面积的面板,从而大幅降低成本。

李裕正特别指出,板级RDL工艺提供具有成本效益及较大面积的制造方式。以同样的方式制造,将RDL工艺适用于micro LED和被动元件制造,相比FOWLP(300mm晶圆,芯片尺寸8mm×8mm)可降低66%的成本。”

从这点也可以看出RDL对FOPLP的重要性。如果充分发挥RDL的特性,FOPLP将具有显著的成本及效能优势。要知道,FOPLP面积使用率>95%,FOWLP面积使用率则<85%。

FOPLP如今面临了极其难得的发展机遇。根据Yole的报告,5G、AI和IoT的发展将推升FOPLP全球产值在2024年达457百万美元,未来5年的年复合成长率高达30%。如果再叠加FOWLP的应用空间,RDL前景将不可限量。

同时,当前主流的RDL线宽仍在5-5μm及以上,当5G需求爬坡以及存储器带宽需求变高时,将推动市场对3-3μm和2-3μm及以下的更小CD(关键尺寸)的RDL需求。Yole报告指出,云基础设施、5G、自动驾驶和人工智能革命将塑造未来十年的封装趋势,密度更高的多层RDL积层结构方法将成为有助于在系统层面满足“超越摩尔”的解决方案之一。

以设备精细化应对RDL未来挑战

扇出型技术主要可以分为三种类型:芯片先装/面朝下(chip-first/face-down)、芯片先装/面朝上(chip-first/face-up)和芯片后装(chip-last,有时候也称为RDL first)。前面两种chip first需要在扇出表面做精细布线,RDL first则需要在晶圆和面板(载具)上线做精细布线,布线能力会更高。封装厂商如果要做出精良的扇出型封装,只能采用RDL first制程。

于大全认为,未来FOPLP若全面走向RDL First,需要的RDL是非常精密的,技术挑战也更高。比如,铜互联要实现微纳或者纳米级别的组织调控,采用自由取向的再布线技术,对RDL的研发也提出了很苛刻的要求。

他进一步指出,从FOPLP所对应的产品类型来看,所需要的RDL还没有FOWLP那么精密,这也跟其当前所用的设备和工艺关联度很大,但要实现高精度的布线,需要材料、设备进一步的升级。

在当前的扇出型封装中,有一个很大的挑战就是如何形成高膜厚均匀性且高分辨率的RDL层,这是对封装厂的考验,更是对设备厂商的考验。

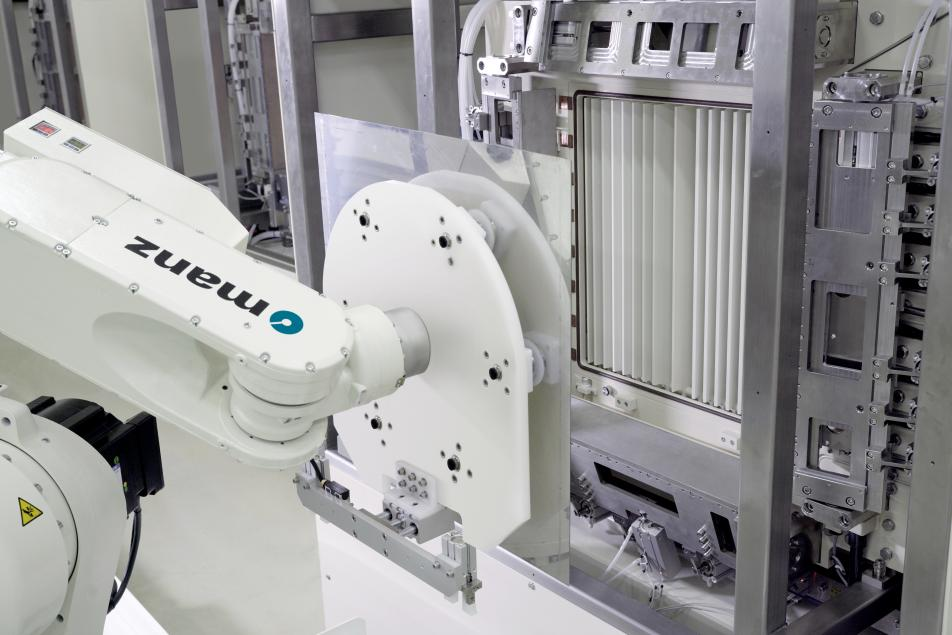

对于此,李裕正认为设备厂商应该从细节处着手,“以Manz亚智科技为例,考虑到基板已经很重,专门开发了无治具的模组,可以让基板直接密合到反应槽上,而不需要另外承载的治具,大幅缩减了系统的重量。”

Manz亚智科技的电镀无治具模组

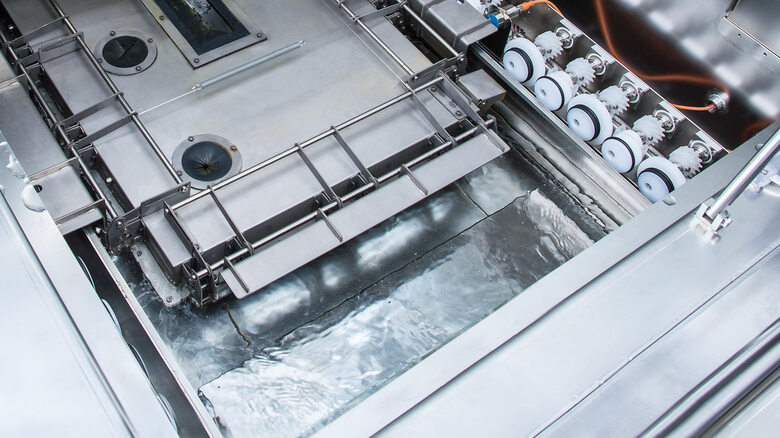

李裕正表示:“Manz亚智科技还开发了专利技术,可以让垂直电镀在反应完成之后,快速地净空圈子,使电镀均匀性大于90%。此外,在细线路制作上面,也可以提供给客户一些特殊需求的设计制作。”

Manz亚智科技用于RDL的湿法制程设备

李裕正认为板级RDL所面临的其他挑战,如基板增大带来的重量增加,铜导线制程在生产中的问题等,都可以通过精细的设计来解决。比如,Manz亚智科技提供了特殊的设计来处理沉重的基板和材料的翘曲。另外,在容易与基板接触的部分,Manz亚智科技通过特殊的处理,可以在短时间内完成显影、剥膜及蚀刻的部分,使均匀性达到90%以上。

Manz亚智科技的RDL制程设备解决方案

不过,当RDL走向更细的互连线路、更多层数的立体堆叠时,挑战还是会继续产生。所以如其他先进封装技术一样,RDL和FOPLP的技术演进也将是一个长期的过程。在这个过程中,封装厂要不断优化工艺细节,设备供应商要不断根据需求改进设计,两者携手一致方能将技术推向新高度。

*此内容为集微网原创,著作权归集微网所有,爱集微,爱原创

13个创业团队巅峰对决!集微紫琅杯IC创业大赛圆满收官

专利申请

专利申请

知识产权质押融资

知识产权质押融资

专利地图分析

专利地图分析

版权登记

版权登记

集成电路布图设计

集成电路布图设计

商标交易

商标交易

商标申请

商标申请

专利交易

专利交易

专利无效

专利无效

热门评论