(文/清泉)万物智能互联的时代,催生了大量的数据产生,也对计算提出了新的挑战,业界预计,到2025年对计算性能的要求将有千倍级增长,而要满足这一需求,我们需要在每个技术领域,实现至少4倍左右的摩尔定律提升,这些领域包括制程工艺、封装、内存和互连,而架构是将它们与软件结合起来的关键要素。

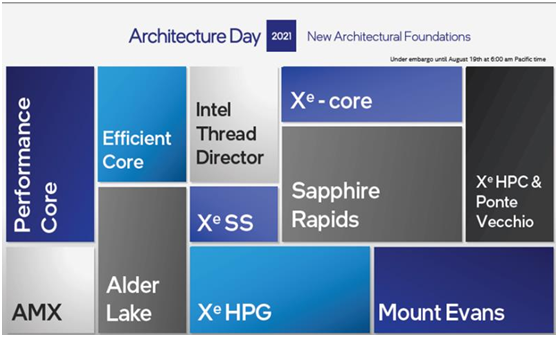

日前,英特尔架构日上宣布推出了两款下一代X86内核微架构:能效核(E-Core)与性能核(P-Core),同时还展示了用于客户端与视觉计算领域的新架构Alder Lake与Xe HPG 。除了在架构上的新进展,英特尔还宣布了多款SoC芯片产品,包括下一代至强可扩展处理器Sapphire Rapids、全新的基础设施处理器(IPU)Mount Evans、以及面向百亿亿次计算的GPU——Ponte Vecchio和全新游戏独立显卡SoC英特尔锐炫(Intel Arc)产品。其中Ponte Vecchio将采用台积电N5和Intel 7制程工艺,展示了其今年初发布的IDM2.0战略的重要一环。

性能混合架构成未来计算趋势

英特尔此次推出的能效核与性能核微架构是X86架构近十多年来的重大变革。

英特尔研究院副总裁、英特尔中国研究院院长宋继强

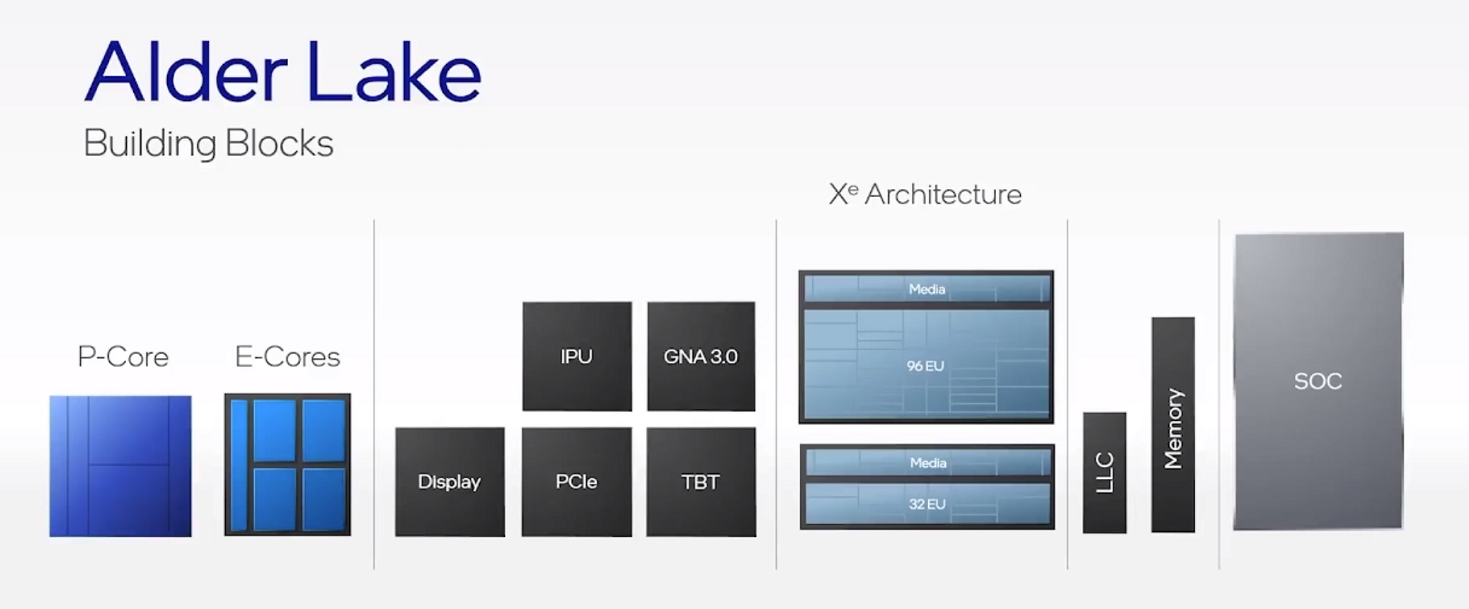

英特尔研究院副总裁、英特尔中国研究院院长宋继强解释说,“能效核专注于提供足够高的通量,同时保证更优化的功耗。相比英特尔最多产的CPU内核Skylake,在单线程性能下,能效核能够在相同功耗下实现40%的性能提升,或在功耗不到40%的情况下提供同等性能。同时,还可以灵活组合实现具有不同性能伸缩能力的产品。性能核则专注于提高计算密度,能够在很少的延时内完成任务。这两种不同的内核,在硬件线程调度器的整合下,可以去组合成不同的新产品。”

这其中,将能效核和性能核无缝衔接在一起的关键是硬件线程调度器,它可以从开始就动态、智能地分配工作负载,从而优化系统以在真实场景中实现更高的性能和效率。在硬件线程调度器与操作系统的无缝配合下,可以实现在合适的时间把合适的线程分配给合适的内核。

基于这一创新技术的首个性能混合架构Alder Lake,可满足从超便携笔记本到高性能台式机的客户端对性能、功耗等的广泛需求。

宋继强认为,通过E-Core和P-Core将奠定未来十年在SoC架构上提供性能和能效出色的产品组合基础,而这一在CPU领域全新的微架构平台以及混合架构代表了未来计算产业发展的一大趋势。

异构集成将向多维度扩展

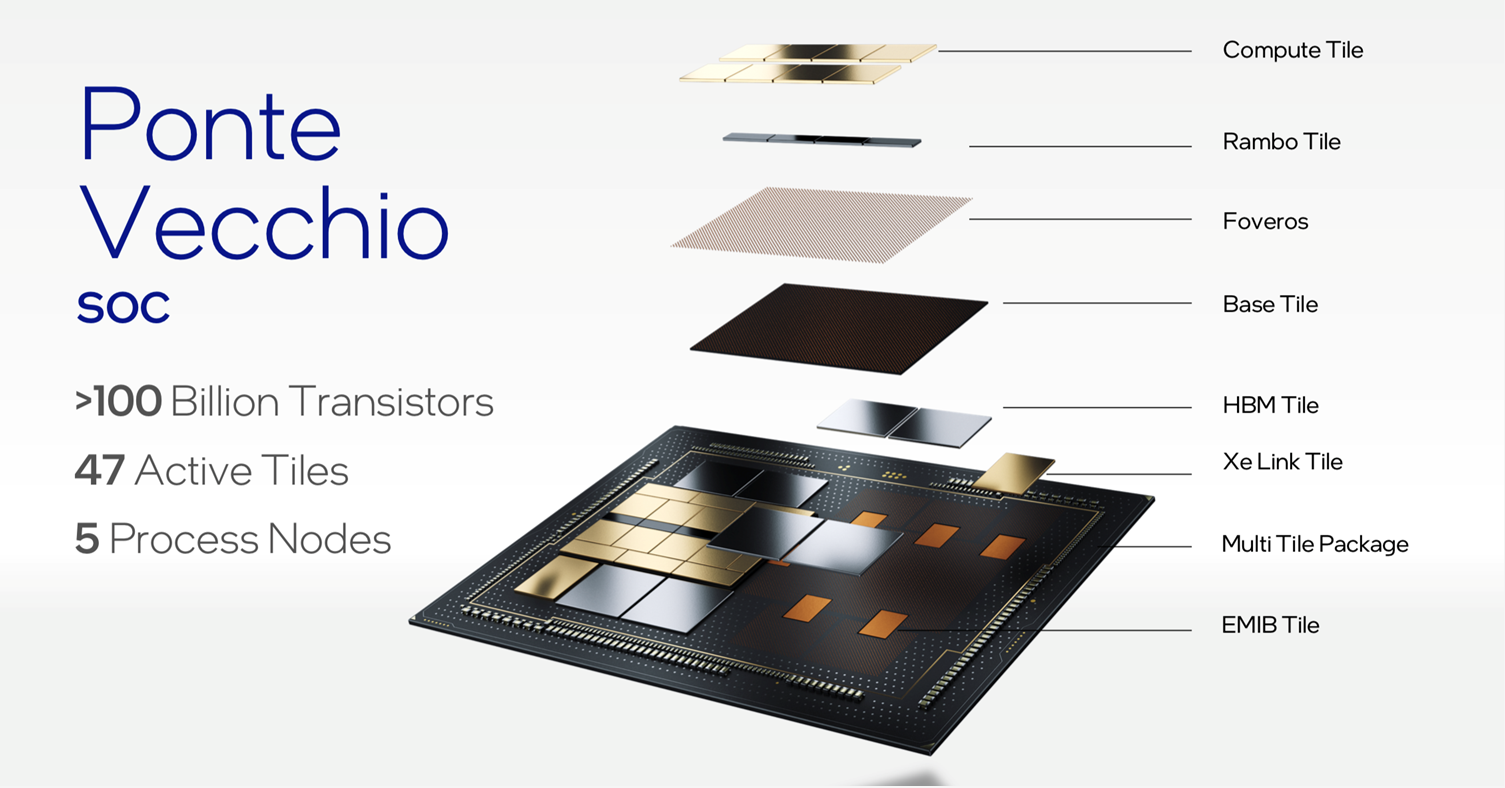

在本次架构日上,英特尔宣布了迄今为止最复杂的一款SoC Ponte Vecchio,深刻诠释了超异构集成在多维度的扩展。

据宋继强介绍,“Ponte Vecchio内部集成了5种不同类型的晶片,有的做内存,有的做计算,有的做互联.....这么多的晶片通过英特尔变革性的EMIB技术以及Foveros技术封装整合在一起,共集成了1000亿个晶体管,是英特尔迄今为止最复杂的一颗SoC。”

Ponte Vecchio不仅采用了多种先进的半导体制程工艺、英特尔变革性的互联封装技术,同时使用了台积电N5和Intel 7制程工艺制造,真正实现了跨架构、跨供应商、跨工艺制程的集成。

宋继强认为,“这是异构集成的一个代表作,也是英特尔践行IDM 2.0战略的绝佳示例。”

除了Ponte Vecchio,英特尔此次架构日上发布的多款SoC,例如Sapphire Rapids、Mount Evans以及独立显卡SoC英特尔锐炫等,无不展示着这种异构集成的趋势。正如英特尔CEO帕特·基辛格在架构日上所讲:“英特尔已经开发出了许多架构和平台,在各个级别和维度上的异构计算,从子芯片、主板、系统到数据中心,从边缘和终端设备到网络、再到云,一切设计旨在智能地使用最佳计算资源,即用最优架构来完成每项任务。”

IDM2.0战略进一步扩大英特尔代工合作

英特尔CEO帕特·基辛格上任即宣布的IDM2.0战略开始进一步落地实施,此次架构日上,英特尔宣布其Xe显卡产品将首次利用台积电先进制程工艺生产。这就像设计师为其工作负载选用合适的架构一样,英特尔也会为架构选择最适合的制程节点,其独立显卡产品采用代工厂的制程节点,就是恰当之选。

宋继强强调,采用第三方代工,用不同的制程来生产多元化产品,这是IDM2.0策略中的关键一环。未来英特尔将不断演进IDM2.0战略,深化和扩大与主要代工厂的合作关系,选取不同的节点平衡和优化配置。

事实上,数十年来,英特尔一直都在使用外部代工厂。目前英特尔20%的产品是交由外部代工厂生产,其中,与代工厂合作生产过的产品包括Wi-Fi模块、芯片组,以太网控制器等特定产品线。IDM2.0模式的演进将进一步扩大英特尔的代工合作。

宋继强总结说,英特尔具有从架构、封装、制程、软件等的全方面创新能力,还具备大规模生产制造能力,未来执行战略规划的速度将不断加快,能力将不断拓展。(校对/Lily)