芯观点──聚焦国内外产业大事件,汇聚中外名人专家观点,剖析行业发展动态,带你读懂未来趋势!

从1947年第一个晶体管问世算起,半导体技术一直在迅猛发展,现在它仍保持着强劲的发展态势,继续遵循摩尔定律指明的方向前进,大尺寸、细线宽、高精度、高效率、低成本的IC生产,正在对半导体产业链带来前所未有的挑战。

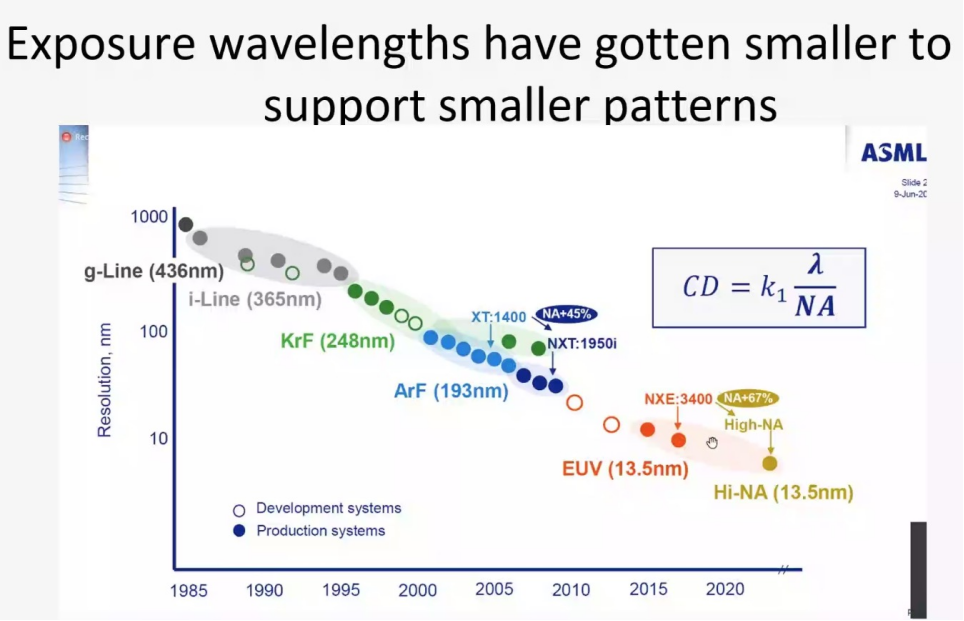

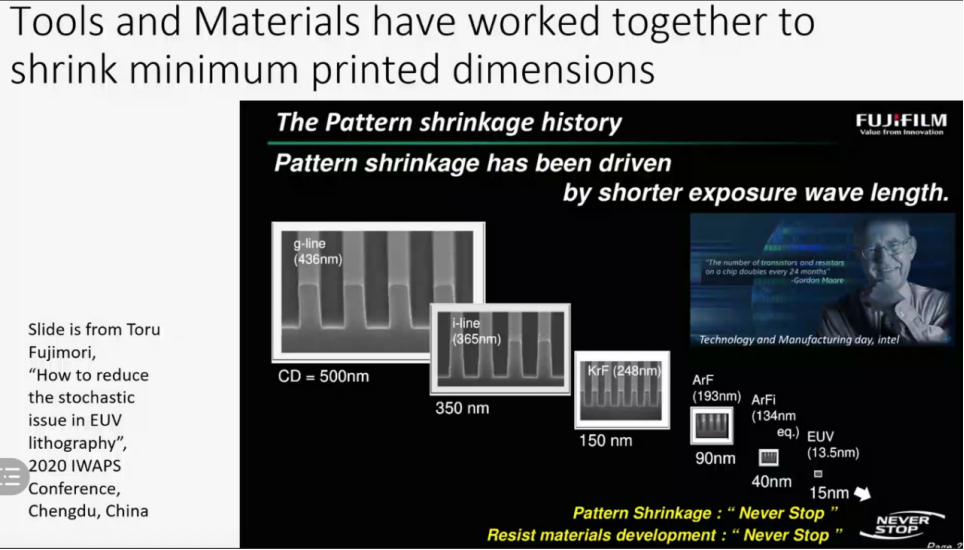

集成电路在制造过程中经历了材料制备、掩膜、光刻、清洗、刻蚀、掺杂、化学机械抛光等多个工序,其中尤以光刻工艺最为关键,决定着制造工艺的先进程度。随着集成电路由微米级向钠米级发展,光刻采用的光波波长也从近紫外(NUV)区间的436nm、365nm波长进入到深紫外(DUV)区间的248nm、193nm波长。目前大部分芯片制造工艺采用了248nm和193nm光刻技术。目前对于13.5nm波长的EUV极端远紫外光刻技术研究也在提速前进。

可以说,随着芯片集成度的提高,对光刻技术提出了越来越高的要求,而光刻技术的演进,在某种程度上也反映了半导体技术的发展路线。上世纪中叶,IEEE电子和电子工程师协会设立了ITRS组织,该组织每年都会发布一份半导体领域中技术路线图——ITRS(International Technology Roadmap for Semiconductors)。但在2017年,IEEE停止更新ITRS,并将其重新重命名为IRDS,他们认为这样可以更全面地反应各种系统级新技术。

IRDS路线图光刻委员会主席、厦门大学嘉庚创新实验室产业运营平台科技总监,厦门大学半导体科学与技术学院客座教授Mark Neisser最近对光刻技术与半导体路线之间的关系进行了详细解读。

Mark Neisser指出,当前的IRDS路线图预测了未来15年的行业需求,并指出了关键挑战和技术选择。他表示,摩尔定律的意义在于,指示了“提高每个芯片中的晶体管数量降低了计算成本”的路线,在数十年被摩尔定律“规划”的半导体产业发展过程中,它也逐渐被扭曲为自我实现的预言:(芯片设计公司)竞争对手总是试图跟上摩尔定律预测的创新步伐,一旦某一个竞争者可以达到这个速度,其他所有的人都必须努力达到这个速度。一旦跟不上节奏,你的成本就会高于竞争对手的成本而在竞争中落于下风。与此同时,设备、工具、材料、供应商、软件都必须改进,以实现更高的晶体管密度和更低的成本。

其中,随着工艺演进,光刻波长经历了几次大的更迭,i-line时期使用的波长为365nm,KrF时期使用的波长为248nm,ArF时期使用的波长为193nm,进入EUV时代后使用的波长为13.5nm。每一代光刻技术的革新都对光刻机等设备和材料提出了新挑战。

如上图中的光刻公式,决定光刻分辨率的因素有三个:1.选用更小波长(���)的光源,2.通过增大投影入射角及折射率更高的界面材料来提高数值孔径NA值,3.并通过分辨率增强技术以获取更低的工艺因子k1。

历史上光刻工艺中的成像改进,都伴随着工具改进、材料和工艺改进以及多重成像(multiple patterning)。

工具改进,包括使用更小的波长以获得更高的分辨率;改善对焦控制和套准(overlay)控制;更高数值孔径(NA)的镜头;更好的控制系统、照明系统;掩膜和芯片设计的改进等等。

材料和工艺改进,包括抗放射涂层材料;改变印刷临界尺寸的收缩材料和线宽修剪材料;用于新一代光刻波长的光刻胶;刻蚀放大材料;光刻胶清洗材料和涂层;CMP工艺以及突破曝光工具分辨率极限的多重曝光工艺等。

以CMOS器件变迁历史为例。最初,CMOS器件越小性能越好,更小的尺寸意味着更快的导通,工作电压也更小。在某种程度上,尺寸缩小带来的副作用影响了器件性能,例如漏电流增加,寄生电容增加等。器件结构和工艺一直在改进以实现更小尺寸和更好的性能,包括隔离,栅极材料、漏极和掺杂图案等等,来达到更高的PPAC要求(PPAC,power, performance, area和cost)。

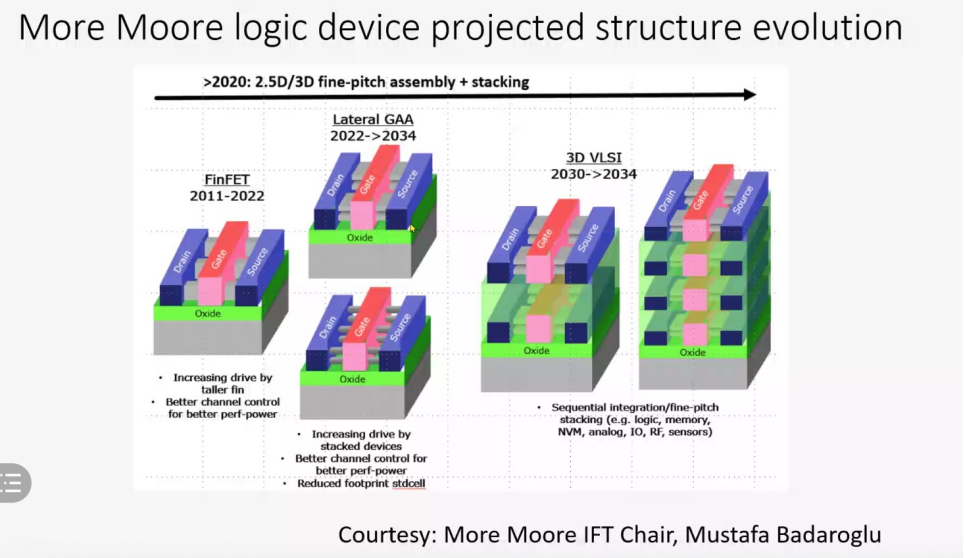

随着平面器件结构缩小尺寸已不能满足性能需求,三维的FinFET晶体管架构逐渐成为高性能逻辑标准器件,IRDS路线图预测高性能器件的晶体管结构将发生更多变化。

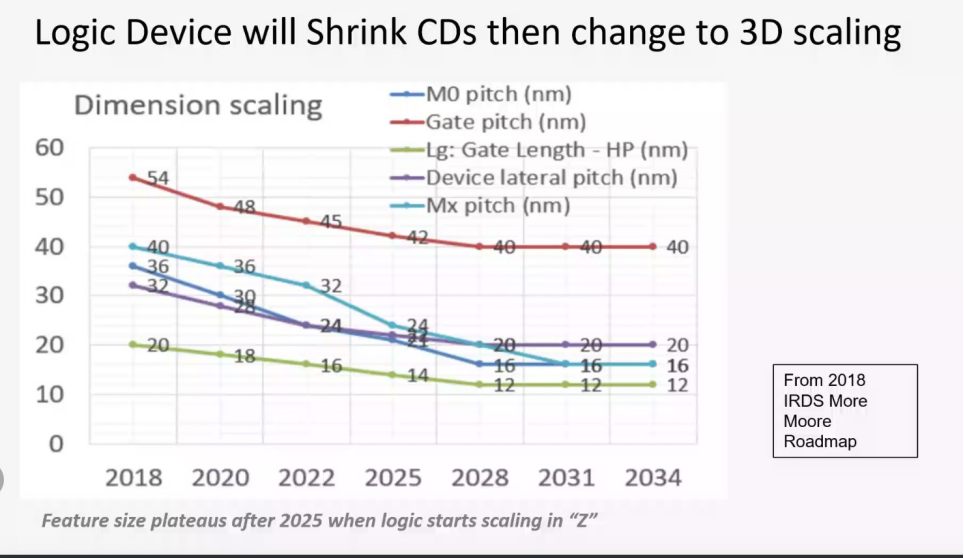

下图预测了未来逻辑器件结构演进方向,从当前的FinFET,到lateral GAA,再到3D VLSI等。逻辑器件从特征尺寸缩微逐步转变到三维缩微。存储器件将是率先发生这一转变的领域,并且闪存技术已经开始三维缩微。

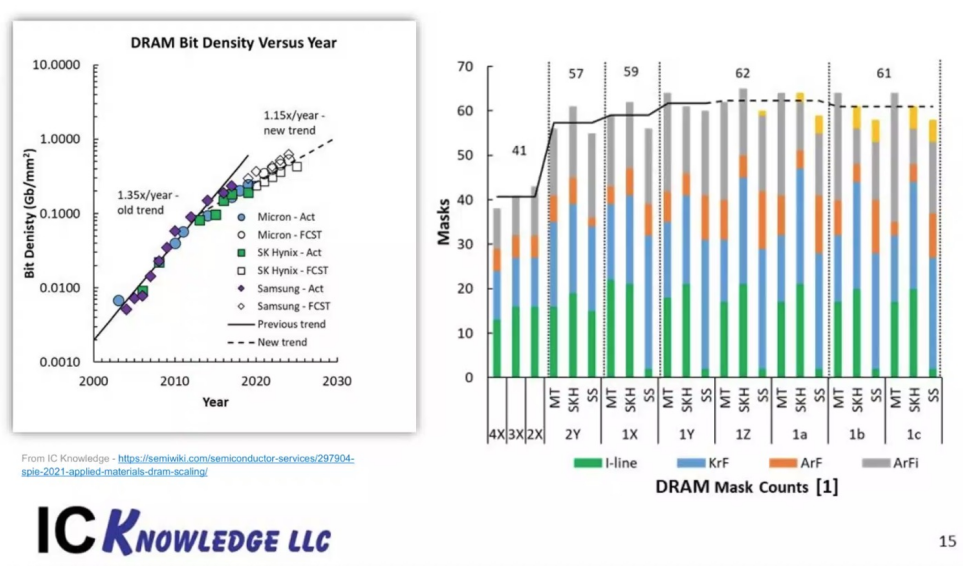

如下图,随着存储密度快速提升,由于存储单元太小而无法可靠地保留存储状态,且达到了纠错能力的极限,平面结构闪存已无法继续提升性能,基于三维缩放的3D NAND闪存开始成为主流。3D存储单元的体积比2D闪存要大得多,众多的层数也意味着可以实现比2D存储器件更多的存储密度,目前业内3D NAND闪存最高已达到176层,还将继续增加。SK海力士已经在讨论2025年达到500层,2030年800层的规划。

其他新型存储技术方面,英特尔和美光联合研发的3D XPoint开始量产,但是目标用途与DRAM不同,目前也还没有哪种存储技术能够取代DRAM或闪存,其他类型的存储技术只占据了市场的一小部分。

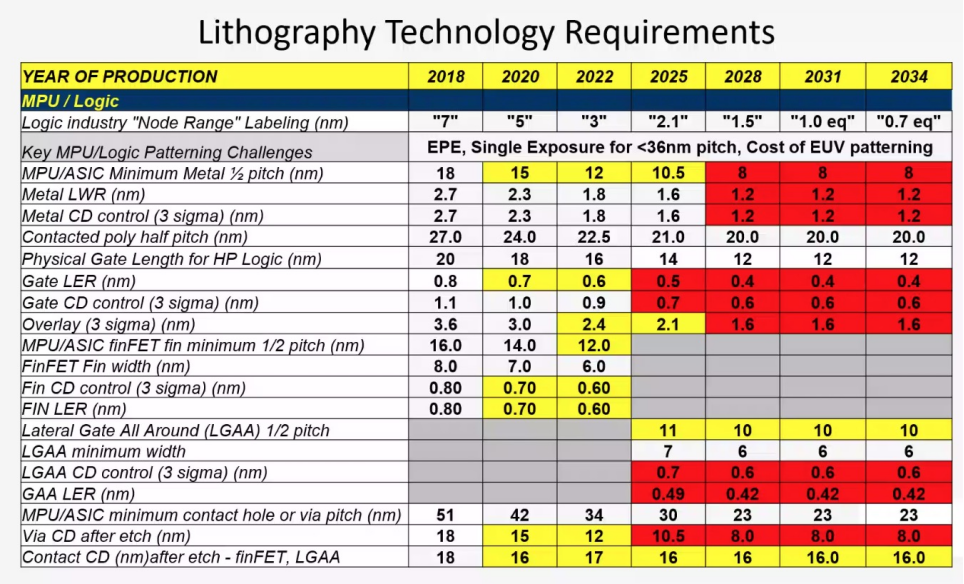

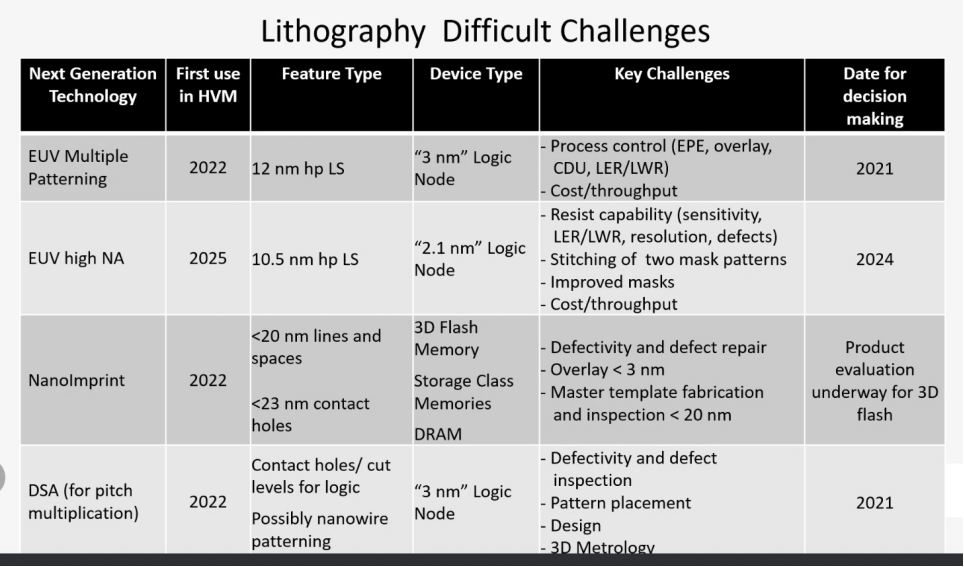

下图列出了2018年开始,7nm制程之后光刻技术的主要尺寸要求。IRDS据此给出了潜在的光刻解决方案选择,以及将面临的关键挑战。

几项光刻技术和面临的挑战

随着5nm工艺芯片进入批量生产,科研机构将倾向于研发下一代光刻技术,包括多电子束直写光刻机(MEB)、纳米压印技术(NIL)以及定向自组装技术(DSA)。其中,MEB被广泛应用于掩膜的制造,分辨率可达到2nm,未来将被用于在晶圆上直接刻画图形而不借助掩膜版。NIL分辨率极高可达2nm,用于制造特殊图形的模具、压印特殊图形。DSA则利用两种聚合物材料的定向生长进行加工,对于材料的控制要求高,生长缺陷大,目前还不能真正用于生产,但可兼顾高分辨率极高的加工速度需求。

纳米压印

其分辨率只与模版图案的尺寸有关,而不受光学光刻的最短曝光波长的物理限制。纳米压印有望用于制造例如闪存等成本敏感、可容错(defect-tolerant)的产品。该技术无需投影光学,但挑战包括缺陷和套准等。

DSA(定向自组装)

可以通过BCP(block co-polymer)实现间距致密化的目标,有望用于半导体量产。缺陷和设计是现阶段主要挑战。大约十年前,或许双重成像(double patterning)要比DSA要好一些,但是如今DSA具备更长远的发展潜力。

对LER/LWR(边缘粗糙度/线宽粗糙度)的要求已经来到分子水平,以至于到2022年,噪点将是一个关键挑战,对成像图案的质量影响非常大,进而会影响芯片的电气性能。化学和光的随机性会在已成像的光刻胶中产生噪点。下图中红点显示曝光后和烘烤前产生的个别酸。

在EUV中,光子撞击光刻胶发生反应且这一动作重复多次,这些过程充满不可预测性和随机性,可能会产生新的反应,也就是说EUV光刻工艺容易出现所谓的随机性,是具有随机变量的事件,这些变化被统称为随机效应。随机效应有时会导致芯片中出现不必要的接触缺陷或有粗糙度的图案,两者都会影响芯片的性能,甚至导致设备出现故障。在过去的几年中,这些问题在传统的光刻技术中基本被忽略了。但对于EUV而言,随机效应成为主要问题之一,越高级的节点,随机效应越严重。

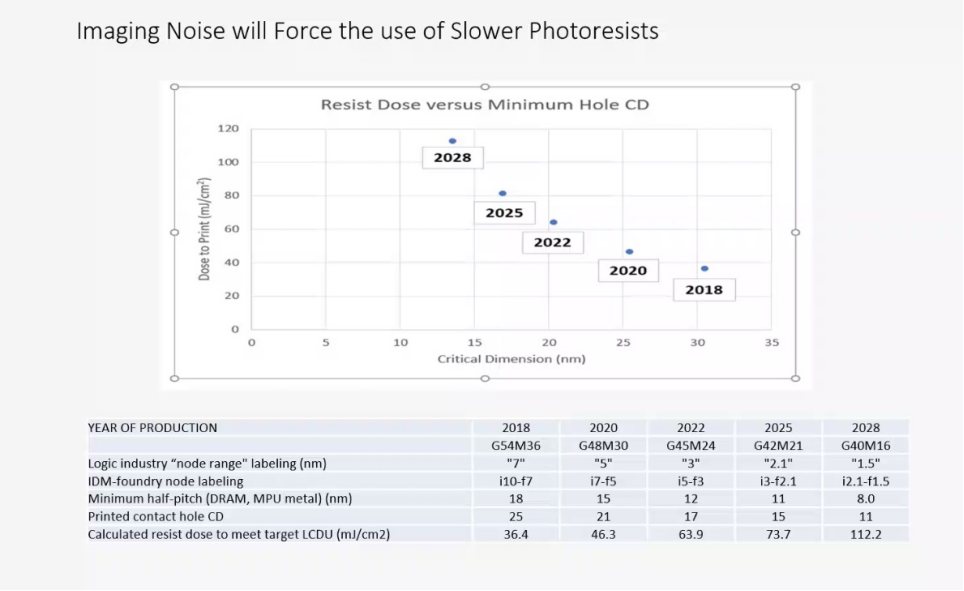

由于成像噪点的原因,不得不降低光刻胶的剂量,但是较低的剂量也意味着更少的光子,以及更高的随机概率。预计在未来两年内吞吐量将下降2.5倍。下图显示了光刻胶剂量和最小通孔直径之间的关系。

其他挑战,包括套准;可用的EUV掩膜防护罩需要在对比度、结构等方面继续改进;更小的临界尺寸和3D结构要求在薄膜沉积和刻蚀工艺进一步改善;更多的层数和工艺步骤对成本和良率带来的挑战等。

总结和建议

在十年内,预计晶体管尺寸将继续缩微,尤其是高性能逻辑器件将继续推动这一趋势。从长期来看,器件堆叠工艺将能够提供更高的性能,而挑战主要在于良率,工艺产能和成本等方面,当前光刻机的分辨率能力足以满足预计的需求。光刻工艺中噪点和缺陷是亟需解决的关键挑战,而摩尔定律也将在未来一段时间内继续发挥作用。

Mark Neisser对中国半导体产业也提出了几点建议。他指出,首先,需要以解决客户问题的方式进行创新。作为中国半导体制造商客户的中国公司,很多好的创新都是由客户需求驱动的,因此,并非所有这些创新都是遵循路线图的。例如,格芯近几年已经放弃了追逐路线图的尝试,现在也依然发展的很好。该公司通过SoI等其他途径来解决客户的芯片需求,而不仅仅是尝试模仿或跟随其他公司的脚步。因此,如果能够创造自己的专长,也能在技术贸易等领域处于更有利的地位,并以创新推动行业前进。此外,他还强调,要重视半导体领域的基础研究,从研究到出成果,开发以及制造之间,有5到10年的时间差,基础研究是长期而又非常必要的工作。

(校对/小山)