图源:eeNews

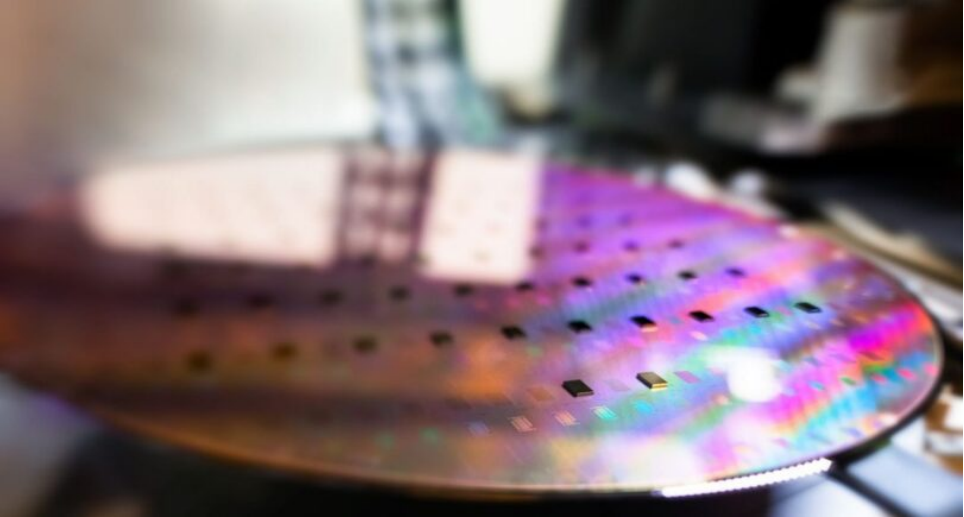

英特尔和法国研究实验室CEA-Leti优化了一种混合直接键合、自组装(self-assembly)制造流程,可以促进“裸片到晶圆”(die-to-wafer,D2W)键合的应用。

据eeNews报道,D2W混合键合工艺被认为是在晶圆衬底上结合存储器、高性能计算芯片和光子芯片的必要工艺,但它比晶圆对晶圆键合要复杂得多,具有较低的对准精度和较低的模组装吞吐量。

几年来,CEA-Leti一直在开发一种自组装方法,目标是大幅提高吞吐量和放置精度。新研发的技术可以提高对准精度,通过使用滴液对准目标晶圆上的裸片,将每小时制造吞吐量提高数千个裸片。

CEA-Leti 3D集成项目经理Emilie Bourjot表示,D2W自组装吞吐量提高至商业化规模克服了与裸片处理相关的两个主要挑战。“如果将自组装过程与拾取放置工具相结合,通过减少对准时间,可以提高产量,因为精确对准是通过液滴进行的。当自组装与集体裸片处理解决方案相结合时,由于所有裸片在同一时间粘合在一起,而无需在工艺流程的任何时间进行任何高精度放置,从而提高了产量。”

本周在2022年电子元件与技术会议(ECTC)上发表的一篇论文描述了一种技术,该技术利用毛细管力,这种力产生于表面最小化的原理,并在液体的情况下通过表面张力施加。

从宏观上看,液体倾向于使其液体/空气界面最小化,以达到能量最小化的平衡态。这种机制允许裸片在粘接部位的自对准。选择作为重新排列矢量的液体必须具有较高的表面张力,并且必须与直接键合相兼容。大多数液体的表面张力在20到50 mN/m之间,除了水,水的表面张力为72.1 mN/m,这使其成为使用亲水键合的自组装过程的优秀候选,水已经是一个关键的机制参数。

CEA-Leti开发了一个内部D2W系统,该系统在150 nm下显示出在各种裸片尺寸(8×8 mm²、2.7×2.7 mm2、1.3×11.8 mm2和2.2×11.8 mm2)下的平均偏差。相比之下,拾取和放置工具后粘接的1µm对准,以及700nm的最佳情况,而自对准工艺可提供低于500nm甚至低于200nm的后粘接对准。

该论文旨在鼓励组装设备制造商采用该技术。研究人员说:“自组装的许多方面仍然需要探索,只有当设备供应商开发一种适应的设备来自动化这一过程时,才能实现巨大的改进。”(校对/Aaron)