在上一篇文章芯片验证反内卷,搭载ML技术的高级校验工具让你躺赢中,我们提到Linting是一项非常重要的技术,多年来也取得了巨大的进步。如今,当代芯片设计所涉及的功能错误和设计问题多种多样,从RTL设计描述中的高风险编码实践,到设计投入生产后才会出现的复杂软硬件交互错误,都会对产品质量产生重大影响。

为了避免出现代价昂贵而又费时的设计返工或改版,开发者们不仅需要智能的Linting工具来尽早发现尽可能多的RTL问题,更需要一套预定义的、值得推荐的基础/高级版本Linting检查,以备不时之需。这一理念正是新思科技GuideWare™方法学的核心。

GuideWare™是我们为设计团队自主研发的一整套规则集,旨在加速完成Lint工作流程,帮助团队每次都能按时完成设计,而且这套指导规则集已经被业内许多领先的半导体公司所采用。

在本期文章中,我们将深入探讨以下几个问题:

-在汽车领域,是什么样的设计挑战推动了GuideWare的问世和研发?

-新思科技VC SpyGlass Lint的GuideWare在RTL早期阶段能够发现哪些设计问题,从而避免让开发者们等到综合或逻辑等价性检查阶段再进行不必要的迭代?

-重点介绍几个可以通过新思科技VC SpyGlass功能Lint分析工具发现的高级问题

GuideWare:一针见血指出问题

大家都玩过乐高积木吗?GuideWare方法学就相当于乐高的底座积木颗粒。通常我们要在开始拼搭结构前先选好底座积木,再选择用来加强基础结构的积木。使用GuideWare也是同样的道理,不同领域的用户可以在新思科技GuideWare规则集的基础上修改并建立自己的Lint方法学,利用业界最全面的设计专业知识和最佳实践知识库,实现用户指定的扩展。

当我们有一套可靠的设计方法学后,就相当于有了一个全面的分步Linting检查流程。客户在写完RTL代码后便可以立即使用。这种含有规则集的方法学文档可以作为团队的重要框架,确保他们在整个设计过程中保持风格前后一致,同时还能通过多核技术来加速运行时间。

不同应用的设计需求截然不同,所需的Linting检查也千差万别。以符合ISO 26262标准的汽车应用为例,汽车应用设计中需要确保不存在逻辑拥塞或大的多路选择器或延迟的级数很深等不良做法,通常汽车开发者倾向于采用模块化、可复用的设计方法学,而新思科技的GuideWare Lint Automotive正好可以满足这一要求。

新思科技VC Spyglass Lint采用“左移”的识别方法学,能够提前发现新思科技Design Compiler和Formality在实现流程中读取设计阶段报告的代码问题。通过使用VC SpyGlass Lint,开发者可在RTL早期阶段的等价性检查中就识别出复杂的验证问题,从而减少下游阶段的迭代。此外,我们还开发了专用规则集来发现仿真与综合之间的不匹配问题。

超越常规:功能Lint分析

功能验证的目标是在开发过程中尽早地发现尽可能多的问题。面对棘手的可移植性挑战,语义和语法检查一直都起着关键作用。

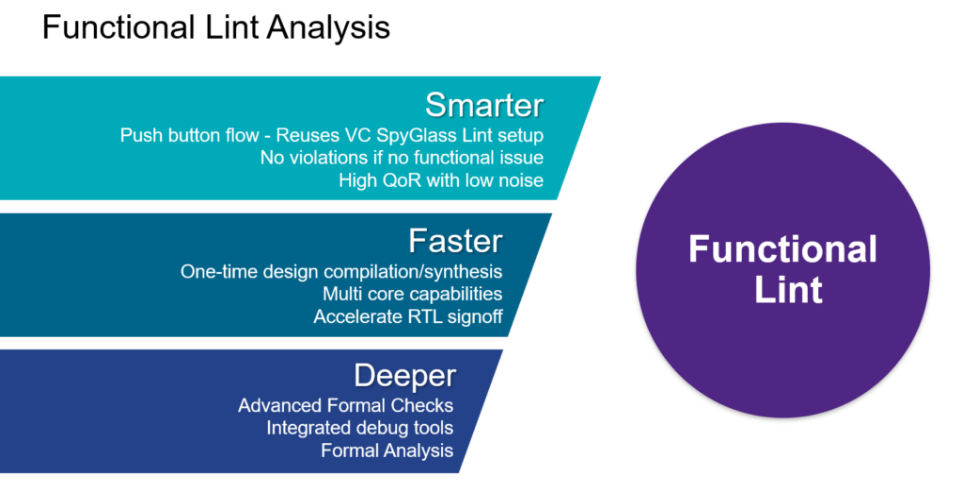

凭借深厚的专业知识和技能,新思科技在传统Linting方法学的基础上新增了功能Linting检查。借助新思科技的VC SpyGlass Lint,开发者能够以独特的简易流程,以更智能、更快速和更深入的方式开展功能Lint分析。用户无需提供复杂的约束条件,也无需具备形式验证方面的专业知识,便可利用新思科技的无缝混合流程加速RTL签核。VC SpyGlass利用VC Formal™原生技术,为解决位宽不匹配和越界检查等RTL设计问题提供了一套综合、易用、低误报的方法学,从而实现违例报告更准确的高质量RTL。

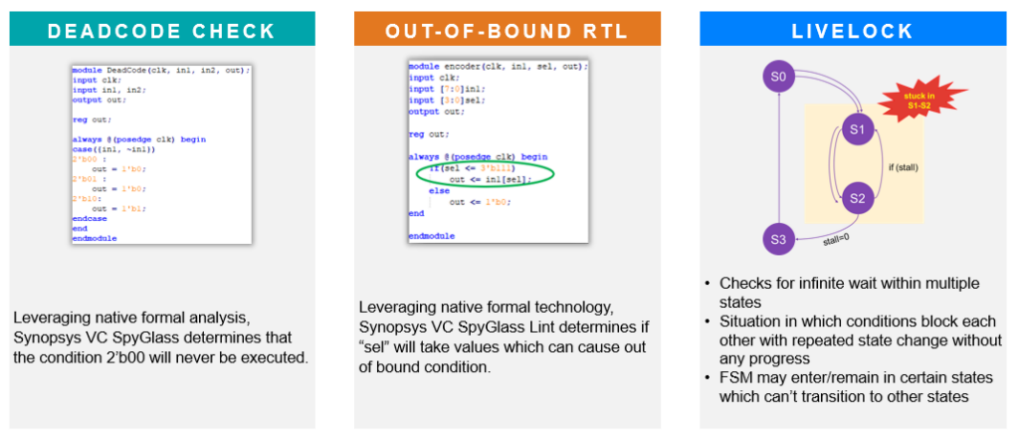

以DeadCode和FSM LiveLock为例,前者是用于识别不会被触发的RTL代码的关键检查,后者则是针对多个状态下无限等待的检查。它们都无法被传统的Linting检查技术识别,因此需要使用新思科技的VC SpyGlass功能Lint技术。此外,简单的调试功能,如波形查看器和带有详细注释的原理图查看器,也能进一步缩短验证时间。代码复杂性看板报告也能帮助管理团队预估RTL的复杂性。这些独特的功能能够将潜在错误尽早暴露给开发者,从而避免它们在下游阶段演变成更严重的问题。

新一代Linting技术

实现更智能、更快速、更深入的RTL签核

Linting检查让开发者的工作更加轻松、编写的代码更加稳健,同时也更适合后续的验证和实现流程。新思科技始终是Linting检查技术领域的领导者和践行者,始终致力于帮助客户更早发现漏洞和其他设计错误。新思科技的VC SpyGlass包含CDC、RDC和Lint技术,作为新一代的RTL签核平台,已获得各大公司的广泛使用。意法半导体等公司通过使用VC SpyGlass将CDC/RDC的验证速度最多提高了4倍。

无论是新思科技的GuideWare方法学,还是VC SpyGlass Lint中利用VC Formal原生技术的功能Lint流程,均已成为业界领先的ASIC/SoC公司的基本设计方法学,且已被各大半导体公司所采用。即便是初创的小型芯片设计公司也将VC SpyGlass作为他们的第一选择并纳入其RTL流程。

新思科技与全球排名前20的半导体客户均有合作,因此我们能够及时掌握最新行业标准,开发出完备的RTL签核Linting工具。无论是设计覆盖的深度,还是适配各种RTL场景和编码风格的广度,我们的工具都表现地十分出众。

未来,我们将剖析在功能检查中集成机器学习(ML)技术和RCA功能将如何更好地帮助开发者大幅缩短周转时间,并介绍智能Linting检查在未来几年的发展趋势。