2023年7月31日,芯片软硬件协同设计解决方案服务提供商兆松科技(Terapines Technology),宣布兆松科技的 ZCC 工具链全面支持Andes晶心科技(Andes Technology; TWSE: 6533)全系列的 RISC-V 处理器。ZCC工具链目前在嵌入式、高性能、AI芯片等多个领域的表现都处于国际领先水平。

Andes晶心科技是32及64位高效能、低功耗RISC-V处理器核心领导供货商、RISC-V国际协会(RISC-V International)的创始首席会员,也是将RISC-V推向主流的主导力量。近日,兆松科技也正式加入RISC-V International,成为其战略会员。ZCC全面支持AndeStar™ V5指令集,意味着晶心科技及其合作伙伴可以在 V5架构的 RISC-V CPU产品中使用 ZCC 工具链,以达到更高代码密度和性能,从而满足更加广泛的应用需求。

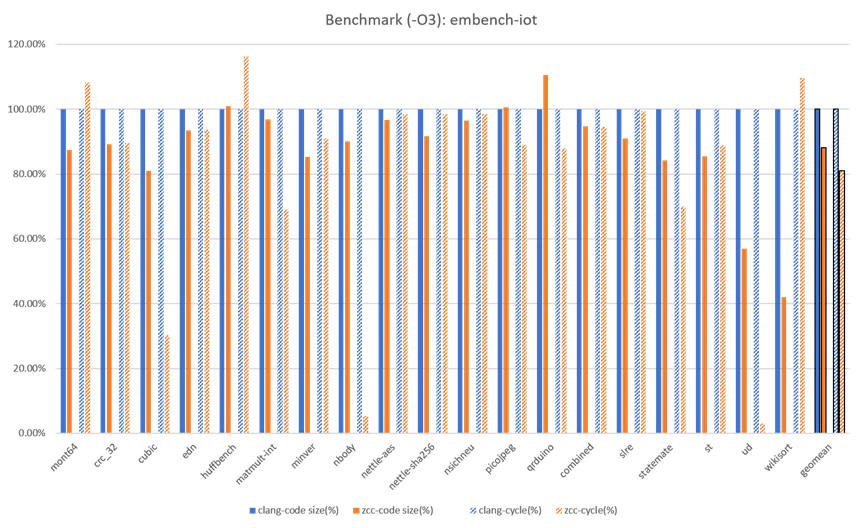

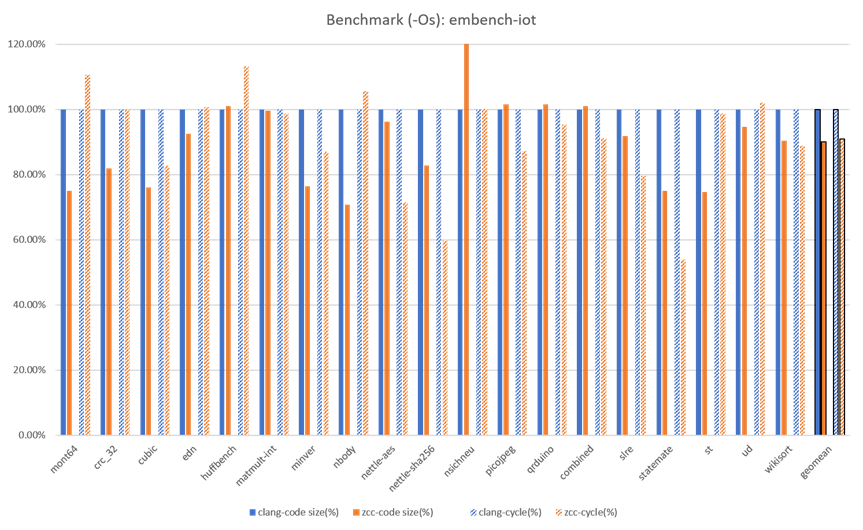

ZCC工具链相较Andes晶心科技AndeSight™ IDE 所提供的LLVM编译器,可以进一步将AndesCore™ AX45 双发射8级流水线处理器CoreMark分数提升6%,在Embench-IoT(-O3)测试中同时实现了18.9%的性能提升和11.8%的代码密度优化;在Embench-IoT(-Os)测试同时实现了10%的代码密度优化和9.1%的性能提升。

根据SPECInt2006动态指令数测试结果,相较开源LLVM 16.0,ZCC针对RISC-V RV64GCBV处理器的优化减少指令数30%,针对RISC-V RV64GCB处理器的优化减少指令数13%;

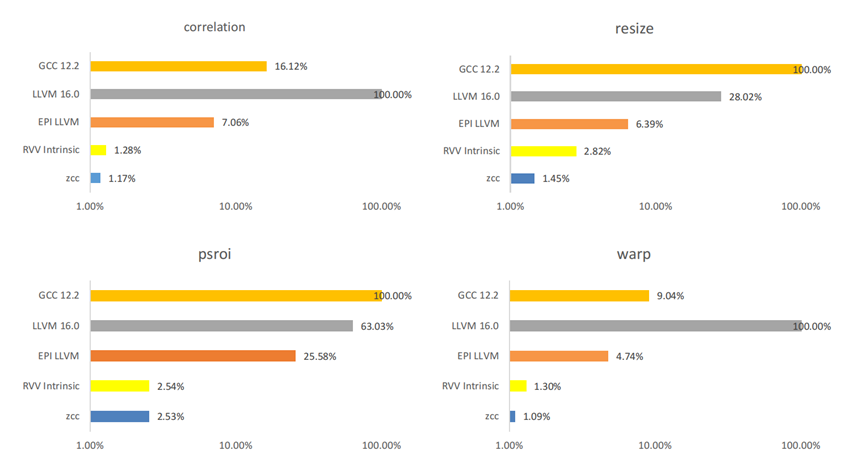

根据典型AI算子动态指令数结果,兆松科技ZCC工具链自动向量化性能相较于开源编译器最高提升91倍,意味着ZCC工具链可以为AI芯片的开发带来前所未有的优势,在性能和手写算子库不相上下甚至超过手写算子库的情况下,可以大幅降低算子库的维护成本。

兆松科技CTO伍华林表示,“兆松科技从ZCC工具链全面支持AndeStar™ V5的指令集作为起点,将逐步和晶心科技建立更进一步的合作,除了从工具链的代码密度和性能等优势上,帮助AndesCore™ RISC-V CPU IP更具有竞争力,未来还将提供软硬件协同设计工具,虚拟模型性能仿真工具等,帮助晶心科技的客户,高效的设计出有竞争力的芯片。”

“很高兴看到兆松科技与Andes晶心科技合作协助我们的共同客户,大幅优化发挥出RISC-V处理器的效能, 同时进一步缩减代码。”Andes晶心科技总经理暨技术长苏泓萌博士表示,”RISC-V技术持续快速发展,我们期许持续拓展生态系为客户提供专业开发工具的支持,进一步保障客户的产品效能与竞争力。”