3.测量

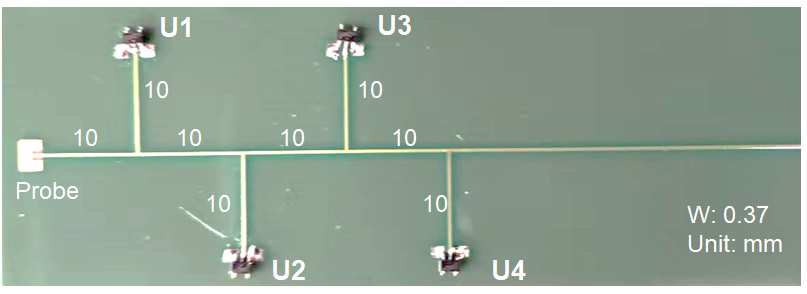

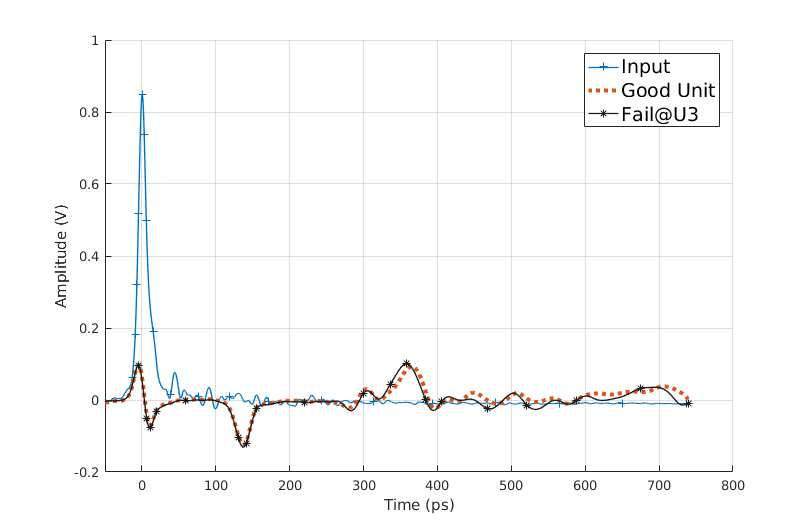

OSN方法在BUS网络上进行了实验验证。在厚度为0.2 mm的FR4衬底上制备了带有微带线的PCB样品。对于宽度超过0.37 mm的所有引线,实现了50Ω特征阻抗。图8显示了4个芯片(U1~4)的BUS拓扑网络的PCB布局。每个芯片由一个逆变器芯片(Nexperia, 74AUP1GU04)实现,其中引脚2(输入)和引脚3(地)分别焊接到每个分支引线和PCB地的末端。根据74AUP1GU04数据表,输入电容(CIN)为1.5 pF。由于所有芯片在TDR测量期间都处于断电状态,因此芯片的其余引脚未连接。故障单元设计为Fail@U3,其特点是在与U3并联的10-Ω电阻器中短路。采用8个参考芯片进行OSN分析,包括4个芯片点的开路和短路情况。采用Advantest TS9001 TDR系统进行测量。图9为输入端模拟TDR波形。与仿真中使用的理想输入信号不同,输入端的实际脉冲信号是一个不对称的脉冲形状和一个带噪声的尾部。TS9001分析软件提供了反卷积功能来解决这个问题。为了更好地显示波形,所有后续的测量波形都是在反卷积后呈现的。

图8 4个芯片的BUS拓扑网络的PCB布局

图9显示了反卷积后好片 (Fail@U3)反卷积后的波形,波形紧密对齐直到大约330 ps。与仿真结果相比,测量结果具有更高的样本到样本的变化,这是优于PCB布局和逆变器CIN的公差。此外,在好片和Fail@U3的测量结果中,在0ps附近都观察到由探测接触产生的微扰。

图9 4个芯片的BUS拓扑网络的TDR波形

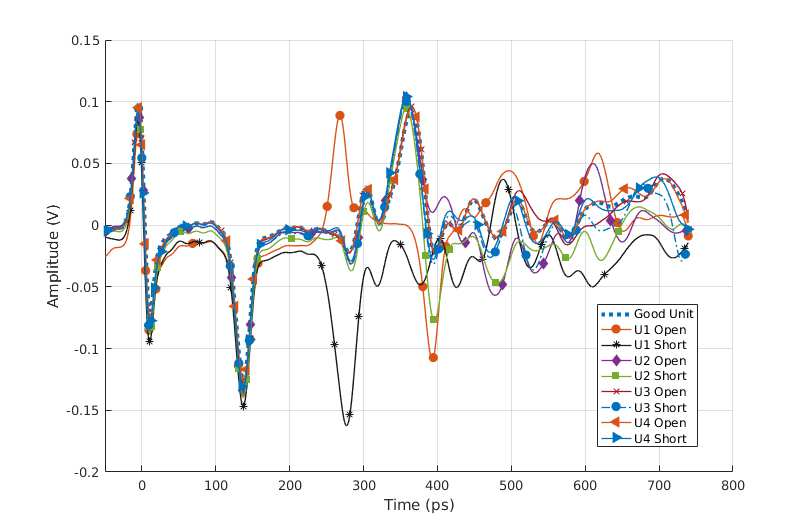

步骤1:开路/短路参考

图10显示了8个开/短路参考芯片在所有芯片点(U1~4)相对于好片的测量TDR波形。与仿真结果不同的是,即使在传播的公共路径中,波形之间也没有完全对齐,可以观察到直流电压电平的移位。由于TDR波形在反卷积过程中的时间跨度有限,这是不可避免的。但是这不会影响OSN分析。

图10 参考芯片的实测TDR波形在U1、U2、U3和U4处开断和短路

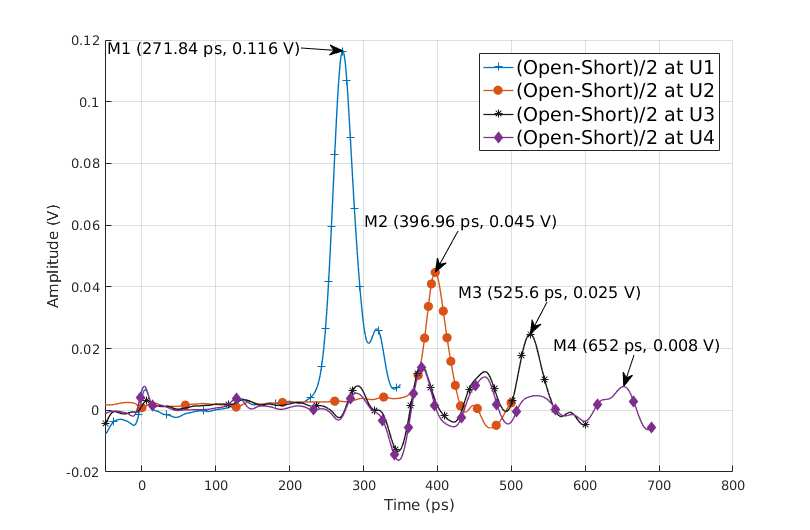

步骤2:TLI、DIR和DDR

计算得到的四个芯片点的TLI。如图11所示。U1、U2、U3、U4的TLI分别为M1、M2、M3、M4。Fail@U3的TDR波形在330ps之前与好片相差不大,因此其可能的缺陷位置可能在U2、U3或U4,因为M1位于缺陷时间窗之外。接下来是计算每个可能缺陷点U2, U3和U4的DDR。

图11 U1、U2、U3、U4的时间-位置指标

步骤3:缺陷位置和缺陷类型

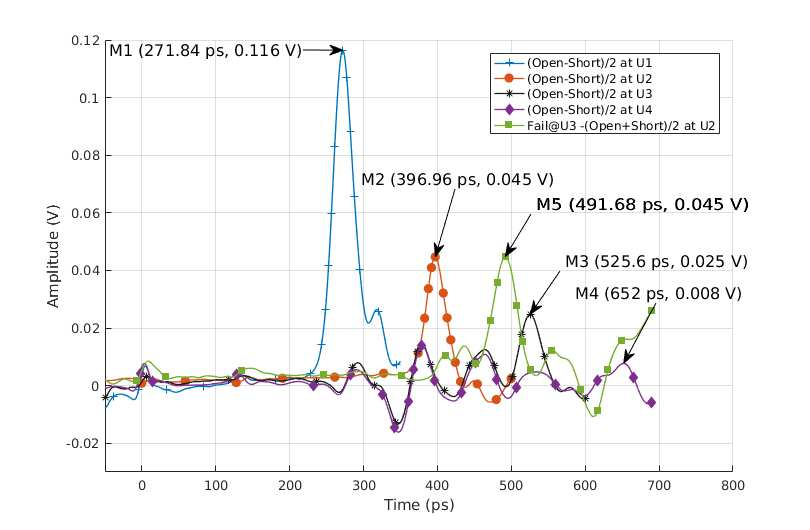

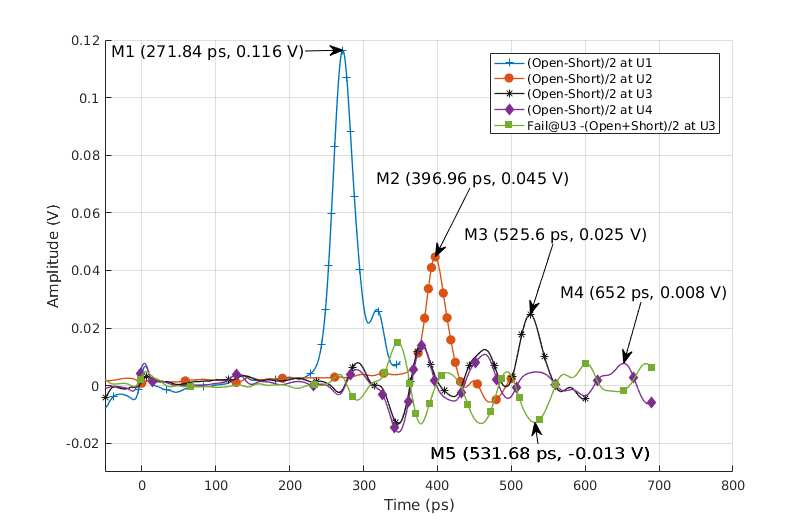

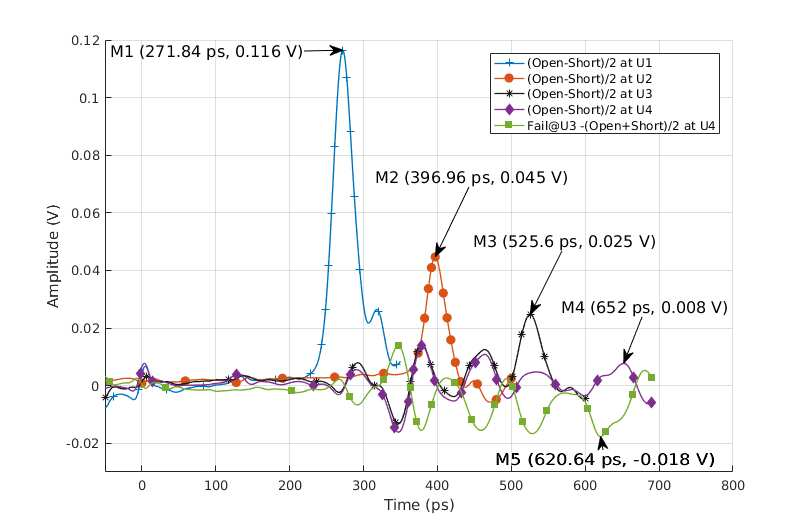

图12为假设U2为缺陷位置时提取的Fail@U3 DDR,其中第一个峰出现在M5 (491.68 ps, 0.045V)处。显然U2不是故障点,因为M5在时间上离M2有95-ps的距离。图13为假设U3为缺陷位置时提取的Fail@U3 DDR,其中第一个峰出现在M6处(531.68 ps, -0.013V)。M6与M2在时间上很好地对准,表明U3为缺陷位置,而且根据计算出的反射系数-0.52,可以进一步估计缺陷类型为电阻性短路,等效短电阻为15.8 Ω。当然,15.8Ω与预设的10Ω电阻器不一样,但它与实际值足够接近,可以证明缺陷的原因。图14为假设U4为缺陷位置时提取的Fail@U3的 DDR,其中M7处(620.64 ps, -0.018V)与M4在时间上最接近。U4绝不是缺陷位置,因为M7与M4在时间上的距离为29.4-ps,但其量级远高于M4。通过OSN分析,我们成功地找到了Fail@U3的缺陷位置和缺陷类型。

图12 假设U2为故障点,提取Fail@U3的DDR

图13 假设U3为故障点,提取Fail@U3的DDR

图14 假设U4为故障点,提取Fail@U3的DDR

4.结论

利用开短归一化(OSN)方法,可以从多支路坏片的TDR波形中提取缺陷相关反射(DDR),快速估计缺陷位置和缺陷类型。本文展示了OSN在4个芯片的BUS网络中识别缺陷位置和缺陷类型的应用。通过仿真和测量结果验证,OSN有效地分析了分支引线网络的开路缺陷和短路缺陷。