相比于激进的英特尔,不仅已完成业界首台商用高数值孔径(High-NA)EUV的组装工作,更有消息放出英特尔已“承包”ASML今年全部高NA EUV光刻机产能,台积电却依旧“淡定”,表示继2nm之后推出的A16(1.6nm)制程也不会采用该光刻机。

作为代工业的常胜将军,台积电作出的这一决定应是深思熟虑之举。

而背后释放的另一重深意更值得深思:1.6nm不用高数值孔径EUV也可实现,不仅实现了对高NA光刻机的祛魅,也为持续在追赶中的大陆代工业带来新的启示。

有专家指出,对于光刻技术可能要重新认识,之前认为2nm必须采用高NA光刻机,而台积电开创先河直接拒用。反观之前业界认为美国阻止EUV出口大陆,大陆在先进制程领域只能止步于7nm,如此来看或许提升至5nm也不是没有可能。

平衡成本和技术

在前不久台积电举办的2024年北美技术论坛,台积电首次公布了A16制程工艺,并透露A16制程工艺不需要采用下一代高NA EUV光刻机,预计2026年量产。

如此笃定,充分表明台积电已找到了在现有EUV光刻机经济高效地使用双重曝光等方法实现1.6nm的途径。

上述专家对集微网表示,工艺制程离不开设备,可以说有先进设备才能实现更先进的制程,但台积电此次暂缓引入高NA光刻机,可能是尽管采用了多重曝光,相对工艺步骤多、周期长、成本高,但采用高NA光刻机可能风险更大,台积电应是认为采用原有的EUV更为经济且可行。

而台积电豪言让现有EUV发挥“余热”,还在于其多年来在EUV领域积累了丰富的经验,通过持续创新不断提高生产率、降低成本和功耗。台积电于2019年开始在其N7+工艺上使用EUV,通过优化EUV曝光剂量及其使用的光刻胶,改进光罩薄片延长寿命、提升产量、降低缺陷率等等,如今光刻机数量增加了十倍,但晶圆产出是2019年的30倍,且仍将持续改进,这也成为其未来支撑1.6nm工艺的重要支柱。

除保证可行性、让现有EUV发挥余热之外,台积电暂缓高NA EUV引入亦是应对成本、挑战和客户需求的权衡之举。

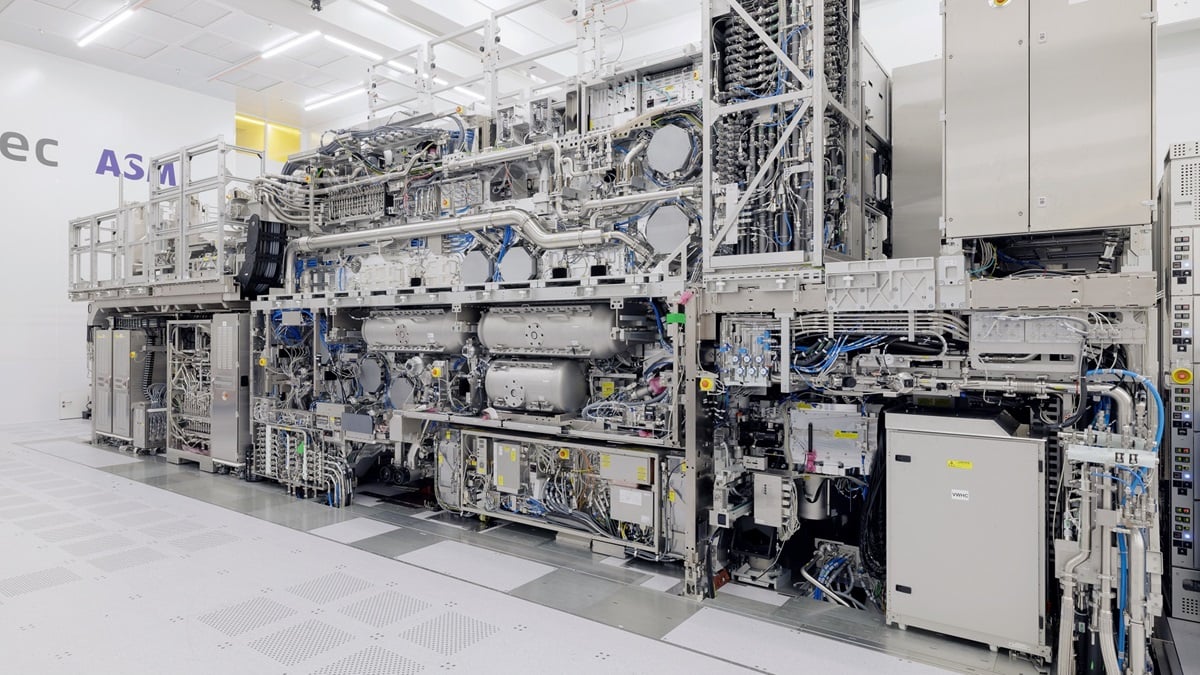

尽管高NA EUV工具在提高制程效率和性能方面具有巨大潜力,但其价格十分昂贵,据悉一台高NA EUV成本高达3.5亿欧元,比现有EUV的1.7亿欧元约高出2倍多。连台积电资深副总经理张晓强也直言高NA EUV虽然性能令人满意,但“价格实在太高了”。而且,引入高NA光刻机并不表明万事大吉,不仅要解决相应的挑战,如可以支持光子散粒噪声和生产力要求的光源;满足0.55NA小焦点深度的解决方案;计算光刻能力;掩膜制造和计算基础设施包括新型材料等等,还需要一定的调试和开发时间,兼顾稳定性,投入的时间和隐形的成本可以想见。

此外,市场需求也需考量。有行业人士李弈(化名)指出,采用高NA光刻机制造的芯片成本巨增,虽然每片晶圆切割的芯片更多,但需要销售更多的芯片才能弥补投入,目前仍无法判断最先进工艺市场需求能否有足够的量来消化成本。

“单靠手机AP芯片市场难以支撑,AI芯片的需求能否支撑仍待观察。本来AI最大的市场在中国,现在被限制后找不到第二个市场能够支撑,市场预期并不好。”李弈说。

因而,台积电持续采用现有EUV实现1.6nm,不仅可大幅降低总体成本,在成本和技术之间寻求了平衡,还进一步彰显了台积电对于成本控制和技术更新速度的深刻理解。

背面供电将全面硬杠

值得关注的是,台积电A16工艺将结合GAAFET与背面供电,以提升逻辑密度和能效。与N2P相比,A16工艺芯片预计在相同电压和复杂度下性能提升8%-10%,在相同频率和晶体管数量下功耗降低15%-20%,且密度将提升1.1倍。

在之前的2nm节点,台积电已全面导入GAAFET晶体管技术,因而其1.6nm工艺更突出的特征还在于背面供电。

作为继工艺缩进、3D封装后第三个提高芯片晶体管密度和能效的革新之一,背面供电不仅是半导体工艺创新的重要发展方向之一,也成为先进工艺比拼的新“竞技场”。

在这一技术领域,英特尔仍是先行者,计划在2024年上半年首次应用于其节点Intel 20A(相当于2nm),并计划在未来量产中应用于Arrow Lake平台。而三星也想先下一程,将背面供电技术应用提前,原定于2027年对背面供电技术商业化,搭载于1.7nm制程,但近期爆料显示三星将修改路线图,最早将于2025年2nm制程应用背面供电技术。

这也意味着,三大巨头的对决不止在2nm GAA层面,在背面供电领域也将火力全开,谁能更胜一筹或成为未来对决的胜负手之一。

有分析称,台积电的背面供电尽管比英特尔推出晚了一两年,但其新型超级电源轨BSPDN技术将背面电源网络直接连接到每个晶体管的源极和漏极,比英特尔PowerVia与晶体管开发分开的方案更为复杂,在面积缩放层面更为有效。

1nm或将引入高NA光刻机

细究台积电的成功之路,台积电从来就不争“第一个吃螃蟹者”,无论是从DUV转向EUV,还是选择GAA,台积电均倾向于确保新技术的成熟和可靠性之后再进行部署,其“稳健”的台风一直在沿续。

以EUV为例,当三星在2018年开始在其7nm工艺中使用EUV之际,业界也普遍认为EUV必不可少之际,台积电依靠成熟的DUV光刻机仍成功地开辟了首条7nm产线,巧妙地避开了当时EUV光刻机的不完善和高昂成本,同时也印证了它在技术进阶路线选择上的准确判断。直到EUV的稳定性和成熟性得到确认,才在2019年的N7+工艺中开始使用EUV。相较之下,三星率先采用EUV的勇气可嘉,但由于良率问题反而让台积电后来居上。

此外,在与三星3nm制程竞赛中,台积电并没有急于使用GAAFET,而是依旧选择稳妥的FinFET路线。尽管三星在3nm先声夺人,但良率过低和反复跳票让台积电在3nm后发先至,捷报频传,客户的“集体投票”即是明证。

从不冒进的台积电坚定地遵循着一步一个节点的演进策略,稳扎稳打不断突破,如同接力赛中的优秀接力手,将前一棒的优秀成果传递至下一棒,在先进工艺的长跑赛中以定力和耐力持续成功登顶。接下来的问题是尽管台积电在1.6nm工艺划了高NA光刻机的“红线”,但未来在哪一节点引入也成为业界关注的话题。

台积电之前公布的路线图显示,基1.4nm级A14工艺预计在2027年至2028年之间推出,而1nm级A10工艺的开发预计将在2030年前完成。有消息指出,台积电可能会等到1nm工艺上线后才会考虑使用下一代光刻机,按照目前的节点迭代速度,或在2029年至2030年间采用高NA EUV系统。

上述专家对此表示,在市场经济中只要企业自主决定,一定是适合自己的策略。对台积电来说,后续引入高NA光刻机或是认为达到其投入和产出、以及技术成熟度的平衡点。

大陆工艺进阶如何借鉴

探寻台积电最近的这一系列稳健决策,以及工艺稳健的演进历史,对于处于风口浪尖的大陆半导体产业来说,无疑具有重要的启示作用。

尤其是在当下大陆在EUV光刻机获取全面受阻的情况下,李弈建议,台积电通过深入挖掘现有EUV光刻机的潜力,可支撑未来的1.6nm工艺,而大陆代工业如何借助DUV光刻机向7nm乃至下一步5nm制程发起冲刺应当有希望,应着力在光刻胶、光罩、多重曝光技术等领域持续创新突破,以全面提升利用DUV实现更先进制程的可能性。

还要意识到的是,台积电的成功不仅取决于工艺的持续迭代和良好的良率,客户的信任为其持续迭代提供了强大的助力。

有报道指出,在3nm时代,台积电报价超过2万美元,较4nm/5nm代工价格高出4000美元。这种高价让众多客户望而生畏,然而苹果仍然选择台积电代工,并包圆了起步时的所有产能。进入2nm,台积电依旧有苹果“撑腰”。

近日苹果首席运营官Jeff Williams访问台积电,双方举办了一场“秘密会议”,苹果将为其自研AI芯片“包圆”台积电所有初期2nm工艺产能。据行业预测,如果苹果预定台积电2nm乃至更先进制程的首批产能,则预估苹果将贡献台积电营收达新台币6000亿元约合1345.8亿元,有望再创新高。

台积电和苹果的深层次捆绑背后,是双方互利共赢的双向奔赴。对于大陆代工业来说,扩大自己的朋友圈、扩展有实力的合作伙伴也是未来向前发展的必修课。

路在脚下事在人为,台积电暂缓引入高NA的战略选择不止是自己的实力、底气和稳健使然,更是对大陆半导体工艺自主创新发展的一次深远鼓舞,大陆探索出一条通往先进制程的独特道路必有可为,大有可为。