引言

原型验证是一种在FPGA平台上验证芯片设计的过程,通过在FPGA上实现芯片的设计原型,使得开发人员可以在硬件完成之前提前开始软件开发和系统验证。然而,如何快速确保在原型验证平台上开发的软件能够顺利移植到最终芯片上,并完成“bring-up”(即系统启动并正常运行),成为了开发团队面临的一个重要挑战。

为了实现这一目标,虽然原型验证具备高性能,能够快速模拟真实芯片的运行环境,但要进一步满足客户对快速开发和验证的需求,缩短开发周期,还必须依赖于灵活的子卡(Daughter Boards)、降速桥(Speed Bridge)方案、AXI协同仿真软件以及优化的I/O分割(Partition)设计。这些工具不仅为软件开发提供了真实的数据交互环境,还显著加快了软硬件的bring-up过程。因此,在选择商用原型验证平台时,资源的多样性与灵活性成为提升验证效率的关键因素。

如何快速进行原型设计?

在原型验证过程中,“bring-up”是一个关键阶段,涉及一系列操作,从硬件配置、基本功能验证到复杂系统的运行调试。这个过程不仅仅是硬件的连接和配置,还涉及到软件的运行、设计加载、错误调试等多个步骤。最终的目标是确保系统能够在预期的条件下顺利运行,从而为进一步的功能测试和性能评估做好准备。

快速完成“bring-up”依赖于多个关键因素:

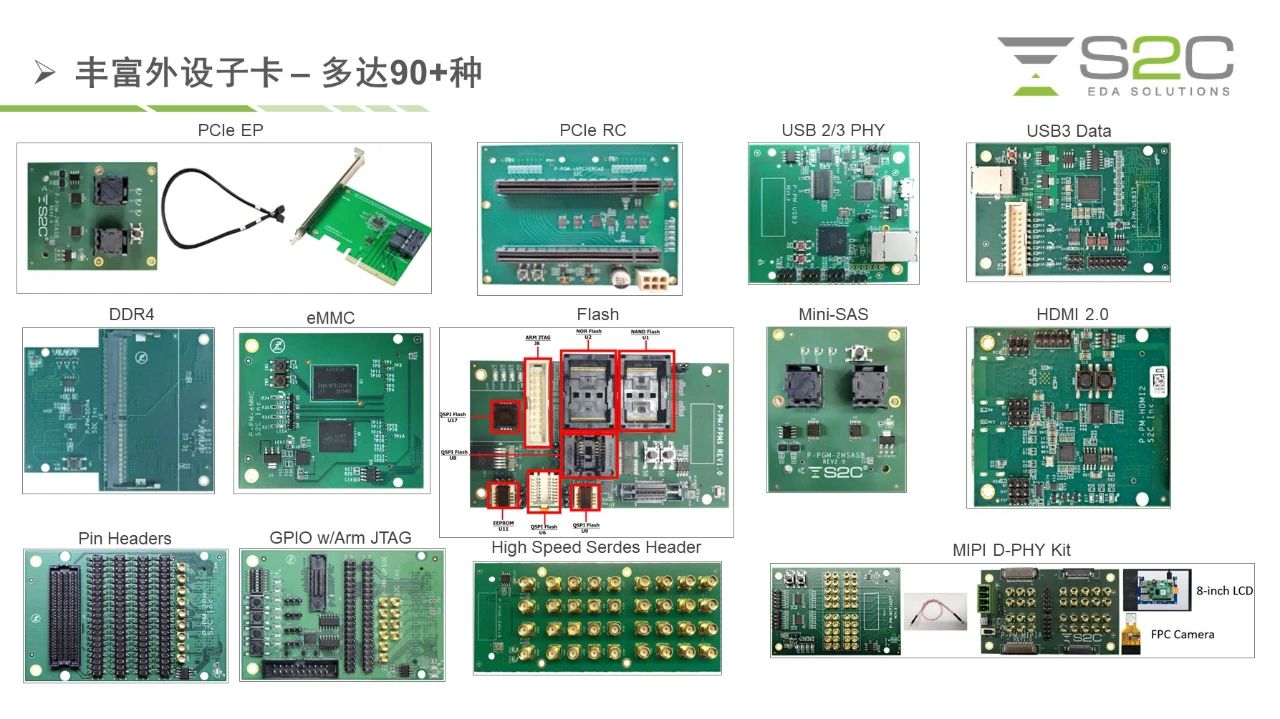

首先,灵活的接口方案对于快速部署至关重要,能够支持与外部真实设备的连接。子卡是原型系统与外部设备交互的核心组件,它们支持多种通信协议,如MIPI、DDR4、PCIe等,满足多种应用场景需求。通过灵活的子卡配置,开发团队能够根据项目需求,快速搭建符合真实使用环境的接口,加快系统验证的进程。

降速桥以及相应的IP开发套件也是实现快速“bring-up”的关键。它能够有效地协调高速与低速设备的通信,确保原型系统与外部设备之间的数据传输稳定流畅。降速桥的接口方案通过高效的数据转接机制,保证了系统与实际应用环境之间的适配,并最大程度地提高了原型验证系统的可靠性。

除了硬件支持外,AXI协同仿真软件和参考设计也在快速部署中发挥了重要作用。AXI协同仿真软件凭借其高效的数据传输和处理能力,帮助开发人员在接近真实芯片运行速度的环境中进行仿真和验证。而参考设计提供了经过验证的成熟解决方案,帮助开发团队快速集成和验证设计,从而减少从头开发的时间和成本。这些工具和技术的结合,显著提高了开发团队的生产力,帮助他们在最短时间内达到验证目标,并加速生成所需的波形数据(Fast Time to Waveform)。

此外,分割是大规模SoC设计中设计加载的核心挑战之一。为了支持大规模设计,系统需要提供丰富的I/O接口以及高速SerDes接口,以实现分割后的互连和外设连接。

芯神瞳Prodigy原型验证

子卡:

子卡在原型系统与真实芯片环境之间提供了灵活的接口,能够根据不同应用需求进行配置。子卡支持多种通信协议,满足多媒体接口(如 MIPI)、SoC软硬件协同(如 DDR4)、存储(如 PCIe)和网络接口等需求。这种灵活性确保了原型系统可以模拟真实使用环境的接口和带宽要求,使得设计团队能够快速适配不同应用场景,加速原型系统的部署。

当前FPGA厂商提供的测试套件和内部FPGA板在应用上存在一定局限性。大多数评估板上的固定接口往往无法满足SoC/ASIC原型验证的需求,且难以在新项目中重复使用。这一限制同样适用于许多自制的FPGA板。一些公司选择自行开发(BYO)子卡接口,但这不仅增加了验证接口正确性的难度,还可能在没有现成子卡或设计的情况下,使快速部署变得十分困难,常常需要从头设计或修改。这种开发成本和复用困难在激烈的市场竞争中往往会成为一大负担。

思尔芯的芯神瞳 Prodigy 原型验证解决方案为用户提供了多种灵活的接口方案,包括丰富的外部子卡集合,涵盖了多种模块类别,包括 Arm 处理器接口模块、嵌入式模块、多媒体模块等。这些模块覆盖了主流应用领域,经过市场验证,用户可以直接使用,避免了自行开发的复杂性和潜在风险。

这些预先测试过的广泛子卡集合帮助用户减少开发风险,能够满足当前芯片接口的行业标准,例如 USB、HDMI、PCIe、以太网和 DDR。以 Prodigy 三通道 RGMII/GMII PHY 接口模块为例,通过严格的设计流程,确保子卡能够在超过125MHz的频率下稳定运行,支持千兆以太网的性能。自动检测技术使全球团队能够远程识别并测试子卡,同时集成的 IO 电压检测功能可以防止由于输入错误电压而导致的硬件损坏。

降速桥:

降速桥方案与相关IP模块能够有效协调数据传输,确保原型系统能够与低速外部设备进行接口适配。通过灵活设计,降速桥IP支持高速传输协议的转换,保证系统性能与实际应用环境一致。

在大规模复杂SoC设计中,高速接口IP(如PCIe Gen3/Gen4)在FPGA原型验证阶段往往由于工艺限制只能运行在较低速度,无法直接连接实际外部接口。因此,需要相应的高速接口降速桥方案进行适配。降速桥IP通常有两种形式:基于硬件的降速桥和基于软核IP的降速桥。思尔芯都有相应的解决方案。

此外,先进的Memory控制器IP(如LPDDR4/5,HBM2E/3)的验证在FPGA原型系统中也是一大挑战。由于这些控制器IP标准较新,主流FPGA供应商无法提供相应的PHY解决方案,导致这些IP在FPGA原型验证系统中无法正常运行,思尔芯便为此提供了相应的解决方案。

例如,有客户在设计中使用了LPDDR4 Memory控制器,但由于在原型验证阶段缺少基于FPGA的LPDDR4物理层IP,无法进行验证。通过采用思尔芯提供的基于DFI接口的Memory控制器IP适配方案,客户将LPDDR4控制器的读写操作通过DFI接口成功转接到FPGA厂商的DDR4 Memory控制器上,顺利完成了LPDDR4控制器的验证。

调试时的AXI协同仿真:

基于 FPGA 的原型系统在运行速度和精度上接近流片后的实际芯片,对于芯片的完整功能性确认和早期软件开发来说至关重要。然而,构建一个符合标准的原型验证系统,需要丰富的专业知识、大量资源以及额外的硬件环境和互联技术方案支持。

思尔芯的芯神瞳协同仿真软件 ProtoBridge 通过采用广泛使用的 AXI-4 总线协议以及独有的专利技术,实现了设计到 FPGA 原型验证环境的连接。通过高吞吐量的数据通道,ProtoBridge 实现了 FPGA 与 PC 主机之间的快速数据交互。使用这些工具,开发团队可以在接近真实芯片速度的环境中进行早期的软件调试和功能验证,减少了芯片回片后的适配工作,显著提升了设计移植的效率。

分割时的I/O优化:

在原型验证中,系统需要提供丰富的I/O接口和高速SerDes接口,以支持分割(partition)互连及外设子卡的连接,确保高效的数据传输与系统协同工作。然而,分割过程往往是一个复杂且反复的迭代过程,涉及设计映射到设备的多次判断和调整,必须从RTL或软件中的错误中筛选并纠正映射错误。

思尔芯的芯神瞳 Player Pro – CompileTime(PPro-CT)工具为此提供了一种高效解决方案。它通过图形化界面逐步引导用户完成所有编译步骤,并支持Tcl脚本模式下的自动ECO流程执行。尤其在I/O管脚分配方面,Player Pro 通过集成思尔芯子板I/O管脚对应关系的库文件,自动匹配到I/O连接器,显著提升了效率并减少了人为错误的可能性。

传统I/O布局的局限性极大地限制了验证系统的规模。为突破这一瓶颈,新一代的PPro-CT 具有SerDes的TDM模式,使级联规模至少提升1倍,打破了I/O数量的限制,从而使更大规模的原型系统验证成为可能。通过这一优化,开发团队能够更加灵活地处理复杂设计,并加速原型验证进程。

总的来说,快速原型设计依赖于多个关键因素的协调与整合。子卡与外部接口的搭配与数据交互是系统验证的基础,降速桥IP则通过高效的转接性能实现不同设备间的协同工作。调试方面,思尔芯的 ProtoBridge 软件通过软硬件协同,确保了设计能够在接近真实芯片的环境中进行调试与验证。而在系统分割过程中,通过丰富的I/O接口和高速SerDes接口,保证了分割设计的有效互连与高效数据传输。这些要素的紧密配合,极大提升了系统的稳定性与部署效率,使得快速原型验证成为可能。

而思尔芯为用户提供了多种灵活的接口方案,包括丰富的外部子卡集合、降速桥方案、调试时需要的AXI协同仿真软件,以及分割时I/O优化等,提供了超过90种不同子卡和配件,使得他们能够更快速地搭建原型验证环境并应对不同的项目需求。这些预先测试过的,并久经市场验证的方案不仅帮助用户减少开发风险,还能显著减少开发工程资源,加速芯片设计的验证与优化过程,从而在竞争激烈的市场中保持领先地位。