环栅晶体管(GAAFET)与传统FinFET工艺流程相比,引入了内侧墙(inner spacer)、沟道释放(channel release)等工艺,必须通过对叠层结构的精确横向刻蚀来实现。高精度刻蚀工艺控制是三维集成电路制造面临的最大挑战之一,其工艺机理和调控机制在科学界和工业界受到广泛关注。

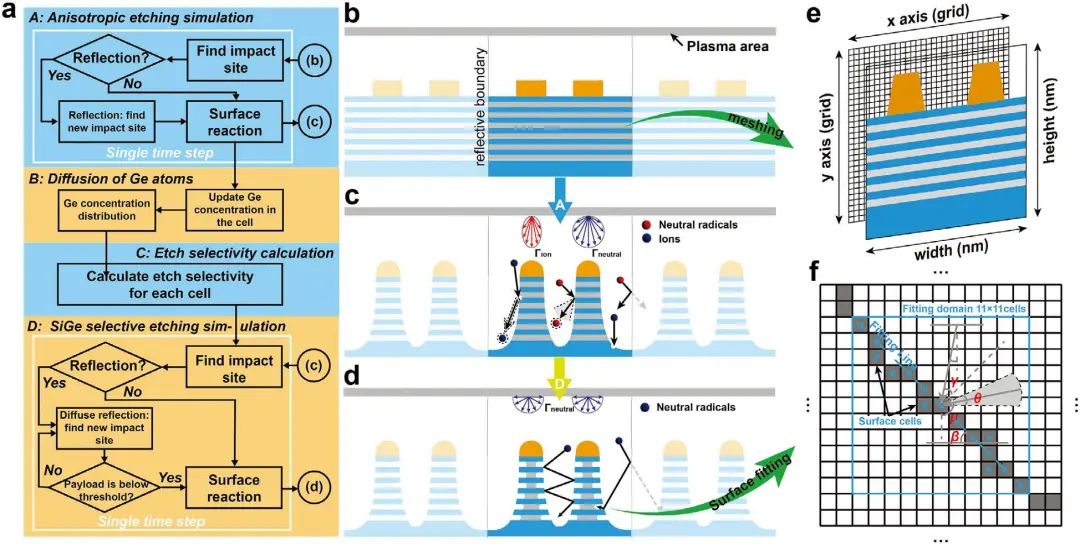

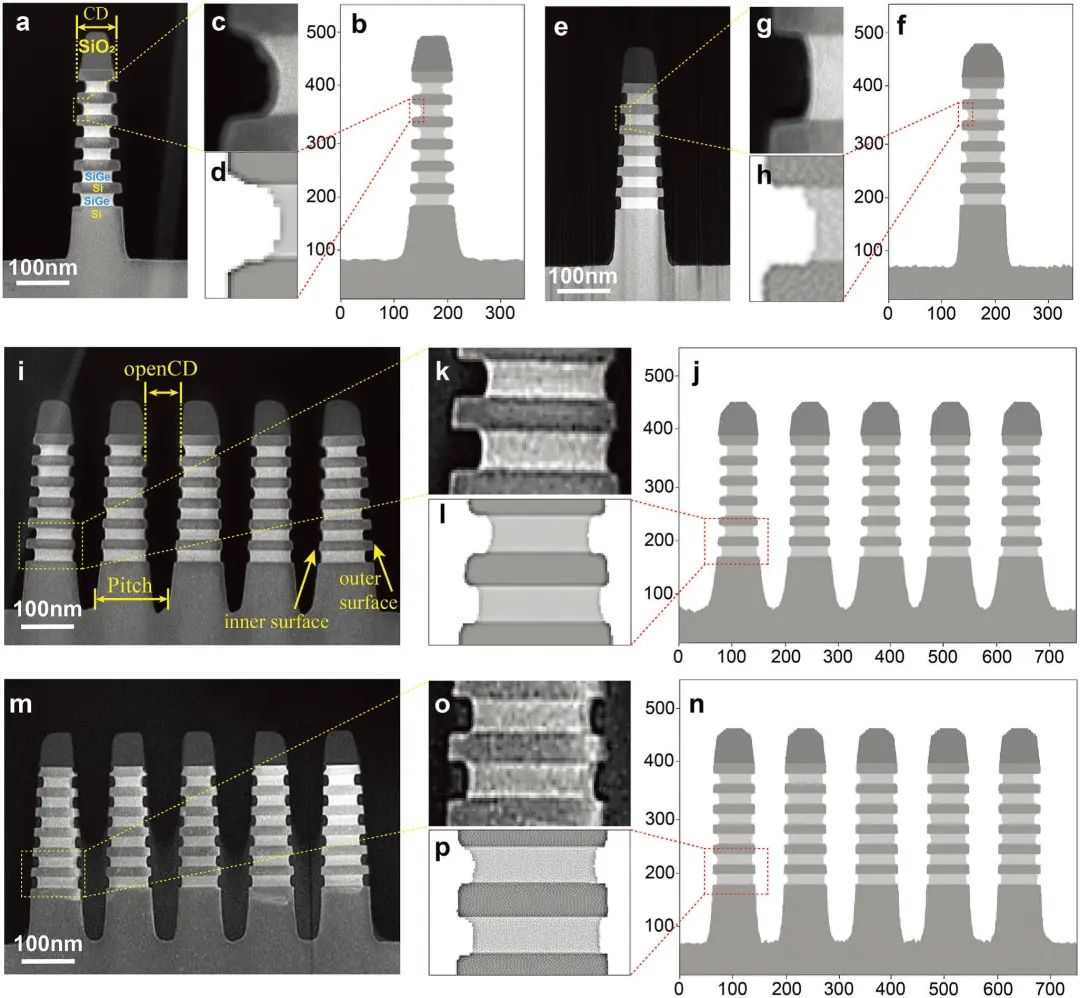

针对GAA内侧墙结构Si/SiGe叠层横向选择性刻蚀工艺面临的形貌缺陷和均匀性问题,微电子研究所EDA中心陈睿研究员与先导中心李俊杰高级工程师、南方科技大学王中锐教授、维也纳工业大学Lado Filipovic教授合作,通过提出全新的Ge原子解吸附和扩散的模拟算法,建立了基于蒙特卡洛方法的连续两步干法刻蚀工艺轮廓仿真模型,实现了针对Si/SiGe六叠层结构的横向选择性刻蚀工艺轮廓仿真,并完成了相应结构的流片实验。通过结合形貌仿真和透射电子显微镜(TEM)表征,探究了Ge层刻蚀表面圆化现象,以及腔体气压等参数对刻蚀形貌均匀性的影响机制。该项工作为阐明新原理刻蚀工艺机理和优化工艺性能提供了理论和实验参考。

研究成果近期以题为“A Two-Step Dry Etching Model for Non-Uniform Etching Profile in Gate-All-Around Field-Effect Transistor Manufacturing” 发表在材料领域顶级期刊《Small》上,微电子所硕士研究生呼子义为论文的第一作者,微电子所陈睿研究员、韦亚一研究员、南方科技大学王中锐教授为共同通讯作者, 同时入选TCAD仿真领域旗舰会议SISPAD 2024口头报告。此外,相关研究成果还发表在《ACS Applied Electronic Materials》、《Journal of Vacuum Science & Technology A》等期刊上,微电子所李俊杰高级工程师为共同通讯作者。该项研究得到了中国科学院战略性A类先导专项、国家自然科学基金的支持。

图1 建模流程

图2 不同气压条件下的Si/SiGe六叠层iso/dense结构刻蚀实验与仿真结果