台积电11月欧洲开放创新平台(OIP)论坛上宣布,该公司有望在2027年认证其超大版本的CoWoS(晶圆上芯片)封装技术,该技术将提供高达9个掩模尺寸的中介层尺寸和12个HBM4内存堆栈。新的封装方法将解决性能要求最高的应用,并让AI(人工智能)和HPC(高性能计算)芯片设计人员能够构建手掌大小的处理器。

台积电每年都会推出新的工艺技术,尽最大努力满足客户对PPA(功率、性能和面积)改进的需求。但有些客户需要更高的性能,而EUV光刻工具掩模限制858平方毫米是不够的。这些客户选择使用台积电CoWoS技术封装的多芯片解决方案,近年来,该公司提供了该解决方案的多个迭代版本。

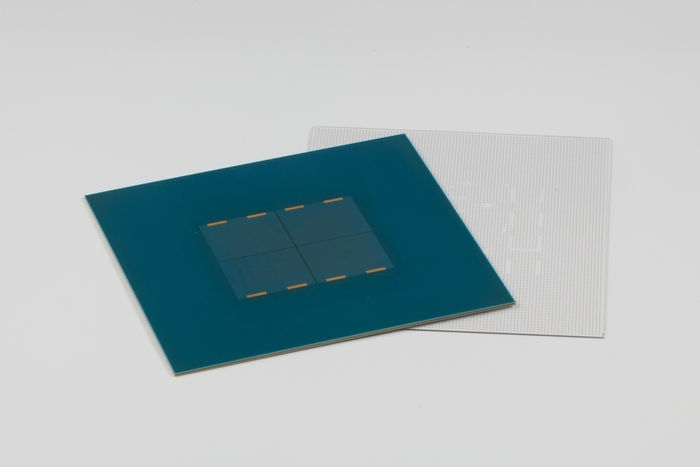

最初的CoWoS在2016年实现约1.5个掩模尺寸的芯片封装,然后发展到今天的3.3个掩模尺寸,这使得可以将8个HBM3堆栈放入一个封装中。接下来,台积电承诺在2025年至2026年推出5.5个掩模尺寸的封装,最多可容纳12个HBM4内存堆栈。然而,这比起该公司的终极版CoWoS仍相形见绌,后者支持多达9个掩模尺寸的系统级封装(SiP),板载12个甚至更多的HBM4堆栈。

该9个掩模尺寸的“超级载体”CoWoS(为芯片和内存提供高达7722平方毫米的面积)具有12个HBM4堆栈,计划于2027年获得认证,推测它将在2027年至2028年被超高端AI处理器采用。

完全希望采用台积电先进封装方法的公司也能使用其系统级集成芯片(SoIC)先进封装技术垂直堆叠其逻辑,以进一步提高晶体管数量和性能。事实上,借助9个掩模尺寸的CoWoS,台积电希望其客户将1.6nm级芯片放置在2nm级芯片之上,因此可以达到极高的晶体管密度。

然而,这些超大型CoWoS封装面临着重大挑战。5.5个掩模尺寸的CoWoS封装需要超过100x100毫米的基板(接近OAM 2.0标准尺寸限制,尺寸为102x165毫米),而9个掩模尺寸的CoWoS将采用超过120x120毫米的基板。如此大的基板尺寸将影响系统的设计方式以及数据中心的配备支持。特别是电源和冷却。每个机架的电源功率达到数百千瓦,需要采用液体冷却和浸没方法,以有效管理高功率处理器。(校对/赵月)