人工智能在图像识别、音频处理、自然语言处理、大模型等领域应用极为广泛。新兴智能应用对AI芯片的算力和能效提出了更高的要求。存内计算技术通过将存储与计算深度融合,能大幅度降低冗余的数据搬运,有效提升AI芯片能效。在各种存储介质中,SRAM具有工作电压低、读写速度快、读写功耗低,工艺兼容性好等显著优势,近年来,基于SRAM的存内计算芯片在能效、算力等方面相比于传统架构取得了质的飞跃。不同应用场景通常需要不同的计算位宽以实现计算精度与能效的最优化。但当前基于SRAM的存内计算芯片仍然面临不同配置下的阵列利用率和能效损失等问题,导致其难以实现最佳的能效。

针对以上问题,中国科学院微电子研究所乔树山研究员团队设计了一款基于SRAM的数字可重构存内计算芯片。该存内计算芯片采用全数字设计,能够保证不同位宽配置下的精确计算。为实现不同位宽配置下的高利用率和高能效,团队提出了一种基于行计算的数字存内计算架构,该架构能够实现1-8bit内任意位宽下有符号/无符号计算,且在不同配置下均能实现极高的计算资源利用率。为了进一步提升系统的能效,团队对数字存内计算芯片中功耗占比最高的求和阵列进行了低功耗设计,提出了一种基于4-2压缩器的求和阵列,并采用定制化的设计方法设计了一款低功耗4-2压缩器,有效降低了求和操作的能耗。该存内计算芯片支持1-8bit的计算位宽,1bit乘累加峰值能效突破2238TOPS/W,4bit乘累加峰值能效突破44.82TOPS/W。

本工作以“A 1–8b Reconfigurable Digital SRAM Compute-in-Memory Macro for Processing Neural Networks”为题发表在集成电路顶级期刊IEEE Transactions on Circuits and Systems I: Regular Papers,微电子所乔树山研究员为通讯作者。

该研究得到了科技部科技创新2030重大项目、地方合作等项目的支持。

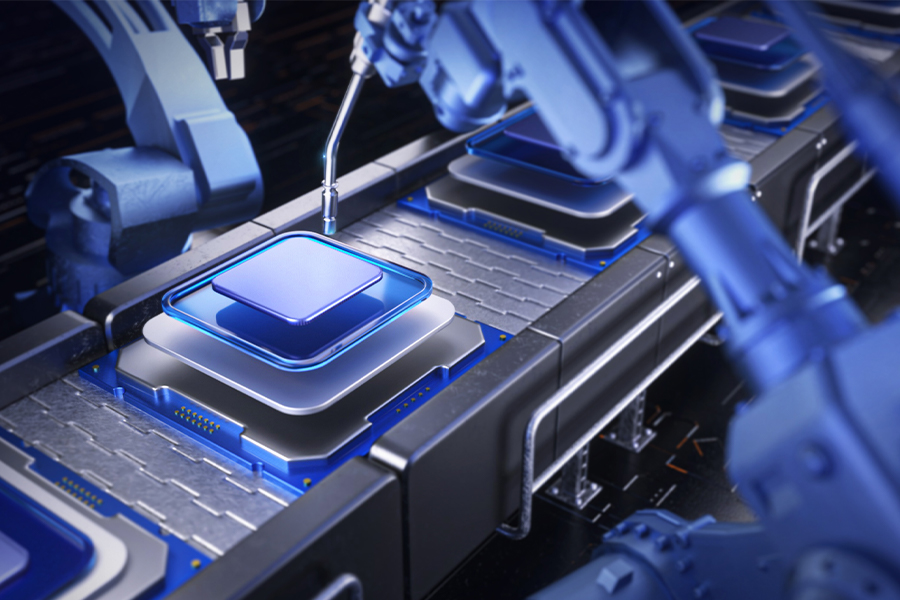

图1. 基于SRAM的可重构存内计算芯片显微照片及芯片参数

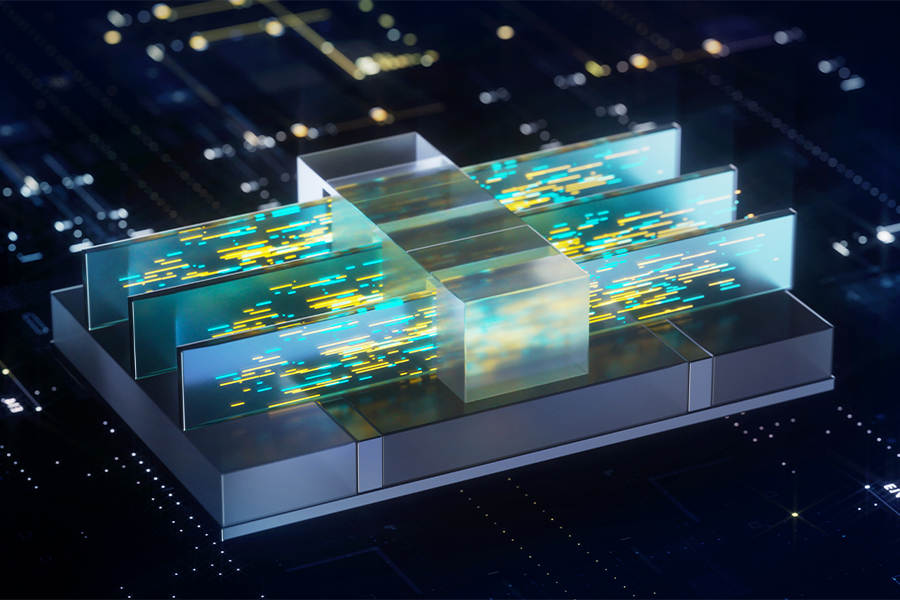

图2. 数字可重构存内计算芯片架构图