背景介绍

随着云计算和光通信网络的快速发展,为解决数据传输量和传输速度急速增加的需求,作为数字世界高速骨干网的关键基石,800G数字信号处理器(DSP)受到越来越多的关注。

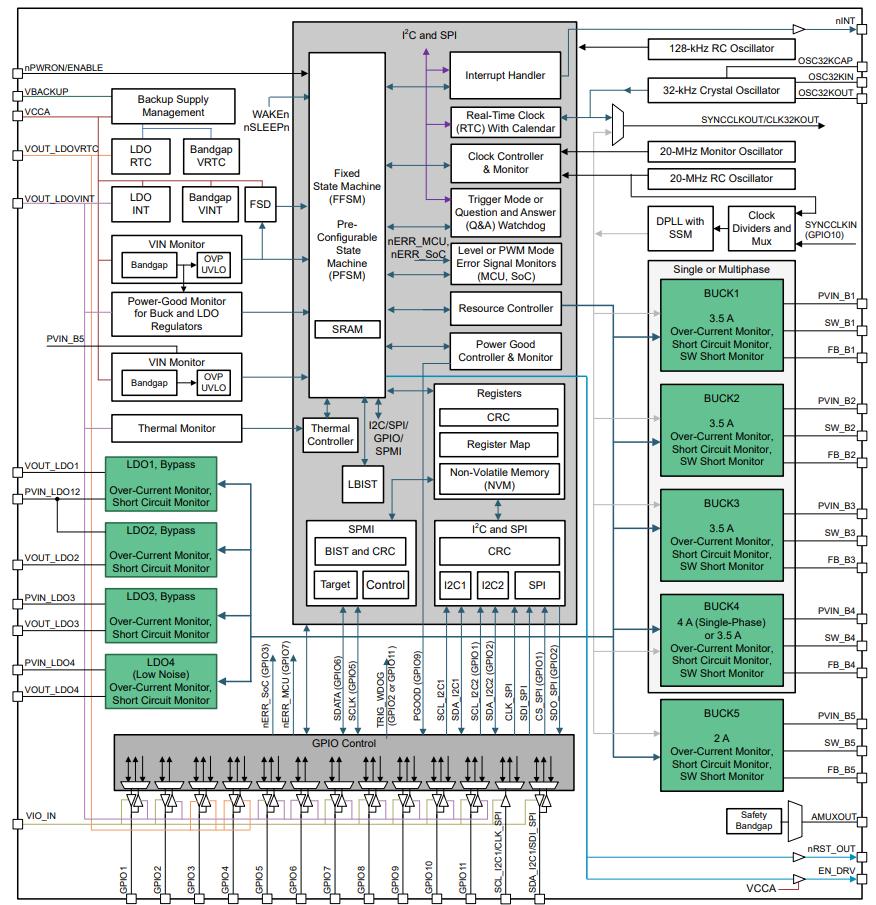

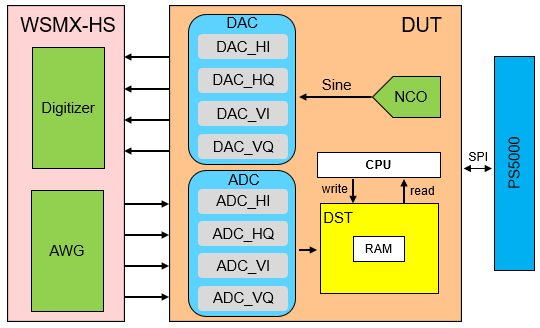

本文将聚焦800G DSP集成的一种高速模数/数模转换器(ADDA)芯片,深入其工作原理以及对ATE测试的挑战,探讨在量产测试阶段如何实现低成本、高效率的解决方案。如下图,是一种采用4x200G方案的800G DSP芯片结构框图。

挑战1:如何覆盖所有测试频率场景

测试频率范围广,本文中800G DSP的AD/DA的测试频率要从低频10MHz到高频70GHz+,但市场上无ATE(自动测试设备)可直接支持这些频率测试场景。所以,如何覆盖所有测试频率,是高速ADDA量产测试的首要挑战。

解决方案

针对该挑战,基于V93000,探索了一种满足所有测试频率的方案。

低频场景:使用WSMX-HS板卡

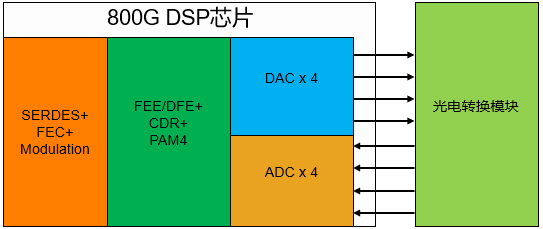

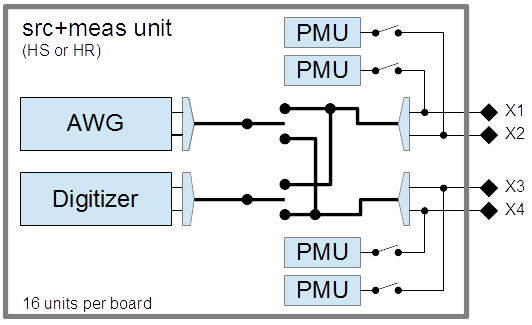

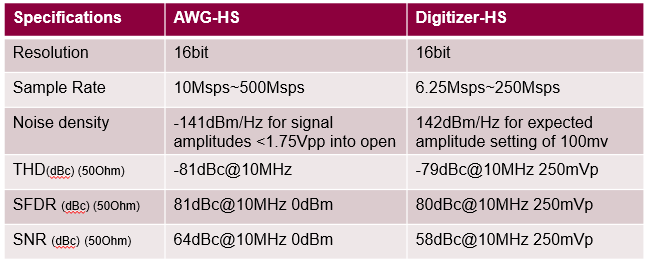

WSMX-HS板卡是一款高性能的混合信号测试板卡,它可以提供16组独立的模拟信号输入/输出资源;每组可提供一个AWG和一个Digitizer,可灵活连接两对差分端口;整张板卡共64个双向端口,支持差分或单端信号输入。其关键参数指标如下表:

低频场景的测试方案如下图,使用WSMX-HS有以下优点:可以单独调试芯片的ADC或DAC,有利于分析调试时遇到的问题;该项目中ADC/DAC的通道较多,且需要同时测试,对模拟资源需求量大,WSMX-HS板卡的16个独立Unit和64个port可以支持多site并测;在低频段,WSMX-HS板卡参数优于芯片的设计指标,相比回环方案,可测出芯片更真实的数据。

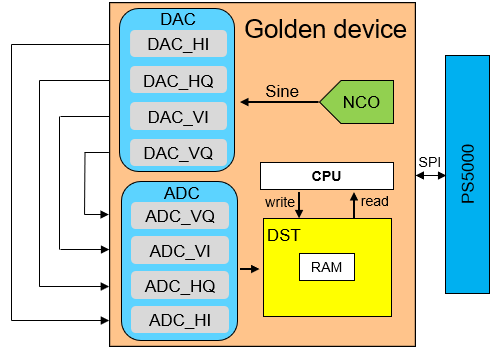

高频场景方案:外部自回环

使用外部自回环的方案进行高频测试,测试方案如下图。

该方案节省了测试机资源,可以做更多的site,节约测试成本;还覆盖了封装对测试结果的影响,实现了真正的“端到端”测试。

此外,V93000高度集成的电源板卡和数字板卡,为回环测试提供更高的稳定性和更低的系统噪声,提高测试结果的准确性。

为保障高频信号质量,可将高频场景和低频场景分开做Load Board,同时可以提高测试精度和测试良率;低频Load Board可以使用普通的线路板材料,降低硬件成本。

挑战2:如何消除交织杂散对测试结果的影响

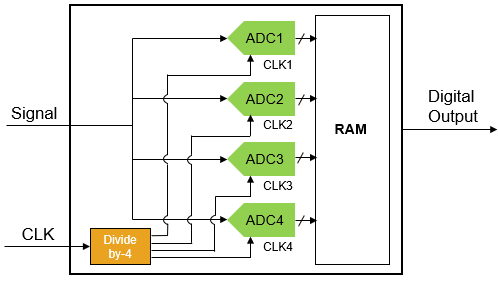

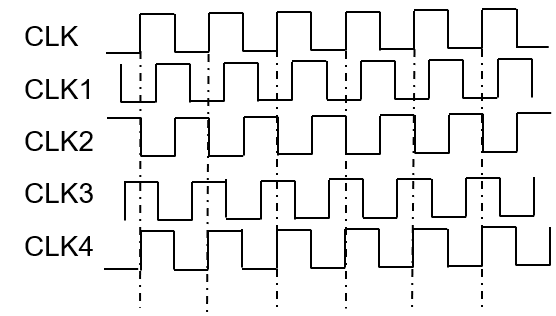

为满足高速信号采样的需求,高速ADDA芯片多采用时间交织(Time-Interleaved)结构,如下图是一种4个ADC通过时间交织技术组成的高速ADC。

时间交织技术是一种通过并联多个低速AD/DA、在时间上交错采样/输出的方式,以实现整体等效高速采样的技术。比如,采用4x200G方案的800G ADDA,4个200GSps的ADC以时间交织结构并联,并以90度相位间隔轮流采样,则可实现等效800GSps的采样率。

采用时间交织技术的高速ADDA,会存在通道间失配,包括增益不一致、相位误差、时钟偏移等,从而引入周期性的杂散信号(交织杂散),影响系统的动态性能,导致测试结果不准确。

采用自校准方案可以去除交织杂散,但需要复杂的前端校准机制来对齐多个子通道,校准算法复杂度高。每颗芯片都需要进行多轮校准与线性分析,导致自校准的时间很长,提高了量产测试成本。

解决方案

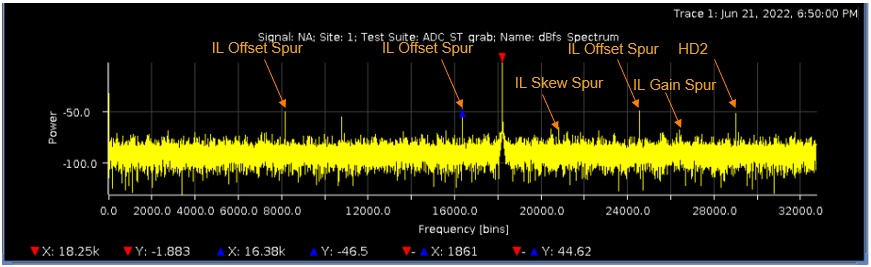

可以采用一种非校准式的后处理技术,无需在路径中校正失配,而是直接在频域对结果进行修复。其有效性建立在交织杂散频率位置可预测的基础上,即交织杂散的频率是固定的,与交织ADC的数量、交织后的采样率和输入信号的频率有关。

按照产生交织杂散的来源可分为四种,对应的交织杂散频率如下表。

M是交织ADC的数量,Fs是交织后的采样率,Fin是输入信号的频率,k=0,1,2,…

通过频率定位与频谱处理的方法,可以消除交织杂散对测试结果的影响,主要步骤如下:

根据交织ADC的数量、交织后的采样率和输入信号的频率,计算出交织杂散的理论频率;将芯片ADC采集的时域信号转到频域,并在交织杂散理论频点附近,找到真正的交织杂散,频谱上表现为孤立的尖峰;用附近的噪声功率,在频谱上替换交织杂散的功率,达到消除交织杂散的目的;最后,计算ADC的动态参数。

本方法已在实际项目中使用,测试结果与自校准方法的结果接近一致,还省去了若干秒的自校准的时间,有效地降低测试成本。

结语

凭借V93000 WSMX板卡和外部自回环方案,既可以提升高速ADDA测试结果的准确性,又可以满足多site的需求,利用扣除交织杂散的后处理技术,有效降低测试时间,解决了800G ADDA芯片的低成本的测试问题。