近日,南方科技大学工学院国家示范性微电子学院潘权团队在高速通信与光电集成电路设计领域取得重要进展,研究成果包括:一是首款工作在224 Gb/s PAM-4的单端收发器前端芯片;二是一款采用电流复用型AFE与单环路半速率无参考CDR的50 Gb/s PAM-4接收机,显著提升抖动容限与能效;三是一款面向VCSEL光链路应用的CMOS单片集成28 Gb/s PAM-4光接收机,在CMOS工艺上实现了单片集成方案。相关论文成果一和二分别发表于IEEE Journal of Solid-State Circuits(JSSC)、IEEE Transactions on Circuits and Systems I(TCAS-I),论文成果三将发表于Optical Fiber Communication Conference(OFC)2026。

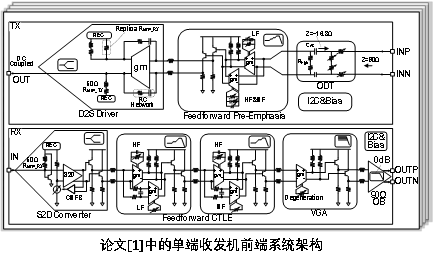

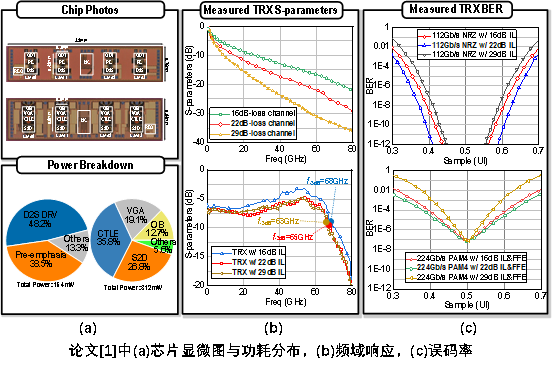

一款采用噪声抑制技术及级联均衡器的4×224Gb/s单端 PAM-4收发机前端

单端互连在长距离电互连中因具备高带宽密度和低时延等优势,已成为支持800GbE/1.6TbE等高速以太网标准的重要技术路径。然而,在向224 Gb/s/通道的目标推进时,单端链路面临高信道损耗、电源抑制能力弱、直流工作点失配及单端-差分转换失配等一系列关键挑战,成为制约其性能进一步提升的主要瓶颈。

本文提出了一种基于130-nm SiGe BiCMOS工艺的4×224 Gb/s直流耦合单端PAM-4收发器前端。该设计在发射端与接收端均采用伪差分结构并集成双环路稳压器,有效提高了电源抑制比。此外,针对接收端的单端至差分转换器,提出了一种电源反弹消除技术,可抑制76%的电源反弹噪声,使眼图宽度提升12%。为了应对高频损耗,接收端还采用了级联连续时间线性均衡器,结合发射极退化、分布式峰化技术与前馈低通分支,实现了对低、中、高频段的综合均衡,最高支持29 dB的损耗补偿。

测试结果表明,该收发器前端在224 Gb/s PAM-4模式下可实现2.08 pJ/b的能效,FoM值为0.07 pJ/b/dB,且在高达29 dB的通道损耗下仍能稳定工作。据作者所知,这是首款工作在224 Gb/s PAM-4的单端收发器前端,为下一代高带宽、长距离电互连系统提供了有效的模拟前端解决方案。

图1展示了单端收发机前端的电路架构图。图2(a),(b),(c)分别展示了提出的发射机芯片显微图与功耗分布、测试的频响结果,及测试的误码率曲线。

罗雄师为论文的第一作者。罗雄师是南科大2025届博士毕业生(也是南科大2019届本科毕业生,硕转博),目前就职于华为技术有限公司。该论文得到了国家重点研发计划等项目的资助。

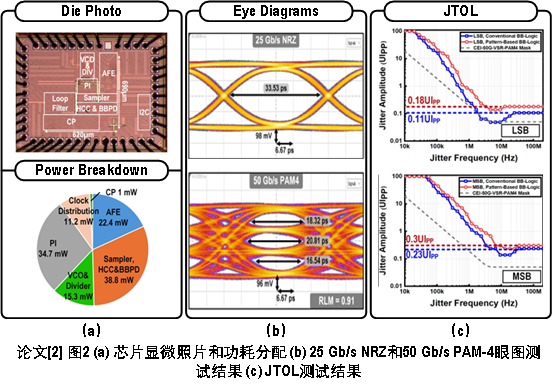

一款采用电流复用型AFE和单环路半速率无参考CDR的50Gb/s PAM-4接收机

随着云计算与人工智能应用的快速发展,数据中心对超高速、低功耗数据传输的需求日益迫切,高速SerDes芯片已成为实现该目标的关键基础模块。相较于传统NRZ信令,PAM-4信令在相同带宽条件下可实现双倍的数据传输效率,因而被广泛应用于新一代高速SerDes系统中。然而,PAM-4信令在提升调制效率的同时,也面临信噪比下降、非线性失真加剧以及抖动敏感性增强等一系列挑战,这些非理想因素将显著劣化信号质量并限制系统误码率(BER)性能。

本文基于40-nm CMOS工艺实现了一款面向VSR应用的50 Gb/s PAM-4接收机。为降低模拟前端(AFE)的功耗开销,设计中在AFE电路中引入了电流复用技术,在保证信号处理能力的同时显著提升了能效表现。针对PAM-4信令中非对称转换沿对恢复时钟抖动的不利影响,本文提出了一种基于码型滤波的Bang-Bang鉴相器(PB-BBPD),可有效滤除非对称转换沿引入的数据相关性抖动,从而降低恢复时钟抖动。此外,通过引入时钟相位选择技术,进一步增强了系统对频率误差的容忍能力,提高了接收机在实际应用环境下的鲁棒性。

测试结果表明,该接收机在50 Gb/s PAM-4模式下实现了2.47 pJ/b的能效,对应FoM为0.29 pJ/b/dB。开启码型滤波技术后,MSB与LSB的抖动容限(JTOL)性能分别提升30%和63%,恢复时钟的RMS抖动为325 fs,整体性能优于同类已报道工作。该研究为高性能、低功耗PAM-4 SerDes接收机的设计提供了一种具有实用价值的技术方案。

图1展示了50 Gb/s PAM-4接收机的电路架构图。图2(a),(b),(c)分别展示了接收机芯片显微图与功耗分布、测试的眼图结果,及测试的JTOL曲线。

李正浩为论文的第一作者。李正浩是南科大2025届博士毕业生(也是南科大2020届本科毕业生,直博),目前就职于华为技术有限公司。该论文得到了深圳市科技重大专项项目的资助。

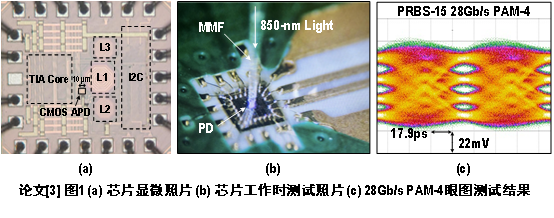

一款面向VCSEL光链路应用的CMOS单片集成28Gb/s PAM-4接收机

近年来,具有850 nm波长的垂直腔面发射激光器(VCSEL)凭借其高带宽连接特性,在数据中心得到广泛应用。新兴的共封装光学器件(CPOs)采用 VCSEL 技术,可进一步缓解异构集成光模块在可扩展性和功耗方面的挑战。为降低对应光模块的封装复杂度并降低成本,在光接收机前端中,业界采用CMOS片上光电探测器(PD)替代III-V族PD,从而缩短光器件到跨阻放大器电路的传输距离,避免封装寄生效应,实现光器件与专用集成电路(ASIC)的全集成。然而,这种全集成接收系统的主要性能瓶颈仍在于CMOS PD的响应度与带宽,并显著限制系统的速率和误码率。

本文基于28-nm CMOS工艺实现了一款面向VCSEL光链路应用的28 Gb/s PAM-4接收机该芯片将PD和跨阻放大器电路集成在一块芯片上,在CMOS工艺上实现了单片集成方案。芯片采用10um×10um受光面积的PD,通过横向插指和浅沟隔离等技术突破了CMOS PD带宽、响应度低等技术瓶颈。同时,在跨阻放大器电路中采用全反相器设计,并插入精心设计的级间电感,显著降低功耗和带内噪声。

该研究为低成本、低功耗的高速光接收机设计提供了一种具有实用价值的技术方案。

图1(a),(b),(c)分别展示了28 Gb/s PAM-4单片集成光接收机芯片显微图、测试照片和测试的眼图结果。

詹东深为论文的第一作者。詹东深是南科大在读硕士研究生(也是南科大2023届本科毕业生)。该论文得到了深圳市科技重大专项的资助。