1.意大利起诉亚马逊及四名高管!涉嫌逃税12亿欧元;

2.Groq敦促三星晶圆代工扩大4nm AI芯片产能,增加67%;

3.三星计划将2nm工艺应用于HBM4E基础芯片;

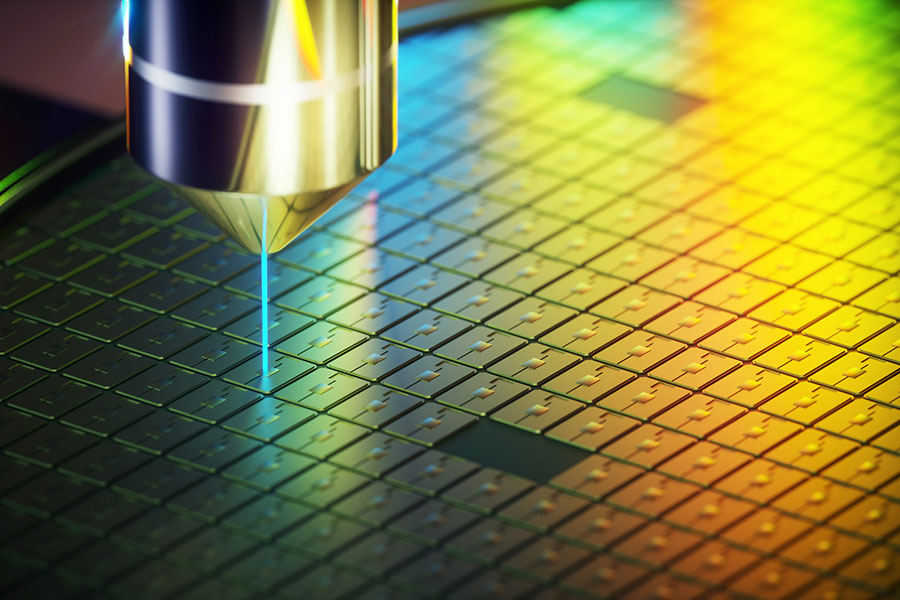

4.IBM、泛林集团利用High NA EUV及干法光刻胶,研发1nm以下制造工艺;

1.意大利起诉亚马逊及四名高管!涉嫌逃税12亿欧元;

知情人士透露,意大利检察官已要求对亚马逊欧洲部门及其四名高管进行审判,罪名是涉嫌逃税约12亿欧元(约合13.8亿美元)。

此举在意大利此类案件中尚属首次,因为亚马逊已于去年12月同意向意大利税务局支付5.27亿欧元(含利息)以了结这场税务纠纷。

以往涉及其他国际集团的类似案件中,一旦达成和解并完成付款,检察官通常会通过认罪协议或撤销案件的方式终止相关刑事调查。

但此次意大利检察官并未采纳税务机关的处理方式,决定继续推进调查,并最终要求将嫌疑人送上法庭受审。

2025年12月达成税务和解后,亚马逊表示将“捍卫自身在这起可能毫无依据的刑事案件中的立场”。该公司还称,“不可预测的监管环境、过重的处罚以及漫长的法律诉讼,正日益削弱意大利作为投资目的地的吸引力。”

目前,法官将确定预审听证会的日期,以决定是否对被告提起公诉或驳回案件。

意大利检察官与税务警察已对这四名高管及总部位于卢森堡的亚马逊欧盟公司展开调查,罪名是涉嫌在2019年至2021年期间,在意大利的在线销售业务中规避增值税。

指控文件显示,亚马逊算法和运营模式使得数万名非欧盟卖家得以在意大利销售商品,却未披露其身份,进而帮助这些卖家规避了增值税缴纳。

根据意大利法律,在意大利提供商品销售服务的中介机构,需对通过其平台运营的非欧盟卖家未缴纳的增值税承担连带责任。

检察官在提起诉讼的要求中,将意大利经济部列为受害方。

知情人士表示,若相关指控在法庭上成立,可能会对亚马逊在欧洲的商业模式构成威胁,因为增值税是欧盟统一征收的税种。

这是亚马逊在意大利面临的多起案件之一。

欧洲检察官办公室(EPPO)正在调查该公司2021年至2024年期间涉嫌的同类违法行为。(校对/赵月)

2.Groq敦促三星晶圆代工扩大4nm AI芯片产能,增加67%;

据报道,因AI芯片需求持续激增,Groq已向三星电子晶圆代工部门提出要求,增加其推理AI芯片的晶圆产量,这一举措也反映出当前市场需求的蓬勃态势。业内消息人士预计,三星晶圆代工业务将通过深化与Groq的合作、扩大产能,进一步提升盈利能力。

Groq计划将2025年在三星晶圆代工的晶圆订单,从约9000片增加至约1.5万片,增加近67%。

分析人士指出,2025年的订单量主要用于生产样品芯片,这些芯片将用于验证实际场景中的AI推理应用,而大规模商业化量产则将于2026年启动。

尽管Groq的订单规模仍相对有限,但三星晶圆代工正积极争取此类合同,以期在推理AI芯片领域站稳脚跟。除Groq外,韩国初创企业HyperAccel的处理器生产也完全依赖三星晶圆代工。目前,三星正采用4nm工艺节点,为这两家公司生产AI芯片。

业内知情人士透露,三星为Groq AI芯片量身打造的4nm工艺,进行了重大改进以提升芯片性能。鉴于该工艺节点成本较高,且行业对4nm及5nm工艺的需求十分强劲,对正与台积电竞争的三星而言,争取到此类订单具有重要的战略意义。

与此同时,市场对英伟达计划在2026年GTC大会上推出基于Groq AI设计的专用推理芯片,预期不断升温。

市场观察人士预测,英伟达将采用Groq的架构,但会将高带宽内存(HBM)替换为静态随机存取存储器(SRAM)。据报道,这一调整有望加快数据传输速度、提升芯片能效,同时降低芯片成本。

英伟达的AI芯片相关计划与Groq的产能扩张形成双重势头,预示着推理AI芯片市场未来将迎来强劲增长。(校对/赵月)

3.三星计划将2nm工艺应用于HBM4E基础芯片;

在半导体竞争中,三星电子正强化其“集成器件制造商(IDM)”战略,该战略融合了存储器和晶圆代工的能力。作为全球DRAM领导者和第二大晶圆代工企业,三星电子计划将2nm工艺应用于下一代HBM(高带宽存储器)的基础芯片,从而提升其技术竞争力。这种集存储器、逻辑和封装于一体的结构正在成为人工智能(AI)半导体时代的关键优势。

据业内人士透露,三星电子正在评估将2nm工艺应用于第七代HBM4E基础芯片的可能性。HBM由垂直堆叠的DRAM核心芯片和作为控制器的基础芯片组成。基础芯片位于HBM底部,用于控制电源和信号。

在HBM3E之前,基础芯片主要负责简单的控制功能;但从HBM4开始,其重要性显著提升,因为它现在直接处理一些计算任务。为了提高计算效率和能源管理效率,基础芯片中的逻辑功能得到了增强,并且采用代工工艺的结构也得到了广泛应用。

为了提升HBM4的性能,三星电子从三星晶圆代工获得4nm逻辑基础芯片,以及其最先进的1c DRAM(第六代10nm级工艺)。这项技术比台积电的12nm工艺领先数代。

随着基础芯片工艺的不断改进,其能效和散热性能将得到显著提升。此外,随着面积效率的提高,可以在有限的空间内集成更多功能。这为实现根据客户需求定制的HBM奠定了基础。

半导体行业预计,从HBM4E开始,将出现大规模的客户定制HBM。台积电也表示,计划从“定制HBM4E”开始采用其最新3nm工艺。

三星电子正在评估的“2nm基础芯片”似乎是一种策略,旨在通过应用领先一步的工艺,即使在HBM4E领域也能保持技术优势。三星电子计划在年中发布标准HBM4E,并在下半年根据客户的进度安排,进行定制产品的首批晶圆流片。

通过在其晶圆代工厂生产HBM基准芯片,三星电子除了提升性能外,还能获得其他诸多益处。三星晶圆代工厂可以确保稳定的客户群,从而提高晶圆厂的利用率,并且预计产量的增加也将带来良率的提升。

尤其值得一提的是,2nm工艺预计将在确保目前正在美国得克萨斯州建设的泰勒晶圆厂的利用率方面发挥重要作用。三星泰勒晶圆厂的设备安装工作已经开始,首片晶圆预计将于2026年底前完成流片。首批产品预计将于2027年初出货。近期,三星也已开始招聘2nm工艺工程师加入泰勒晶圆厂。

三星晶圆代工近期接连获得2nm工艺订单,进一步提升了市场预期。继采用第一代2nm工艺的Exynos 2600之后,第二代2nm工艺将应用于Exynos 2700。据报道,三星已向特斯拉订购的AI6芯片预计也将采用2nm工艺。

三星的重点在于通过大规模生产实现规模经济并提高盈利能力。据报道,2nm工艺的良率也超出内部预期。三星电子还在评估将低利用率的旧工艺转换为先进封装工艺的计划,以提高生产效率。

今年2月,三星电子总裁兼首席技术官Song Jae-hyuk表示:“在存储器、晶圆代工和封装方面拥有竞争力对于制造人工智能半导体非常有利,这种竞争力正在创造协同效应。”(校对/赵月)

4.IBM、泛林集团利用High NA EUV及干法光刻胶,研发1nm以下制造工艺;

IBM和泛林集团宣布达成一项为期五年的合作计划,双方将利用高数值孔径(High NA)EUV光刻技术和泛林集团的Aether干法光刻胶技术,开发将逻辑芯片尺寸缩小至1nm以下所需的材料和制造工艺。该项目将在位于纽约州奥尔巴尼市的IBM研究院进行。

两家公司已合作超过十年,共同推进7nm工艺开发、纳米片晶体管架构以及早期EUV工艺集成。作为双方持续合作的一部分,IBM于2021年发布了全球首款2nm节点芯片。根据新协议,双方将重点转向验证纳米片和纳米堆叠器件架构以及背面供电的完整工艺流程,使用泛林集团的Kiyo和Akara刻蚀平台、Striker和ALTUS Halo沉积系统以及Aether干法光刻胶。

传统的极紫外(EUV)光刻技术依赖于化学放大光刻胶,这种湿法工艺材料难以满足High NA EUV光刻机对精度的严格要求。而泛林集团的Aether技术是一种干法光刻胶,它通过气相前驱体沉积而非旋涂,并采用基于等离子体的干法工艺进行显影。

Aether的金属有机化合物吸收的EUV光量是传统碳基光刻胶材料的3~5倍,这降低了每次晶圆曝光所需的曝光剂量,并有助于在先进节点上保持单次印刷图案化,而无需采用成本更高的多重曝光技术。2026年1月,泛林集团宣布Aether已被一家领先的存储器制造商选为其最先进DRAM工艺的生产工具,但并未透露该制造商的名称。根据联合公告,此次合作旨在实现High NA EUV光刻图案以高良率可靠地转移到实际器件层,并加速业界采用High NA EUV光刻技术,用于下一代互连和器件图案化。在转移良率方面,泛林集团的Aether干法光刻胶技术优于传统的湿法工艺,因为光刻和刻蚀之间的步骤更少,这意味着在更精细的几何形状下,图案劣化的可能性更小。

同时,纳米片晶体管通过堆叠多层薄硅片来提高驱动电流,而无需扩大器件尺寸。双方团队将构建并验证纳米片和纳米堆叠器件的完整工艺流程,以及背面供电技术。背面供电技术通过晶圆背面供电,从而释放正面互连层用于信号布线。

双方表示,这些技术共同的目标是实现High NA EUV光刻图案以高良率可靠地转移到实际器件层,从而实现持续的尺寸缩小、性能提升,并为未来的逻辑器件提供可行的量产路径。(校对/赵月)