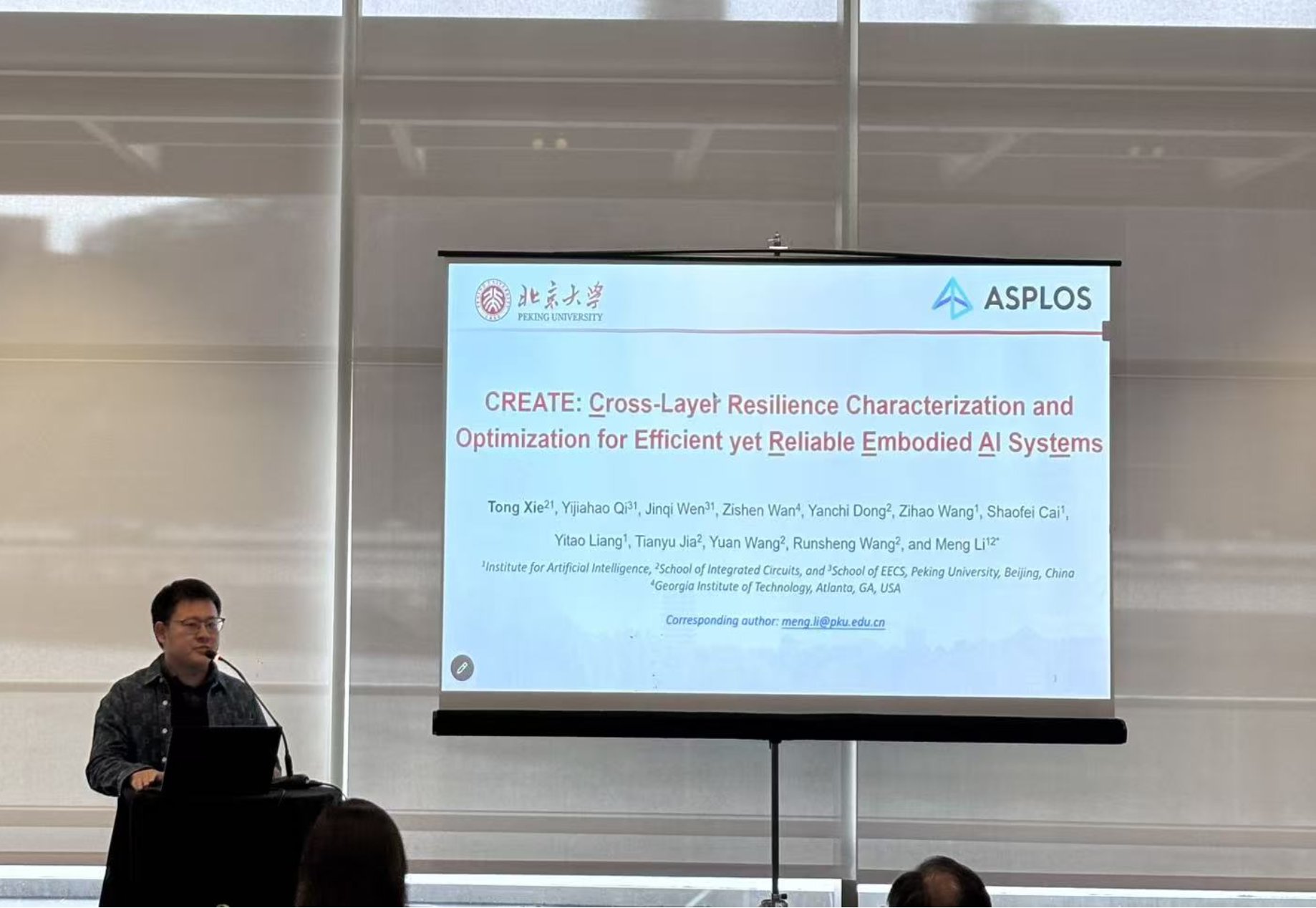

2026年3月22日至3月26日,ASPLOS 2026(ACM International Conference on Architectural Support for Programming Languages and Operating Systems)在美国匹兹堡召开。在本次大会上,来自全球学术界与产业界的专家分享了计算机体系结构及相关领域的最新研究成果,讨论了体系结构未来发展的挑战与方向。北京大学集成电路学院的多位师生现场参加了本次大会,进行了成果展示、汇报与交流。在本次大会上,北京大学集成电路学院/集成电路高精尖创新中心共2篇论文入选,入选论文具体介绍如下:

一、基于等价图反合一的可重用拓展指令发现

随着AI、DSP等计算密集型应用的发展,通用处理器已难以同时满足性能与能效需求,基于RISC-V开放指令集扩展的定制指令成为实现领域专用加速的重要路径。然而,现有自动化方法主要依赖程序热点的语法级模式识别,仅能合并表面相似的指令序列,导致生成指令复用性低、过度特化,难以跨代码位置乃至跨应用复用,从而限制性能收益与硬件资源效率。针对上述问题,梁云教授团队提出ISAMORE框架,首次实现面向可复用性的定制指令自动发现。该方法基于等价图(e-graph)与反合一(anti-unification),通过等价饱和捕获程序语义空间,并提取跨程序共享的语义模式,实现指令跨应用复用。为缓解组合爆炸问题,ISAMORE设计了分阶段迭代流程及基于结构相似性筛选与模式采样的智能反合一机制,显著提升可扩展性;同时结合模式向量化与硬件感知成本模型,在性能与面积之间实现有效权衡。(该工作以《Finding Reusable Instructions via E-Graph Anti-Unification》为题发表并获最佳论文奖,博士生肖有为为第一作者,梁云教授为通讯作者)。

二、具身智能系统的容错与能效协同优化

将基于大小脑分层架构的具身智能系统部署在边端设备上面临着严峻的能耗挑战。尽管降低工作电压可以显著提升能效,但这会引入计算错误,导致严重的任务性能退化。为了在不牺牲任务质量的前提下实现可靠且高效的具身智能体部署,李萌研究员-王润声教授团队对基于大小脑分层架构的具身智能系统进行计算容错性表征。表征发现,具身大脑模型的容错性显著差于具身小脑,其原因在于大脑模型的激活值中存在系统性离群值;具身小脑模型的容错性随子任务和执行状态动态变化。利用这种容错性,研究团队进一步提出了面向高效且可靠具身智能系统的跨层协同优化设计原则CREATE。CREATE在电路层提出了一种异常检测与清除机制,以消除由时序违例引起的极大离群点错误。在模型层,该设计针对具身大脑模型提出了一种权重旋转优化,通过调整大模型中的激活值数据分布来大幅提升其容错能力。CREATE进一步在应用层引入了自适应的动态电压调节技术,根据当前子任务的需求与执行状态灵活调整小脑模型的运行电压。相对于额定电压基线与现有最先进技术,CREATE在不牺牲任务质量的前提下,分别可实现平均40.6%和35.0%的计算能耗节省。这进一步带来了29.5%至37.3%的芯片级能耗节省,并预期可以将系统的整体续航时间提升约15%至30%。(该工作以《CREATE: Cross-Layer Resilience Characterization and Optimization for Efficient yet Reliable Embodied AI Systems》为题发表,集成电路学院博士生解同为第一作者,李萌研究员为通讯作者)。

ASPLOS会议背景简介

ASPLOS会议全称为ACM International Conference on Architectural Support for Programming Languages and Operating Systems,是计算机体系结构领域的顶级学术会议,与ISCA、MICRO和HPCA并称计算机体系结构领域的“四大会”。它综合体系结构、编程语言和操作系统等领域,并且重视各领域间的交叉。该会议曾推动了多核处理器、虚拟化、RAID、RISC、深度学习处理器等计算机系统领域的核心创新,在学术界和工业界拥有显著的影响力。本届会议共收到1048篇投稿,录用152篇,接收率14.5%,创二十年来新低。