先进封装—SiP

随着晶圆代工制程不断缩小,摩尔定律逼近极限,先进封装是后摩尔时代的必然选择,据Yole数据显示,2021年全球先进封装市场总营收达321亿美元,同比增幅高于2020年。预计到2027年,全球先进封装市场总营收将增长至572亿美元,年复合增长率将达到10%。其中,2.5D/3D堆叠IC是增长最快的技术。

SiP(System in Package,系统级封装)是基于SoC的一种新型的封装技术,它将一个或多个裸片及无源器件构成的高性能模块封装在一个壳体内。这些芯片和器件以2D、2.5D或3D的方式整合在一个衬底上,并具备一个系统的功能从而使封装由单一芯片进入系统级芯片。

从集成度而言,一般情况下, SoC 只集成 AP 之类的逻辑系统,而 SiP 集成了AP+mobile DDR,某种程度上说 SIP=SoC+DDR,随着将来集成度越来越高, emmc也很有可能会集成到 SiP 中。

(图片来源:wiki)

随着消费者对便携式产品的需求愈加广泛,SiP技术在WIFI、蓝牙、内窥镜胶囊、数码相机的CMOS影像传感器以及军事设备,如雷达系统等众多领域得到了应用。

SiP涉及多种新型封装技术,如超紧密度SMT、PoP/PiP技术、超薄晶圆处理、嵌入式技术、芯片堆叠技术、芯片倒装技术以及硅穿孔技术(TSV)等。

硅通孔封装(Through Silicon Via, TSV)

上图显示了一个典型的3D 封装芯片结构,其包含TSV, C4 Bump, BGA球等,其封装失效点可能出现在PCB引线、封装引线、硅中介层(Si Interposer)、TSV、Micro-bump等。

其中,硅通孔封装(Through Silicon Via, TSV)互连是集成电路中一种系统级架构的新方法,是2.5D和3D封装中堆叠芯片实现互连的关键技术解决方案。

TSV可堆叠多片芯片,在芯片钻出小洞,从底部填充入金属, 硅晶圆上以蚀刻或激光方式钻孔,再以导电材料如铜、多晶硅、钨等物质填满。TSV能够使芯片在三维方向堆叠,通过垂直互连减小互联长度,减小信号延迟,降低芯片的电容和电感,实现芯片间的低功耗高速通讯,增加宽带和实现器件集成的小型化,是公认的第四代封装互连技术。

随着3D集成成为微电子封装的主流,芯片的体积越来越小,而集成度越来越高,对失效分析手段提出了挑战,也对故障高分辨率定位能力的需求逐渐增大。

对于TSV封装来说,如果组成垂直结构的一部分失效,则必须丢弃整个结构,这会使通过TSV互连的芯片系统制造起来更加昂贵。对于失效位置的精确定位成为TSV芯片失效分析迫切解决的问题。

芯片失效分析与太赫兹电光脉冲反射

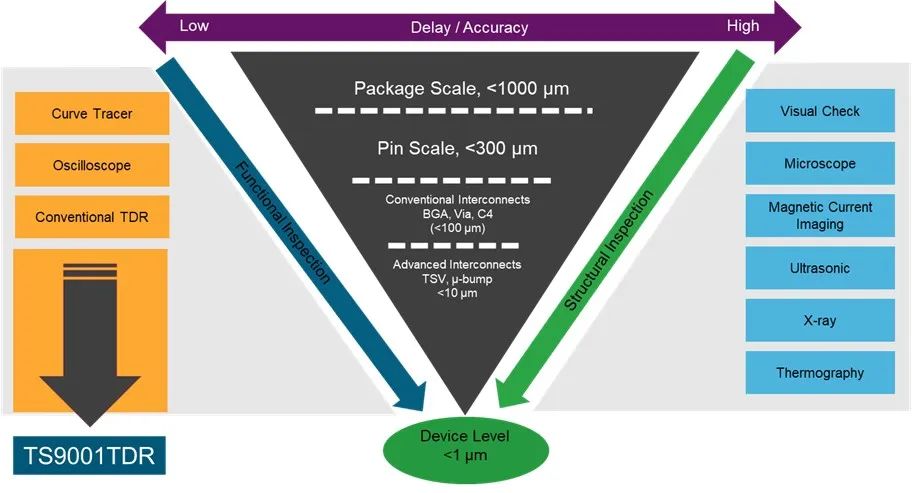

失效分析一般包括结构分析和功能分析(参见下图),结构分析是使用光、声、电、热等方法分析芯片的物理性能,比如显微镜观测,超声成像,3D X-ray, 热成像等;功能分析利用外加电流源、射频信号等方法分析芯片的电性能,常用的技术包括I-V曲线测量,示波器,常规的时域反射计等。对于小于100um的先进封装,传统的电性能分析分辨率无法满足要求,需要全新的芯片缺陷定位方法。

采用太赫兹电光采样技术的脉冲时域反射计,可以对芯片TSV封装失效点进行精准定位,其原理如图 2 所示。

飞秒激光源产生的光脉冲通过光电导开关换成太赫兹脉冲信号,通过射频探针尖端和芯片管脚接触,产生的太赫兹脉冲传播到芯片中的金属引线中。脉冲信号在芯片内部传输过程中,会在焊盘等各个不连续点部分反射脉冲信号,同样如果引线在特定点被破坏,则会产生更强的反射脉冲信号。反射的高频脉冲信号将由光电导开关被相干探测。与传统的基于示波器的TDR相比,基于太赫兹电光脉冲反射仪通过飞秒激光源发出的超短脉冲信号,大大提高了测量带宽和分辨率,失效位置定位分辨率可达5um。

图2 太赫兹电光脉冲反射仪对芯片失效定位的测量原理