(文/王丽英)从英特尔创始人戈登·摩尔提出开始,摩尔定律在过去的50多年里一直指导着半导体行业的发展,今天的计算机芯片可以在一块大小与你的拇指指甲差不多的正方形硅上集成数十亿个晶体管。但随着晶体管技术逼近物理极限,要想在芯片上集成更多晶体管难上加难,许多工业界和学术界的专家都预测摩尔定律会消亡。

但英特尔不这么认为,多年来一直在用创新技术推动摩尔定律发展。最近,半导体全球顶级会议-IEDM 2022(2022 IEEE国际电子器件会议)上,英特尔发布了多项突破性研究成果,将在未来十年内持续推进摩尔定律,预计到2030年可实现在单个封装中集成一万亿个晶体管。尤其是其中的两项革命性技术:新的3D混合键合(hybrid bonding)技术以及推动晶体管尺寸进一步缩小的新型超薄2D材料技术引发业界广泛关注。

英特尔在官方宣传中介绍了这两项技术进展:

通过下一代3D封装技术实现准单片(quasi-monolithic)芯片:通过混合键合技术将互连间距继续微缩到3微米,英特尔实现了与单片式系统级芯片(system-on-chip)连接相似的互连密度和带宽,与IEDM 2021上公布的成果相比,英特尔在IEDM 2022上展示的最新混合键合研究将功率密度和性能又提升了10倍。

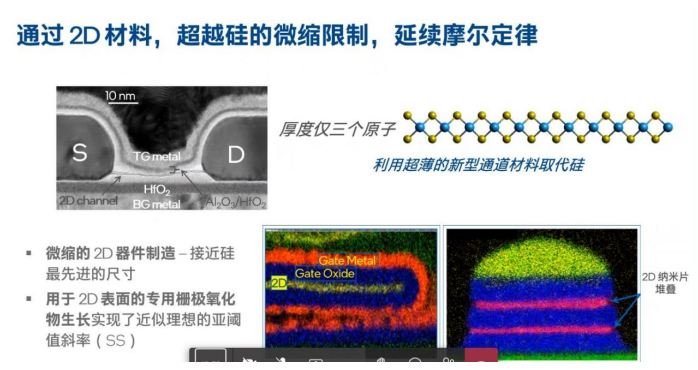

通过超薄“2D”材料,在单个芯片上集成更多晶体管:英特尔展示了一种全环绕栅极堆叠式纳米片结构,使用了厚度仅三个原子的2D通道材料,同时在室温下实现了近似理想的低漏电流双栅极结构晶体管开关。这是堆叠GAA晶体管和超越硅材料的固有限制所需的两项关键性突破。 研究人员还展示了对2D电接触材料的拓扑结构的首次全面分析,有望为打造高性能、可扩展的晶体管通道进一步铺平道路。

准单片是英特尔创造的一个新名词,通过下一代3D封装技术实现准单片是制造集成万亿晶体管的一个关键技术,英特尔是如何实现3微米互联间距进而实现准单片芯片的?

英特尔中国研究院院长宋继强解释说,从晶圆制造出裸片后,再进行封装,这本是两个不同的环节,其中所使用的材料、工艺以及工厂的参数要求都是不同的,但为了提升集成度,要把多个芯片集成在一起制作出封装级的芯片,就需要将原来封装厂做的一些工作转移到芯片制造工厂来做,一个就是混合键合技术。混合键合技术下,芯片之间是不用焊锡的,采用铜互联,芯片间填充物用oxide fill无机氧化物替换传统封装厂所使用的有机材料,英特尔通过诸多工艺材料方面的创新研究,将互联间距从去年的10微米缩小到3微米,大大提升了密度。另外,3D封装中堆叠的芯片之间以前是通过TSV技术在硅上过孔,英特尔创新性地采用在绝缘层过孔,解决了原来TSV硅通孔下的功率和信号完整性问题,这样,通过新材料的引入以及新连线工艺的开发,带宽也得到显著提升。宋继强认为,准单片技术的发展,预示着未来封装和芯片制造之间的界限正变得逐渐模糊。

既然3D封装下可实现高集成度的准单片芯片,是不是就可以不再依赖工艺制程提升了?在宋继强看来,绝非如此。他指出,先进制程是基础,没有持续微缩的晶体管技术,单靠先进封装是不够的。他透露,目前最好的先进封装混合键合方式下,互联间距可以做到3微米,而先进制程下,单芯片内部互联线宽间距一般在100纳米以下,所以仍存在1-2个数量级的差距,但比之前的好几个数量级的差距有了显著提升,这也是为什么可以称为准单片的原因。在宋继强看来,仍然要坚持先进封装和先进制程工艺两条路径发展,齐头并进。

在推进晶体管继续微缩技术上,英特尔此次展示了一项全新的材料和工艺创新,基于厚度仅三个原子的2D通道材料,实现性能更优异的全环绕栅极堆叠式纳米片结构。

据悉,目前晶体管结构正从FinFET向GAA发展,目的就是要进一步缩小晶体管尺寸,在相同面积的芯片中以集成更多的晶体管。宋继强指出,在GAA结构下进一步微缩,当源极和漏极间距缩小时,短沟道效应显现,出现漏电流及不易控制通断等问题,用传统的硅材料去做通道材料面临诸多挑战,新材料的探索便应运而生了。目前业界看好的一种材料是过渡金属硫化物,它是一种2D材料,有助于形成超薄的结构。英特尔基于这种材料进行了持续研究,使用了厚度仅三个原子的2D通道材料,在室温下实现了近似理想的低漏电流双栅极结构晶体管开关,为堆叠GAA晶体管提供了关键技术突破。

宋继强表示,目前业界已能实现在单个设备上集成千亿个晶体管,要从现在到2030年提升10倍增加到万亿个晶体管,仍面临不小的挑战,要实现这一激进目标,一方面需要继续依靠晶体管微缩技术,另一方面要通过先进封装技术,英特尔此次发表的新型超薄2D材料、新型3D混合键合技术等创新技术为实现这一宏大目标提供了切实可用的技术保证,将推动摩尔定律继续向前演进。

评论

文明上网理性发言,请遵守新闻评论服务协议

登录参与评论

0/1000