随着数字芯片设计规格日趋复杂、市场竞争愈发激烈,芯片设计成本和流片费用随之大幅提升,Time to Market不断加快。在这种背景下,如何保证产品能够在计划的时间内完成、尽可能地降低成本与风险已经被越来越多的芯片设计公司所重视。

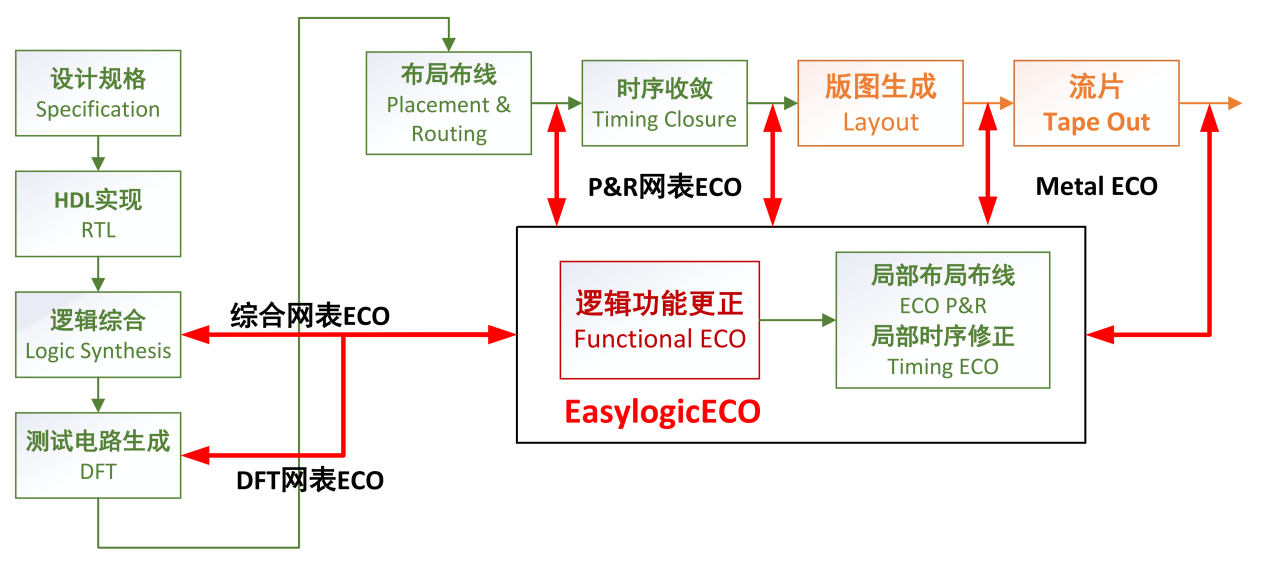

当遇到意料之外的逻辑功能变更需求时(这可能是由于设计工程师发现了在RTL代码中存在之前没有注意到的隐藏错误或者是用户需求出现了变化所致),由于自动化Functional ECO工具可以对当前设计阶段的电路网表直接进行逻辑变更、避免整个设计流程重头来过、甚至避免重新流片造成巨大损失,在现今数字芯片设计流程中,其必要性日益显现。

由于Functional ECO是一个技术门槛极高的细分领域,因此一直以来市面上都还没有一款成熟可靠的自动化Functional ECO工具,大多数芯片设计公司还在手工ECO流程中苦苦挣扎。而奇捷科技守正出奇,凭借其在形式验证、逻辑综合、逻辑优化、逻辑变更等多方面扎实的数字芯片设计前端技术积累,深耕近10年时间,研发推出了在性能与易用性等多方面都深受客户好评的自动化Functional ECO工具EasylogicECOTM,赢得了海内外众多知名芯片设计公司的认可,解决了困扰芯片设计公司多年的痛点。

专业自动化Functional ECO工具需求走高

随着芯片设计的复杂度不断提高,项目周期越来越紧迫,设计工程师很难保证在RTL代码Freeze后能够100%不需要再度进行修改。如果每次RTL代码修改都需要重新完成全部设计流程,则项目进度往往会大幅延迟,使得产品发布时间受到严重影响,人力和资金成本大大增加,对市场影响巨大。而ECO则可以完美地解决上述问题,因此产业界对高效能ECO工具的需求也日益迫切。

Functional ECO的价值体现在可避免重做全部设计流程,通过在电路网表中嵌入一个逻辑补丁的方式,快速修复原有Bug,将原来需要耗时数月的重做流程缩短至几天之内就可完成,从而有效地控制项目周期,减少项目延迟,对芯片设计企业具有重要的战略价值。

除此之外,随着近些年用户需求不断涌现,对Functional ECO的需求也变得越来越多样化。“如有客户要求在对逻辑功能进行变更的同时也要进行DFT扫描链的变更(DFT ECO);还有客户要求在低功耗设计中对于功耗设计部分进行变更(UPF ECO);更有甚者要求通过ECO的方式来完成产品改版升级(Design upgrade)等等。大量新需求的涌现,表明Functional ECO已是不可或缺的芯片迭代技术。”奇捷技术支持副总经理Kager(蔡宗智)总结道。

Kager的这一深刻洞察与其自身丰富的职业履历密不可分。Kager拥有18年CAD业界工作经验, 曾任职于矽统(SiS)、晨星(MStar)、联发科(MTK)、Cadence等企业,擅长ASIC设计的前端工具流程,尤其是形式验证及ECO相关应用。 在2021年加入奇捷科技之后,不仅参与了奇捷科技ECO产品很多先进功能的研制,还协助众多客户在设计环境中完美导入ECO设计流程。

奇捷技术支持副总经理Kager(蔡宗智)

“现有的自动化Functional ECO工具在技术上都还存在着不少问题。”Kager进一步分析说,“目前市面上的Functional ECO工具其实大多只是一个形式化验证(Formal Verification)工具的插件,并非专门针对Functional ECO所研发,因此受验证工具特性影响较大,功能相对受限,可以说是先天不足。具体表现就是工具往往运行时间很久,自动化程度有限,客户用起来非常不方便,结果也不尽如人意。可以说,目前业界迫切需要一个专业全能型的自动化Functional ECO工具,而不是从其他既有产品再衍生出来的副产品。”

但要真正做到这点并非易事。Kager认为,Functional ECO的特性决定了工程师并不会像验证工具那样被经常使用,而是关键时刻用来救命,这就导致工程师不大可能通过反复使用来提高熟练度,所以好的Functional ECO工具应该是操作简单,设定简易,最好是即插即用。另一方面,因为使用到Functional ECO的场景往往是十万火急,因此对于工具的运行时间、迭代次数都要力求做到极致,最好是无需迭代、一次运行即可得到最佳结果,并且运行时间越快越好,可以说ECO就是在和时间赛跑。

值得庆幸的是,奇捷着眼于对Functional ECO的深刻理解,并基于团队数十年在EDA领域积累的丰富经验,厚积薄发,以解决Kager所提到的业内痛点为目标,着力开发专门针对解决Functional ECO问题的自动化EDA工具EasylogicECOTM。

Kager介绍说,与传统的ECO工具相比,EasylogicECOTM在使用流程、运行时间、生成的补丁质量上均体现出了相当高的水平。EasylogicECOTM针对Functional ECO问题的独有特点,采用了革新的流程与核心算法,使得其与传统工具比,自动化程度大大提高,用户基本可以做到一键就能得到最优结果,方便操作,无需迭代;同时,在运行速度和生成的补丁质量方面都有巨大改进。测试结果显示,EasylogicECOTM的运行时间可比传统工具快数倍,生成的补丁质量比传统工具的结果平均要好30%,有些case甚至能好到10倍以上。

快速迭代与专业服务相结合

利刃出鞘,EasylogicECOTM凭借出众的性能在市场上迎来了丰实的收获。据悉,EasylogicECOTM已有数十家签约客户,并且早已走出国门、走向世界。客户遍布世界各地,其中不乏韩国、美国等世界知名的芯片设计公司。而Kager所率领的团队在为国内外用户提供高质量技术服务支持的过程中,也形成了完备的服务体系,积累了宝贵的知识经验。

显然,这一成绩的取得与奇捷对客户的“精准”服务也息息相关。Kager提到,尽管EasylogicECOTM可直接加入到用户原有的 ASIC 设计流程,与原有工具链无缝衔接,但由于不同客户有不同的需求,且设计模式不一,因此对于工具流程的简化以及各种定制化的专业服务变得非常重要。可以说,这是奇捷服务“DNA”的胜利。

EasylogicECOTM支持任何ASIC设计阶段所提出的功能性ECO请求

Kager强调,在帮助客户快速完成ECO任务这方面,奇捷主要注重两点坚持:一是及时响应——客户一旦遭遇任何问题,都可立即联系并获得FAE或RD的帮助,点对点服务。二是最快速的定制化支持——客户一旦有特殊需求,奇捷RD团队会在尽可能短的时间内实现该功能,并及时给予客户新的版本来解决问题,从而使得客户能够在最短时间内完成ECO任务,尽最大努力保证产品研发进度。

Kager举例说,有一家客户的产品备用(spare cell)单元预留有限,但是RTL改动有点复杂,人工ECO难以完成。他们也尝试过市场上其他的ECO自动化工具,但这些工具都无法满足要求,且操作困难,耗时费力。奇捷在了解情况后立即为客户提供培训并为其搭建环境,不到一周时间客户就将这个人工无法完成的项目“通关”了。

Kager提及了另一家客户案例,则更能彰显奇捷增值服务的范本:奇捷在与该客户对接后,两天内即为其呈现了一个初步结果。之后又依据客户产品特性,在一个星期内就推出新版改进算法,使得ECO的补丁质量进一步提高,同时将运行时间减少为原来的1/3。

对于奇捷“专业且迅捷”的服务,诸多客户都给出了高度评价。

创新和推广适用于Functional ECO的设计规范

无疑,奇捷与客户合作是相辅相成的过程。

奇捷通过与多家客户的合作,获益匪浅,在此过程中,不断改进工具的性能,满足客户新的需求,但是另一方面,奇捷也发现有些客户的设计流程规范对于工具并不“友好”,针对这些客户的设计,工具的表现相对差强人意。

这一点也引起了奇捷研发团队对于Functional ECO问题的进一步深入思考:即Functional ECO与芯片设计流程规范之间如何能够更高效地匹配且执行?

“因ECO的过程和结果其实通常与客户本身的设计流程规范关系紧密,如综合策略、优化选项、命名规则或是客户本身版本管理等等,都会对最后结果产生不同程度的影响。”Kager表示,“其实很多芯片设计公司对于设计流程规范对Functional ECO的影响不是很清楚,而奇捷有幸接触过上百家客户,对于哪些流程更有利于Functional ECO也有了一些心得体会。奇捷很愿意分享自己在Functional ECO方面的经验,为客户设计流程规范提供中肯的建议,帮助客户能又快又好地完成ECO任务。”

奇捷的产品开启了Functional ECO市场的变革之后, 志存高远的奇捷也“肩负重任”,着力促进ECO流程的标准化。

“为提升ASIC产业ECO能力,使得各个芯片设计公司能更精准、更有效率地解决IC设计全流程中各个阶段出现的ECO问题,奇捷希望能联合上下游合作伙伴,一起推广一个最适合ECO的综合策略与实现流程,期待能为ASIC业界带来一定的规范,使得每个设计遇到逻辑功能变更的问题都可以通过ECO解决而无需花几个月的时间重头再来。就像软件操作系统那样,只需安装(安全更新)补丁,无需重装系统。”Kager道出了奇捷的宏大愿景。

未来的持续进阶

在细分Functional ECO领域达到了世界顶尖水平的奇捷,可谓走出了一条“正确”的险路,对于奇捷下一步的布局,Kager从趋势和前沿方面进行了阐述。

他提到,Functional ECO工具不是一个可有可无的点工具,而是可以帮助芯片公司顺利按计划流片、推出产品、取得市场成功的必不可少地刚需核心工具。随着产业发展,Functional ECO工具的重要性与日俱增。

而奇捷身为Functional ECO工具EasylogicECOTM的创造者,未来也将持续深耕,将围绕产品技术持续改进、服务第一以及助力客户芯片事业成功这三大主轴全力布局。

“在市场方面,将加深与现有头部企业客户的合作,根据客户的反馈,持续开发新的功能,不断迭代优化,在产品技术方面持续领先;在客户方面,继续秉持实时响应与最快速支援。奇捷并不以自身的事业成功为满足,而是将客户芯片事业成功作为客户服务的终极目标。”Kager强调。

ECO领域谱写新篇章

随着美国对中国半导体业的打压手段不断变本加厉,突破EDA卡脖子技术已成为国内EDA业共同的新航标。

近几年的政策支持、资本助力、人才加码,叠加众多EDA企业的奋发图强、由点及面,国内EDA在全流程、ECO、验证、先进封装等工具层面均取得了可圈可点的进步。

特别是在ECO领域,奇捷作为Functional ECO领域的新生力军,深耕于细分领域,以优异的实战性充分助力客户攻克数字芯片设计的“难关”,从而显著缩短了时间、提高了生产力,为客户革新创造了价值,为行业发展贡献了力量。

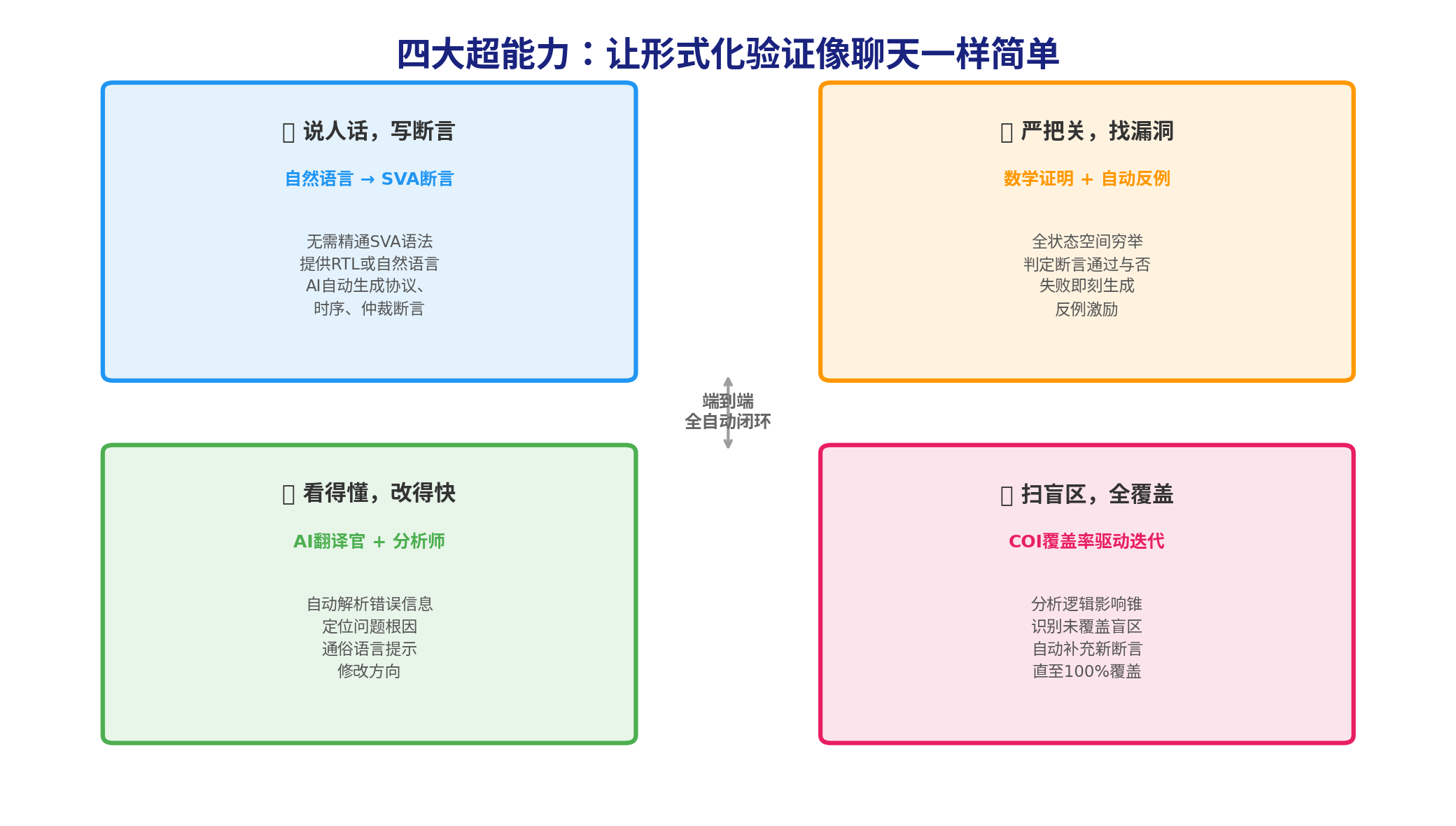

不止如此,奇捷为长远计,还在不断修练ECO“功力”,着力布局全球化,并在持续扩展验证等EDA工具,全力打造逻辑层面的全流程工具,以大胸怀和大担当,全面提升本土企业与EDA国外巨头抗衡的战斗力。

还要看到的是,国内EDA企业的发展绝不能单打独斗,不仅本土EDA企业要勠力同心,奋发图强,还需要更多的芯片设计企业对本土的EDA、IP和晶圆代工企业予以必要的支持,只有活跃健壮的上游生态建立起来,才能一起构建内生性的强大生态。

而类似奇捷这样本土EDA企业,有实力支撑,有进取作伴,有客户为后盾,未来的发展不仅值得期待,也将为国内EDA的奋进史谱写不一样的华彩篇章。