在芯片设计的上游供应链中,IP是技术含量最高的价值节点之一。由于产业起步较晚,我国在芯片设计上长期依赖国外IP。

近几年来,随着产业对底层技术的重视以及国产化需求的井喷式增长,尤其是在接口IP领域,国产化正向深水区推进,一些高端高性能产品不断问世。最近,国内接口IP供应商牛芯半导体在高速DDR IP产品上又实现突破,在国内外多种先进工艺节点,实现优异验证测试结果,为服务器、网络通信、AI等应用领域的高端SoC芯片自主研发提供了新的选择,助推国内SoC产品向高阶DDR接口升级。

速度提升 工艺升级,DDR IP挑战凸显

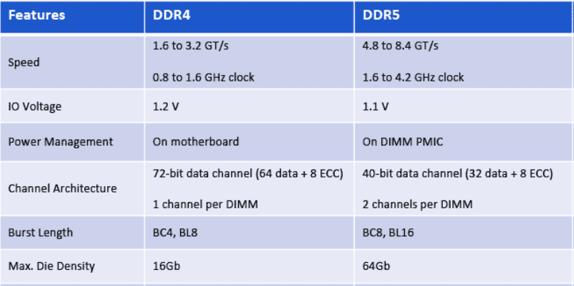

伴随着数据中心、5G、人工智能相关应用的发展,尤其是在时下生成式AI发展热潮下,数据中心等基础算力需求猛增,追求更快速率、更高带宽、更大容量、更低功耗的DDR内存技术已是不可逆的趋势。速率、带宽等技术规格不断提升,从DDR4到DDR5,数据速率从1.6-3.2GT/s大幅提升到4.8-8.4GT/s,对信号完整性、信号稳定传输、功耗等都带来更多挑战。与此同时,从40nm、28nm到14/12nm、7/5nm,制程工艺不断演进,研发打磨新一代工艺产品面临更高的难度。

作为SoC芯片重要的组成部分,在芯片设计中,DDR主要负责硬盘、主板、显卡等硬件与处理器之间的数据交换,如果作为数据交换桥梁的DDR出现问题,芯片的功能必然会大受影响,甚至无法正常工作,因此在设计上门槛极高。

如果芯片设计公司独立开发一款满足性能设计要求且可靠的DDR模块,不仅验证周期长、投入大,且面临总线速度与制程工艺提升带来的指数级增长的设计难度,芯片设计公司或将不得不承担延误产品面市的风险。因此,来自第三方IP厂家的成熟可靠的IP产品成为芯片厂商的不二选择,也是国内芯片公司能专注差异化设计、提升产品力、抢占市场先机的有力依靠。近几年来,国内市场对中高端DDR IP的需求保持了持续快速增长。

替代进入深水区,国产DDR IP实力破圈

伴随着国内集成电路设计产业的蓬勃发展,以及国产替代意识的高涨,国内涌现出了一批专注芯片国产化、聚焦自主可控的IP供应商,产品从原来的单一、低速接口IP,向高速、支持多协议的组合产品方案升级。牛芯半导体凭借长期专注技术创新,在SerDes、DDR等细分赛道中逐渐跑出,成为颇具代表性的企业。

纵观国内众多DDR IP供应商,牛芯半导体不仅在多工艺节点均有布局,是国内少数既有DDR PHY IP又能提供DDR Controller IP的成熟厂商。同时,还能为客户提供基于DDR IP相对灵活的定制模块或功能 。

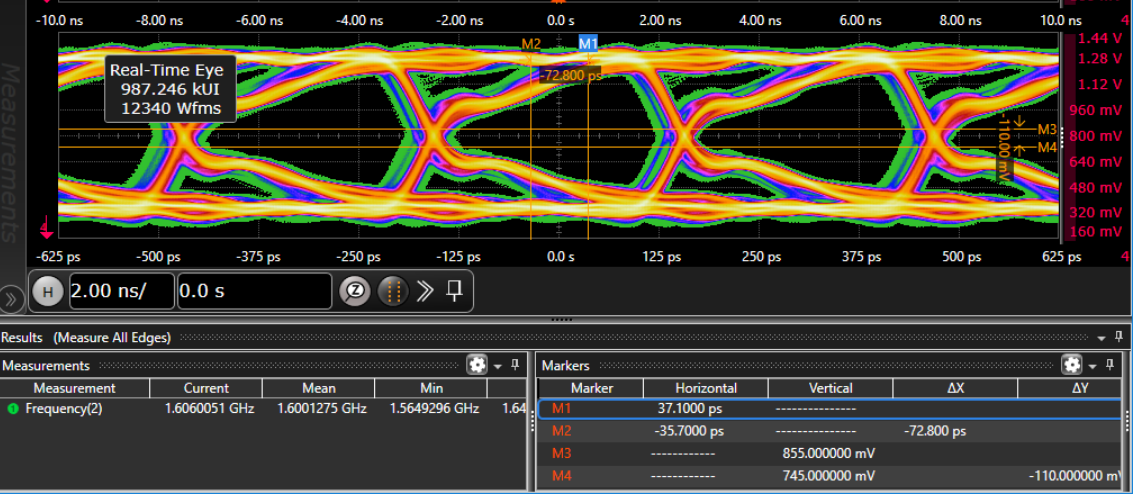

最近,牛芯半导体在DDR IP产品上实现新突破,DDR3/3L/4 & LPDDR2/3/4/4X DDR MC+DDR PHY combo IP在国内外主流先进工艺节点12/22/28nm均取得了成功验证测试结果:DDR4最高速率可以做到3200Mbps,LPDDR4/4X最高速率可以做到4266Mbps。

据悉,目前在先进工艺制程下能取得这一测试结果的国产IP产品并不多,牛芯的IP产品能做到与代工厂工艺紧密配合且取得优异验证测试数据,为芯片设计企业提供了成熟的高速DDR IP产品,无疑将加速这一领域的国产替代。

牛芯半导体的DDR IP产品能凭实力成功破圈,与其多年的经验积累与技术创新分不开。

一个典型的SoC内部DDR子系统中,主要包含DDR MC(controller)和DDR PHY两个模块,对应的也包含两类IP:DDR MC IP和DDR PHY IP。DDR PHY是DDR MC和内存颗粒之间读写交互的桥梁,DDR MC则负责管理和控制内存的读写操作,这两类IP在设计上各有侧重,挑战也不同。DDR IP(DDR MC + DDR PHY)作为底层的高速数模混合类IP,一直以来都存在着较高的开发门槛,国外IP厂商把持技术壁垒,占据着最主要的市场份额。

面对外部“卡脖子”的挑战与国产替代的发展机遇,牛芯半导体密切关注并积极布局数据中心、5G网络、AI人工智能等新兴领域,持续投入以提升DDR底层技术,以便更好适配芯片设计前沿需求。在DDR PHY方向上,牛芯半导体围绕SI/PI、训练算法、实时电压温度补偿以及高速DDR I/O设计,持续进行针对性的创新。

考虑到DDR PHY的使用很大程度上是一个系统工程,在芯片设计初期,牛芯半导体将和客户一起规划DDR PHY的布局和PAD位置,提供I/O IBIS/Hspice model协助客户进行电源完整性(PI)和信号完整性(SI)的仿真和分析,为客户提供一站式的检查和确认。贯穿封装、基板设计以及PCB设计,牛芯半导体可以完善保障集成过程中PHY IP本身性能的实现。

其次,为了适配不同DDR拓扑或外部环境(温度电压)所引入的变化,牛芯半导体DDR PHY通过配合CA Training、Write/Read Leveling、Write/Read Deskew以及Write/Read Eye Centering等一系列可靠稳定的训练算法来调整时钟相位的关系,而对于DDR4、LPDDR4或速度更高的协议,则还会搭配2D VREF Training来寻找到数字眼图裕量最大的设定。同时,针对温度和电压的变化,可以自适应进行Delay line的实时补偿,有力保证了系统的稳定性。

另外,高速DDR I/O的设计也是一大挑战。得益于在SerDes高速接口方面的长期积累,从现有的成熟产品到积极布局的DDR5/LPDDR5 IP,牛芯半导体也正逐步借鉴SerDes接口中所使用的Tx FFE(前向反馈均衡)和Rx DFE(判决反馈均衡)的模块,将其逐步应用到DDR PHY IP中,以应对越来越高速的单pin(>6400Mbps)信号所带来的更严重的信号衰减和码间ISI的影响。

至于DDR MC IP,牛芯半导体认为两者在设计上的挑战又有所不同。作为DDR PHY密切的合作伙伴,DDR MC本身设计的合理和灵活程度,以及两者之间配合的紧密度,直接决定整个DDR系统在时延和带宽之间是否会取得优异和平衡的表现。另外,配合DDR PHY提升在低功耗、节能场景(动态变频)下的表现,也是DDR MC设计的一大重点。

牛芯半导体通过基于数字架构的独特设计,使得DDR PHY易于在不同工艺间移植,配合自研的DDR MC,在带宽和时延的性能平衡以及面积和低功耗的表现上达到业界一流水平。另外,牛芯半导体DDR IP也更注重国产DRAM颗粒的支持,目前DDR/LPDDR IP已成功对接多款国产颗粒,经过特别调试优化的鲁棒性更强,为客户在颗粒供应上提供更多的选择。

背靠市场与客户,本土化优势显著

在接口IP领域,多年来尽管国外厂商占据了主导地位,但国内厂商凭借在市场与用户方面近水楼台的有利地位,在快速响应、定制化服务、对国产上下游厂商支持配合等本土化方面积累下了国外厂商难以比拟的优势。

一方面,当下极少国外IP供应商提供对产品规格的个性化定制设计,本土IP供应商提供定制化服务无疑将成为国产替代的突破口。牛芯半导体作为其中代表,已为多家客户提供涵盖PHY IP和Controller IP的定制服务,以及链路仿真、信号完整性分析、测试调试服务等技术支持。

牛芯半导体兼具DDR PHY IP方案和DDR Controller IP方案,这将更便于聚焦客户需求进行针对性优化,也为同款IP产品在不同工艺节点之间快速迁移提供了便利。另外,基于多数应用场景中DDR IP需要结合SerDes IP使用的实际情况,牛芯半导体提供SerDes+ DDR IP解决方案,能满足客户对外设端口的集成需求,实现全部高速接口IP的一站式采购。

另一方面,市场对中高端DDR IP的需求持续增长,尤其是在国产先进工艺制程的需求更加凸显,坚持技术创新并能够快速推出适配市场前沿需求的IP产品,对本土IP厂商来说尤为重要。

作为本土较早进入国内FinFET工艺的国产接口IP厂商,牛芯半导体长期专注自主研发,在工业芯片设计及量产方面具有丰富经验和技术积累,在主要国产工艺节点上形成了较广泛的产品布局。目前,经测试,牛芯半导体自主研发的DDR IP PPA指标行业领先,DDR3/4和LPDDR3/4等成熟IP产品在高性能计算、AI、智慧终端、企业存储、网络通信等领域有着广泛应用,同时公司也正积极布局,加速推进DDR5和LPDDR5 IP的量产验证。

此次牛芯DDR IP产品在国内外先进FinFET工艺节点上取得突破,为国产SoC厂商带来了新的选择。

欢迎关注,微信公众号“牛芯半导体”,牛芯半导体官网:www.kniulink.com。

评论

文明上网理性发言,请遵守新闻评论服务协议

登录参与评论

0/1000