近日,集成电路学院程然研究团队在国际顶级期刊《IEEE电子器件杂志》(IEEE Electron Device letters,简称EDL)上发表题为“Experimental Demonstration of Non-Volatile Boolean Logic With Field Configurable 1FeFET-1RRAM Technology”的论文,并入选该期主封面文章。该论文第一作者为硕士生丁哲韬、博士生李雪阳,通讯作者为程然副教授。

课题背景

现如今,云计算、人工智能(AI)等新兴计算机技术的飞速发展,带来了急剧增加的数据总量以及吞吐量。在经典冯诺依曼架构中,系统的计算单元与存储单元相互分立,工作过程中必须进行信息交换。面对 “存储墙”,数据交换传输的速度是影响算力及功耗的最主要因素。针对冯诺依曼架构运行过程中的“存储墙”问题,存算一体技术应运而生。存算一体的技术路线主要包括查存计算、近存计算、存内计算以及存内逻辑等,目前应用较为成熟的存储器件有DRAM、SRAM与Flash等。目前学术界关注的焦点很大一部分集中在基于各种非易失性器件(如RRAM、FeFET等)实现存算一体。

课题亮点

此前的存算一体的逻辑单元研究,主要是基于1FeFET-1MOSFET结构的NOR/NAND逻辑门模型和仿真。基于该设计的不同逻辑操作,需要通过调整上拉/下拉电阻或使用更多的MOSFET器件来实现。前者使电路设计复杂化,而后者则需要使用更多的电路面积。

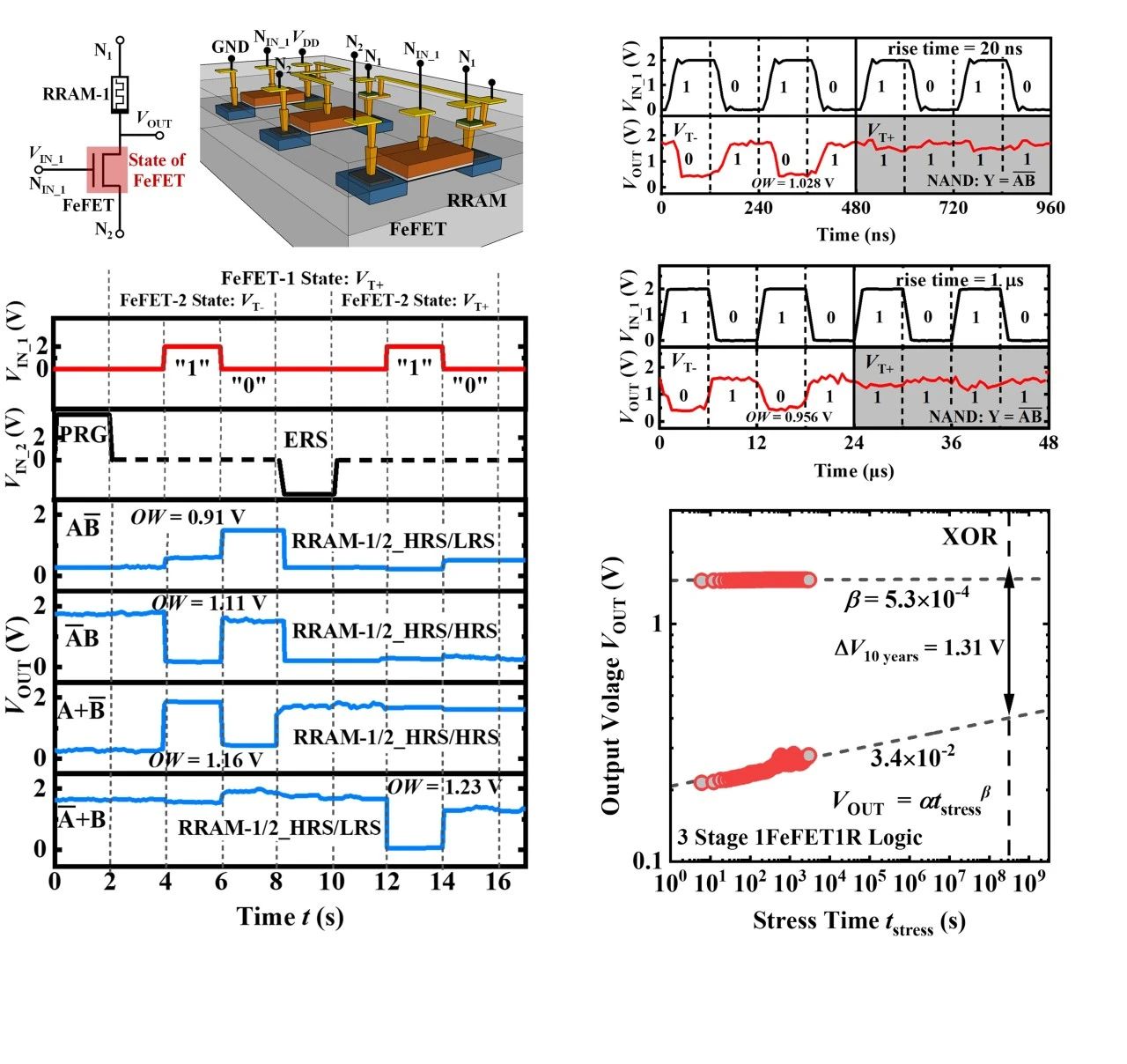

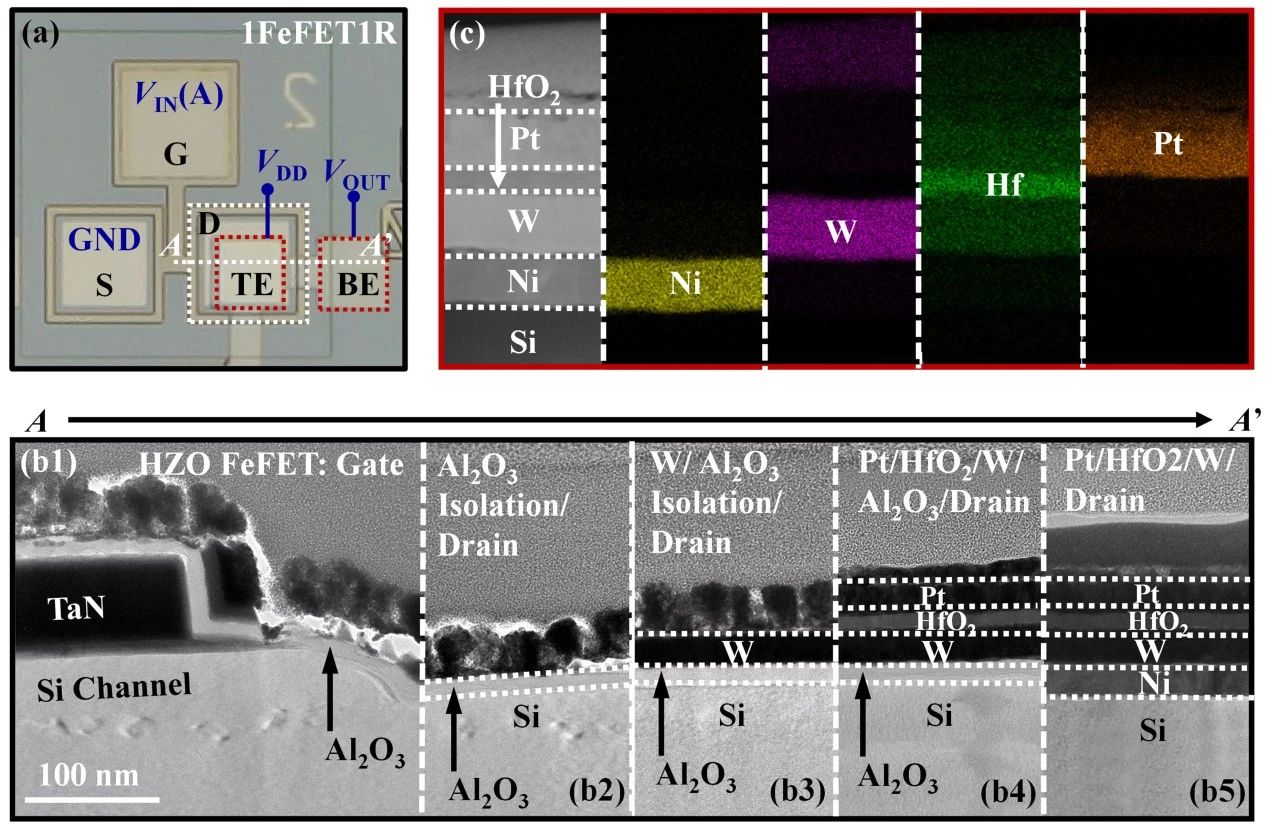

本研究创新型地提出了一种 1FeFET-1RRAM (1FeFET1R) 的可重构逻辑单元设计方法,并完成了制备、集成与实验演示。利用 FeFET 的非易失性存储功能进行逻辑运算,同时,利用 RRAM 的可切换电阻进行逻辑重构,从而实现存内逻辑。团队通过成套工艺,制备了8吋晶圆级 1FeFET1R 逻辑单元以及级联逻辑门电路,并通过电学测试演示了完整的16 种布尔逻辑功能。此外,还对 1FeFET1R 电路的速度和稳定性进行了测试验证。基于 1FeFET1R 的非易失性逻辑电路具有更小的面积消耗、更高的计算效率、更简单且和 CMOS 兼容的工艺以及逻辑可重构的优势,在存内逻辑领域有着广阔的研究前景。

三大亮点

设计创新

基于1FeFET-1RRAM结构实现了全16种布尔逻辑功能

工艺创新

8寸晶圆级1FeFET-1RRAM逻辑电路集成和演示

性能和可靠性

纳秒级速度响应和超过10年的电路输出稳定性

提出的1FeFET1R逻辑单元原理示意图与电学测试数据结果图

课题成果

基于1FeFET-1RRAM 设计,课题组完成了可重构逻辑单元和级联电路的工艺开发,演示验证了基于1FeFET-1RRAM设计的非易失性存内逻辑技术。本课题创新性地将 FeFET 和 RRAM 集成,前者用于非易失性逻辑运算,后者用于逻辑功能重构。基于8寸成套工艺流片,演示并验证了全16种布尔逻辑功能。 1FeFET-1RRAM 非易失逻辑技术具有优秀的可重构性、高面积效率、低功耗、出色的速度和可靠性表现,在存内逻辑运算领域具有巨大应用潜力。

制备的1FeFET1R逻辑单元的SEM、TEM照片与元素分析结果

评论

文明上网理性发言,请遵守新闻评论服务协议

登录参与评论

0/1000