时光荏苒,一直指引半导体业前行的摩尔定律马上就迎来甲子年了。

自1965年英特尔公司的创始人之一戈登·摩尔提出了摩尔定律以来,业界似乎拥有了预见未来的“魔法棒”。像一位历史预言家一样,摩尔定律似乎一直在不断验证其存在的价值。不仅为半导体业提供了一个稳定的指导原则,不断促进技术的快速发展和成本的降低,进而推动了计算机和信息技术的不断进步,一路经历了PC、互联网和智能手机时代,并迎来了AI时代的“寒武纪大爆发”。

历经近60年的起伏,近些年业界质疑摩尔定律有点像薛定谔的猫,摩尔定律快要失效了、摩尔定律已经逼近极限……诸如此类的声音不绝于耳。但这些插曲总是很快就被“打脸”:每当摩尔定律势头有所减缓之际,总会出现新一波“核爆点”,迎来新的创新突破,无论是工艺创新、封装创新还是架构创新,促进晶体管微缩和效能持续进阶,亦让摩尔定律步履不停。

正如英特尔CEO帕特·基辛格在最近举行的Computex大会上亮出的观点:“摩尔定律依然活力满满(Moore’s Law is alive and well),这仍将是推动半导体行业在2030年达到一万亿美元规模的动力。”

摩尔定律生命力永无止境

细究起来,摩尔定律其实是戈登·摩尔在一整篇论文所浓缩而成的一句话,在刚刚发布时是:“芯片可容纳的晶体管数量,每隔12个月便会增加一倍,微处理器的性能提高一倍,或价格下降一半”。在后续的时间里摩尔定律经过了修改,将时间从12个月改为18—24个月,也成为目前通行的“指南”。

可以说,摩尔定律不仅是技术创新的“黄金法则”,推动半导体行业发展,同时还在技术和经济之间建立了量化联系,对产业发展起到指引方向的作用。

作为算力的载体,半导体是信息技术发展的基石。随着数据量的指数级增长,我们始终需要性能更强、功耗更低的芯片,同时摩尔定律还关乎算力成本的降低。对半导体行业而言,摩尔定律更像一面指导产业不断开拓创新的旗帜,代表着推动算力不断以指数级方式提升的信念,为制造速度更快、体积更小、价格更实惠的晶体管铺平了道路。同时,这也带来了计算机、互联网、智能设备、数据中心、智能汽车的快速发展和迭代,驱动了各种数字化应用的蓬勃发展,为日益数字化、智能化的世界奠定了基础。

尤其是新一代科技变革浪潮生成式AI崛起,算力需求迎来大爆发。

帕特·基辛格曾在英特尔on技术创新大会上表示,世界对计算的需求已呈指数级增长,而且这种需求与芯片的面积、成本和功耗成反比。简而言之,这就是摩尔定律。更充足、更强大、更具性价比的处理能力,是经济增长的关键组成。AI代表着计算的新时代,正在催生全球增长的新时代,促进了“芯经济”的崛起,即芯片形成了规模达5740亿美元的产业,并驱动着全球约8万亿美元的技术经济。

追溯到数年前,1971年生产的芯片可以在一平方毫米中塞入200个晶体管,而如今最先进的芯片可以在同样的面积上集成数十亿个晶体管,而且每个晶体管的运行速度也比当初快几万倍。

英特尔还预计,到2030年单个封装中集成的晶体管数量将达到一万亿。显然,这一增长节奏仍然符合摩尔定律。

历经60年, 摩尔定律依旧熠熠生辉,它不仅是技术进步的象征, 更是持续创新精神的体现。 当我们看到诸如High-NA EUV、RibbonFET、PowerVia、Foveros Omni和Foveros Direct等前沿技术的诞生与应用时,我们看到了创新的无限可能。这些技术的涌现,让我们相信,摩尔定律的生命力,永无止境。

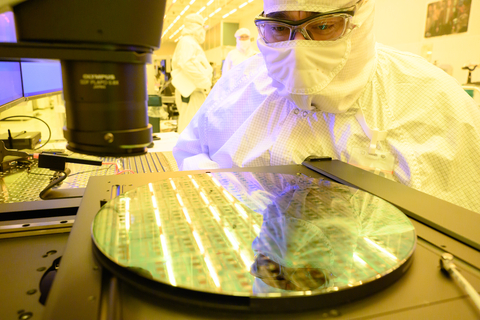

工艺进阶持续创新护航

可以看到,摩尔定律的法则在很大程度上与芯片通过工艺节点制造的方式有关。每一个新工艺都应该比上一代更密集、更优化,这就是该行业几十年来能够满足摩尔定律预测的原因。而在历史的长河中,晶圆厂一直按照每一两年推出新工艺节点的节奏升级,并提高了频率和能效,成为摩尔定律前行的重要推手。

自成立以来,英特尔便不断通过技术创新,将越来越多的晶体管整合到更小的芯片上,并不断克服晶体管微缩出现的漏电、量子隧穿等挑战。从平面CMOS、到Hi-K金属栅极(Hi-K metal gate),再到开启FinFET时代的22nm,直至目前的3nm、2nm,英特尔贡献了里程碑式的创新,并不断以多维度创新拓展工艺技术的边界。

目前英特尔“四年五个制程节点”的目标已基本落定,相当于2nm的第一代GAA RibbonFET工艺即Intel 20A有望在今年推出;后续产品是Intel 18A,预计将于2025年上半年投入生产,并逐步推进至Intel 14A节点。

面向新工艺的重重挑战,在工艺基础创新方面有着深厚底蕴的英特尔也祭出全新的创新招数应对,上述节点的两大利器分别是RibbonFET全环绕栅极晶体管和PowerVia背面供电。

RibbonFET全环绕栅极(GAA)晶体管代表了英特尔自FinFET以来的首个全新晶体管架构。在RibbonFET晶体管中,栅极能够更好地控制电流的流通,同时在任意电压下提供更强的驱动电流,让晶体管开关的速度更快,从而提升晶体管的性能。RibbonFET还将进一步提升芯片设计的灵活性,其沟道可以根据需求加宽或缩窄,从而更适配不同的应用场景。

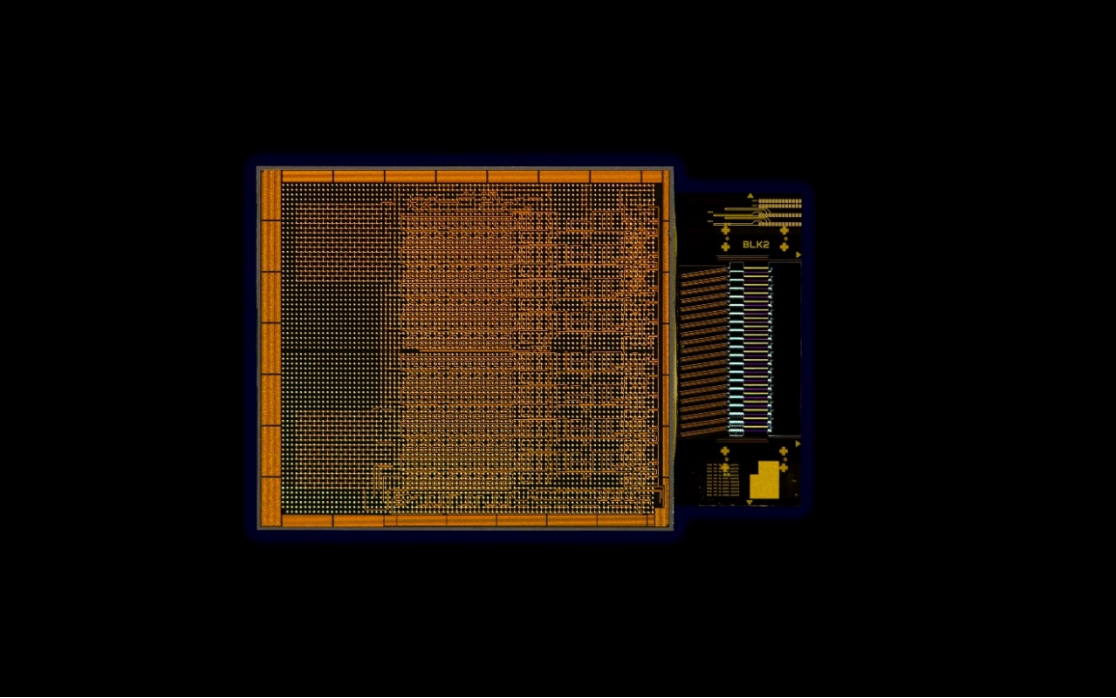

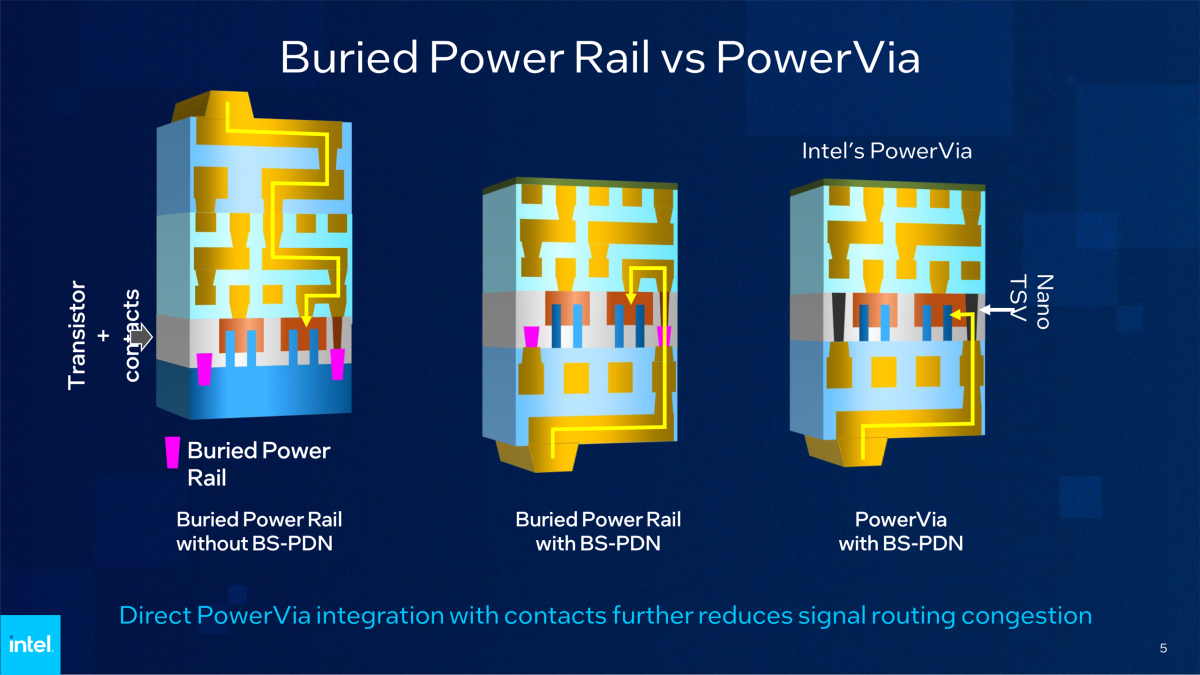

同时,英特尔还提供业界首个背面供电技术PowerVia。从数十年前到现在,晶体管架构中的电源线和信号线一直都在“抢占”晶圆内的同一块空间。通过PowerVia技术在结构上将这两者的布线分开,可更有效地使用金属层,并使芯片设计公司在不牺牲资源的同时提高晶体管密度,进而显著地提高功率和性能。

为解决背面供电技术带来了散热和调试设计方面的全新挑战,英特尔一方面通过将PowerVia与RibbonFET这两项技术的研发分开进行应对,另一方面开发了散热技术,以避免过热问题的出现。

值得关注的是,在下一代Intel 14A节点英特尔将采用High NA EUV(高数值孔径极紫外光刻)技术。High NA EUV技术是EUV技术的进一步发展,通过升级将掩膜上的电路图形反射到硅晶圆上的光学系统,High NA EUV可大幅提高分辨率,从而有助于晶体管的进一步微缩。英特尔希望此举助力在Intel 18A之后继续保持工艺领先地位。

尽管RibbonFET已实现了在3nm甚至2nm工艺中的应用,但进一步缩小到1nm以下,CFET架构将成新“接盘侠”。英特尔业已高度重视,围绕 CFET制造的Inverter做了多项改进。此外,英特尔还通过将每个器件的纳米片数量从2个增加到3个,将两个器件之间的间距从50nm减小到30nm。

上述例子均只是工艺制程持续过“坎”必须借助的新利器,也需要整合供应链进行一系列的协作和改进,但推进摩尔定律挥师向前的障碍也在这一项项的创新中得以消弭。

先进封装提供强大助力

使集成电路继续按照摩尔定律所述那样“倍增”,除了工艺进阶之外,随着尺寸微缩不断向前,封装的作用及其对摩尔定律微缩的贡献正在演进,成为实现摩尔定律效益的载体。

从引线键合和引线框架封装,到陶瓷基板上的倒片封装,再到对有机基板的采用和多芯片封装的引入,以及2.5D/3D封装和Chiplet的到来,半导体封装在经历了几次重大革新之后,迎来了先进封装的时代。先进封装与制程工艺相辅相成,在提高芯片集成度、加强互联、性能优化的过程中扮演了重要角色,成为性能持续提升的重要保障,并持续为实现摩尔定律所需的微缩提供动能。

据Yole预测,2022—2028年先进封装市场将以10.6%的年化复合增长率增至786亿美元,且2028年先进封装占封装行业的比重预计将达到57.8%,先进封装将成为全球封装市场的主要增长极。

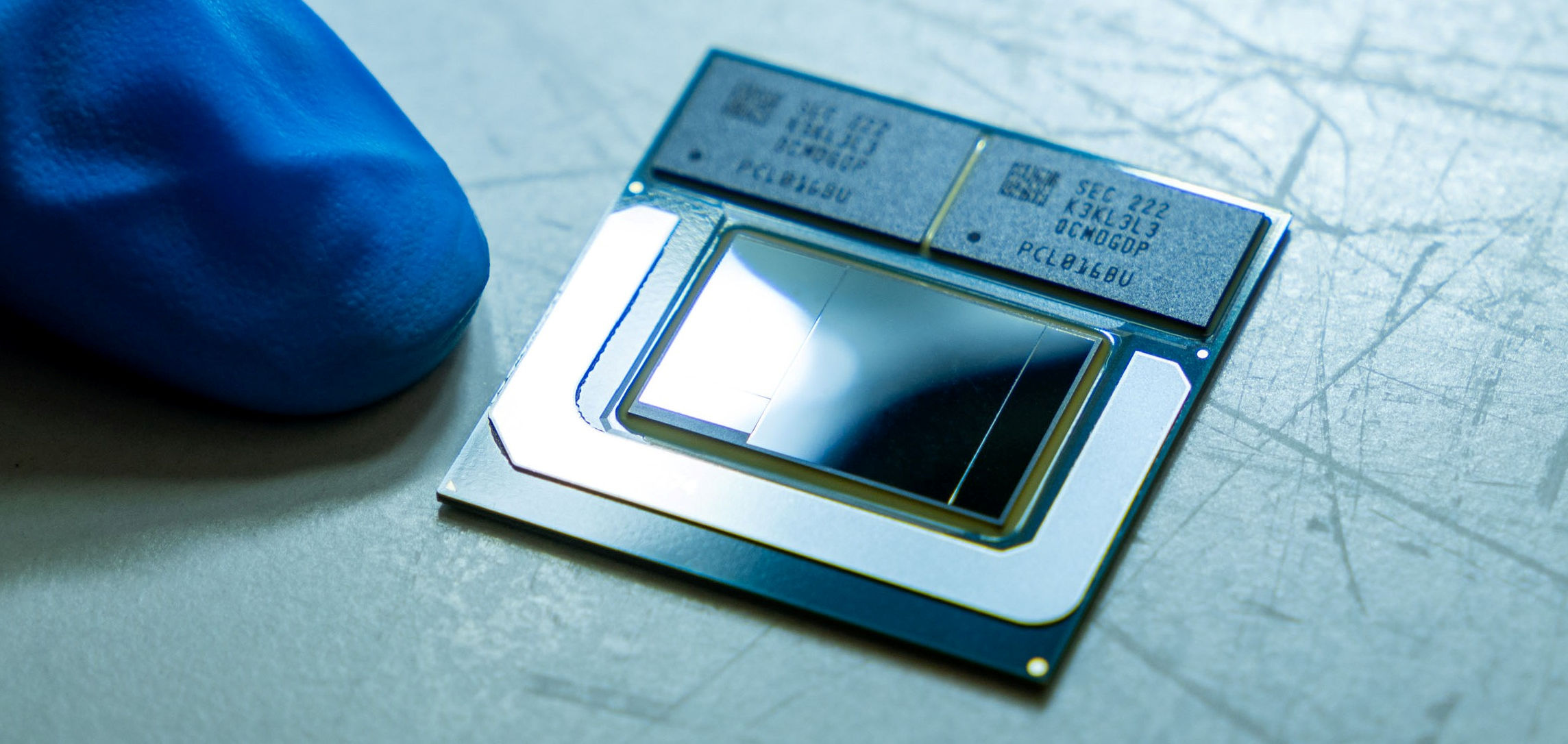

英特尔通过多年技术探索,相继推出了EMIB、Foveros等多种先进封装技术,在互连密度、功率效率和可扩展性三个方面持续精进。其EMIB(嵌入式多芯片互连桥接)作为2.5D先进封装技术,支持把不同的芯片放在同一块平面上相互连接。传统的2.5D封装是在芯片和基板间的硅中介层上进行布线,英特尔EMIB则是通过一个嵌入基板内部的单独的芯片完成互连,从而将芯片互连的凸点间距降低到45微米。

在代表未来的3D封装层面,英特尔Foveros 3D先进封装技术支持在垂直层面堆叠独立的芯片模块,并通过硅通孔技术实现垂直层面的互连。Foveros演进Foveros Omni和Foveros Direct——提供了新的扩展、新的互连技术和新的混合搭配功能。Foveros Omni 进一步将互连间距扩大到25微米,并增加了多个基础芯片的选项。Foveros Direct 引入了铜与铜的混合键合取代会影响数据传输速度的焊接,把凸点间距继续降低到10微米以下,并将大幅提高芯片互连密度和带宽及降低电阻。Foveros Direct还实现了功能单元分区,让模块化设计做到配置灵活、可定制。

在先进封装占据重要一席的材料,英特尔意识到未来使用有机材料微缩晶体管的能力可能将达到极限,因为有机材料耗电量更大,而且存在收缩和翘曲等限制。因此,采用玻璃基板成为迈向下一代半导体可行且必要的一步。

未雨绸缪的英特尔已在代表基板材料未来、5年内渗透率将超50%的玻璃基板领域布局十年之久。与目前采用的有机基板相比,玻璃基板具有独特的性能,如超低平面度、更好的热稳定性和机械稳定性,从而能够大幅提高基板上的互连密度。这些优势将使芯片架构师能够为AI等数据密集型工作负载打造高密度、高性能的芯片封装。同时,英特尔也在布局硅光模块中的CPO(共封装光学)技术,通过玻璃材质基板设计,利用光学传输的方式增加信号交换时的可用频宽,以优化算力成本。

结合先进制程与先进封装两条线,英特尔不仅希冀在晶圆代工领域实现“1+1>2”的效果,更有望借助多重创新,使半导体行业在2030年之后继续推进摩尔定律。

组件研究扩展边界

尽管在工艺和封装层面已经跨过一个个“山海”,但在未来继续推进摩尔定律,实现2030年在单个设备中集成一万亿个晶体管的目标,还需要在集成、材料等多重层面的创新助力。

英特尔也在孜孜以求,近年来组件研究部门围绕集成更多晶体管的扩展技术领域取得了全新的进展和突破。

在IEDM 2022上,英特尔聚焦于性能提升,以及为实现300毫米硅基氮化镓(GaN-on-silicon)晶圆开辟一条可行的路径。在IEDM 2023,英特尔在硅和氮化镓的工艺集成方面取得了进展,率先在同一块300毫米晶圆上成功集成硅晶体管和氮化镓晶体管,成功实现了高性能、大规模的集成电路供电解决方案“DrGaN”,这将有望让供电解决方案满足未来计算对功率密度和能效的需求。

为制造更薄的晶体管,英特尔还着力推进只有几个原子厚2D新型材料的研发工作,以使其在未来继续按照摩尔定律的节奏微缩下去:过渡金属二硫属化物(TMD)2D通道材料让晶体管物理栅极长度有机会微缩到10纳米以下。在IEDM 2023上,英特尔展示了高迁移率的过渡金属二硫属化物晶体管原型,用于NMOS和PMOS这两大CMOS关键组件。此外,英特尔还将展示其率先实现的两项技术:GAA 2D过渡金属二硫属化物PMOS晶体管和在300毫米晶圆上制造的2D PMOS晶体管。

通过开发可垂直放置在晶体管上方的存储器,英特尔重新定义了微缩技术,从而更有效地利用芯片面积。英特尔在业内率先展示了性能可媲美传统铁电沟槽电容器的堆叠型铁电电容器,可用于在逻辑芯片上构建铁电存储器(FeRAM)。业界首创的器件级模型,可定位铁电氧化器件的混合相位和缺陷,标志着英特尔在支持行业工具以开发新型存储器和铁电晶体管方面取得了重大进展。

此外,英特尔也在探索超越CMOS的新型器件和神经拟态计算、量子计算等有望大幅提高性能、降低功耗的全新计算范式。

从降本增效的角度来看摩尔定律,其远远还未达到发展尽头,随着多核、异构、存算一体、Chiplet等技术的发展,芯片集成度还会不断再创新高。看起来,推动摩尔定律的未来创新仅限于我们的想象力。

除了开创摩尔定律之外,摩尔还有一句名言:凡所为,臻于至善(Whatever has been done can be outdone)。面向未来,英特尔也将通过制程、封装和组件研究等前沿领域的一系列创新,继续在未来十年或更长时间内保持摩尔定律。或许,臻于至善让摩尔定律永不会停止。

登录

登录