1.兆易创新“时钟生成模块”专利公布

2.芯联集成“外延设备”专利获授权

3.芯驰半导体“针对芯片开发的信息处理方法、系统及电子设备”专利获授权

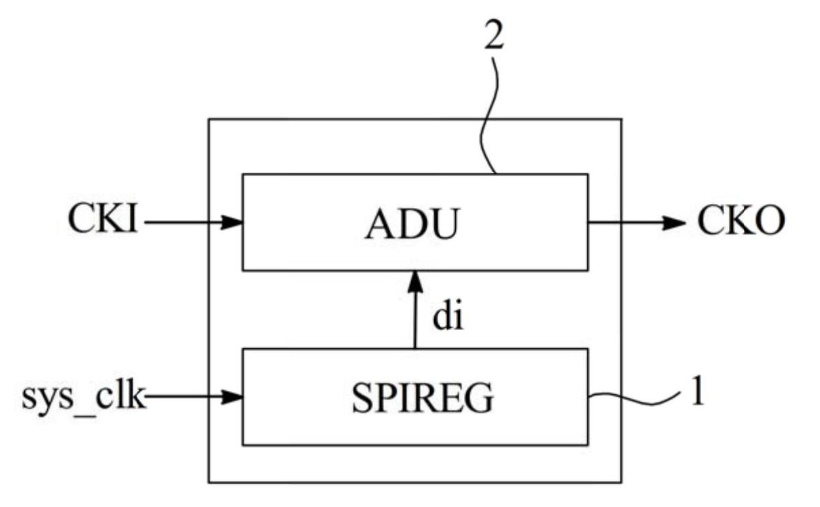

1.兆易创新“时钟生成模块”专利公布

天眼查显示,兆易创新科技集团股份有限公司“时钟生成模块”专利公布,申请公布日为2024年9月6日,申请公布号为CN118606246A。

本发明提供一种时钟生成模块,包括:延迟寄存器模块,所述延迟寄存器模块暂存基于系统时钟信号配置的延迟信息;及可调延迟器,所述可调延迟器耦接所述延迟寄存器模块,所述可调延迟器配置为依据所述延迟信息将用于串行外围接口的时钟信号延迟以生成延迟时钟信号。从而,有效解决现有技术的串行外围接口模块的时钟信号与数据之间存在相位差的问题。

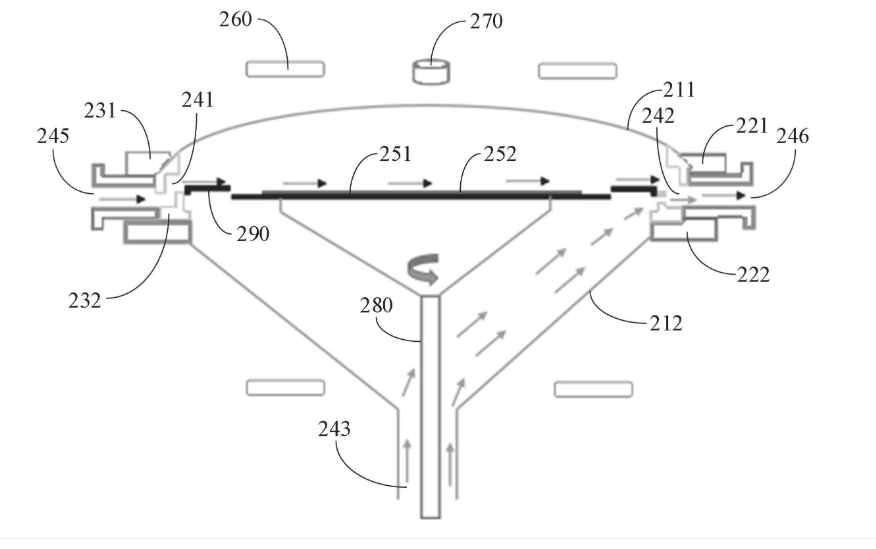

2.芯联集成“外延设备”专利获授权

天眼查显示,芯联集成电路制造股份有限公司近日取得一项名为“外延设备”的专利,授权公告号为CN221663071U,授权公告日为2024年9月6日,申请日为2024年1月25日。

本实用新型提供一种外延设备,外延设备包括:腔体,包括第一腔体和第二腔体;基座,设置于腔体内,用于承载衬底;第一腔体和基座之间形成有反应空间,第二腔体和基座之间形成有吹扫空间;第一内衬环和第二内衬环,设置于腔体内且分别位于第一腔体的边缘和第二腔体的边缘;第一内衬环和第二内衬环之间形成有用于反应气体进入反应空间的第一进气口和用于反应气体流出反应空间的第一出气口;其中,第二腔体上设置有用于吹扫气体进入吹扫空间的第二进气口,第二内衬环靠近第一出气口的部位中设置有用于吹扫气体流出吹扫空间的第二出气口。本申请可以提高外延层边缘厚度的均匀性,解决外延层边缘偏薄的问题,并提高腔体的PM周期。

3.芯驰半导体“针对芯片开发的信息处理方法、系统及电子设备”专利获授权

天眼查显示,北京芯驰半导体科技股份有限公司近日取得一项名为“针对芯片开发的信息处理方法、系统及电子设备”的专利,授权公告号为CN118395517B,授权公告日为2024年9月6日,申请日为2024年6月25日。

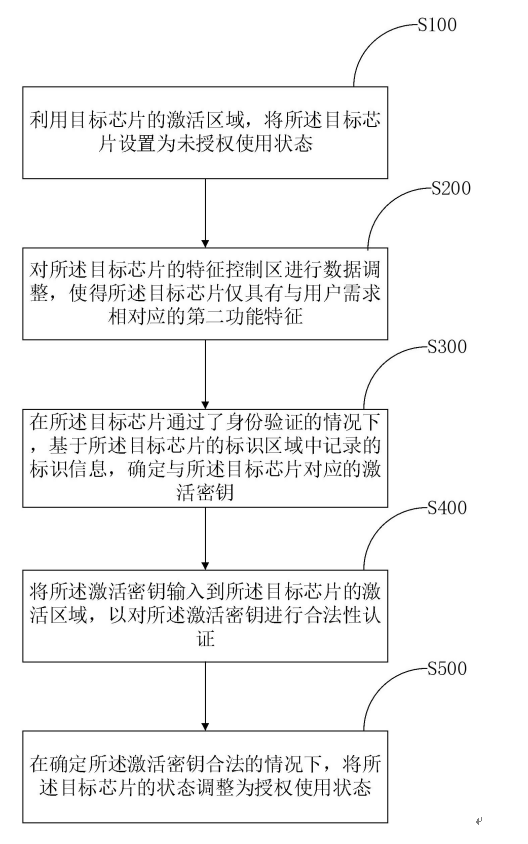

本申请公开了一种针对芯片开发的信息处理方法、系统及电子设备,该方法包括:利用目标芯片的激活区域,将目标芯片设置为未授权使用状态,其中处于未授权使用状态的目标芯片具有第一功能特征;对目标芯片的特征控制区进行数据调整,使得目标芯片仅具有与用户需求相对应的第二功能特征;在目标芯片通过了身份验证的情况下,基于目标芯片的标识区域中记录的标识信息,确定与目标芯片对应的激活密钥,其中标识信息与第二功能特征相关联;将激活密钥输入到目标芯片的激活区域,以对激活密钥进行合法性认证;在确定激活密钥合法的情况下,将目标芯片的状态调整为授权使用状态。该方法提高了芯片开发生产效率,降低了生产成本。