“效率”在射频功率放大器(PA)设计中占据举足轻重的地位。

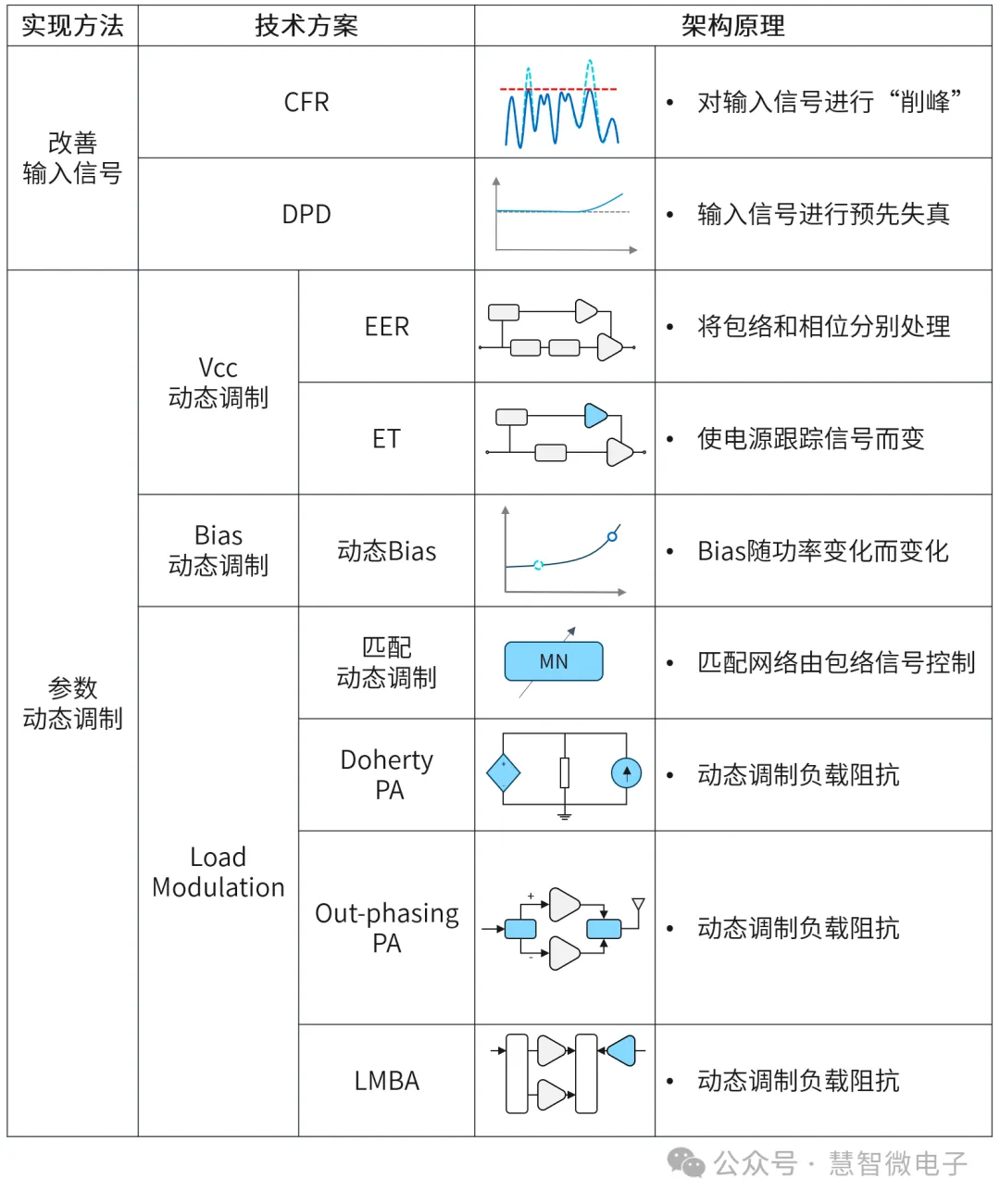

在之前的两篇文章中(《高效率PA设计:从Class A到Class J》与《5G射频PA的架构》),我们已经深入探讨了高效率PA设计的两大核心:PA的“Class”设计以及功率合成架构。然而,当单体PA的效率提升至一定极限后,PA厂商、平台厂商以及终端系统厂商开始将研究焦点转向包含PA在内的系统级设计。试图通过更高层次的系统解决方案,进一步突破PA的性能瓶颈。在这一领域,既有大家耳熟能详的包络跟踪(ET)和数字预失真(DPD)技术,也有相对陌生的负载调制(Load Modulation)和波峰因子减少(CFR)等技术。

这些技术究竟是如何神奇地提升PA效率的?未来又有哪些新技术可能应用于PA效率的提升?本文将试着从系统级的角度,理解高效率PA系统设计的奥秘。

效率与线性度PA设计的双重挑战

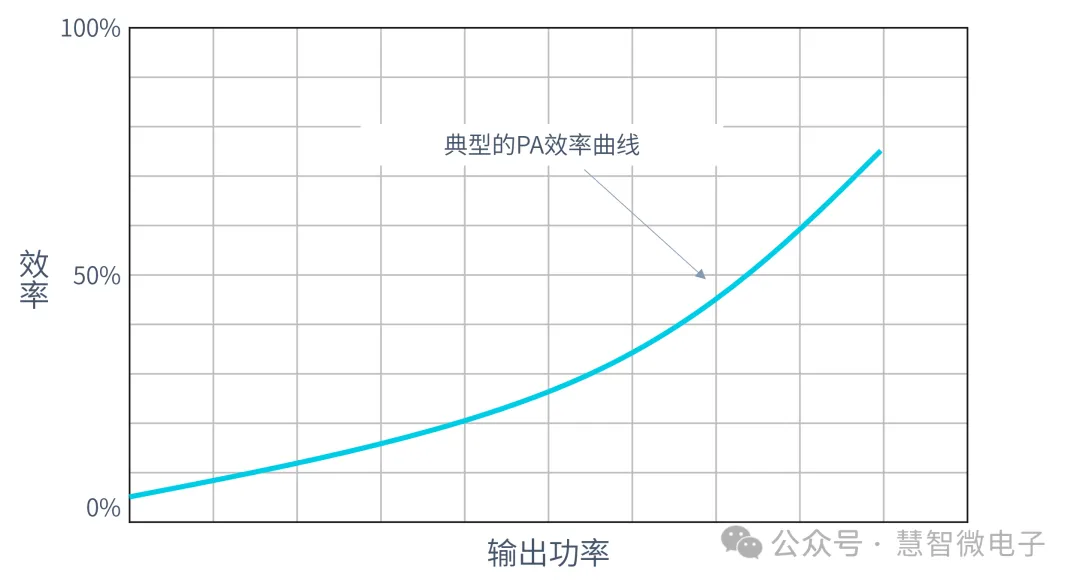

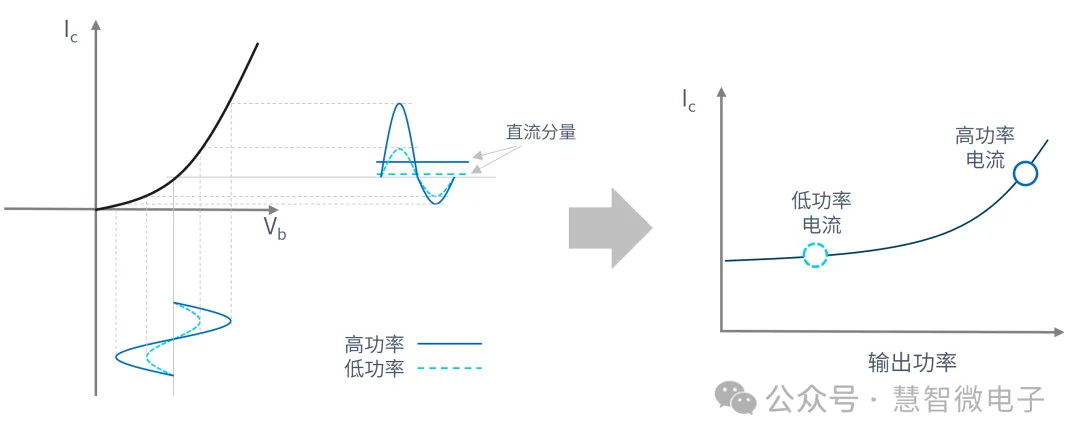

在PA的单体设计中,效率和设计所选的“Class”、拓扑架构乃至匹配网络的损耗等诸多因素紧密相连。然而,从系统层面来看,各种PA的效率曲线都可大致描绘为一根随功率提升而上升的曲线。简而言之,随着功率的增加,射频摆幅扩大,越来越多的能量被转化为射频信号,因此在高功率状态下,PA将直流电转换为射频信号的效率达到最高。

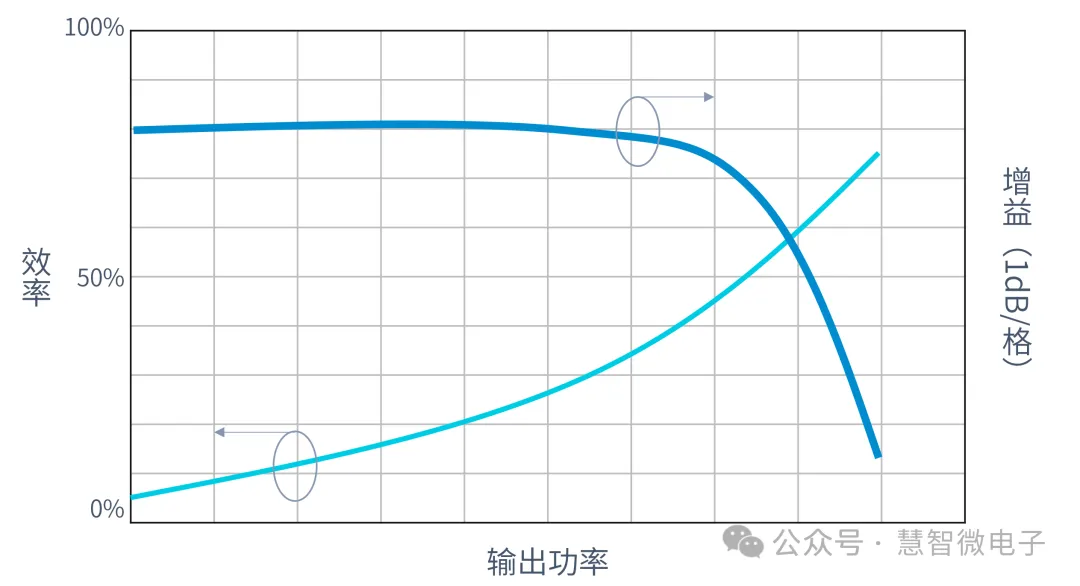

图:典型的PA效率曲线

尽管不同PA的峰值效率点和功率回退时的斜率存在差异,但效率随功率变化的大致趋势是固定的。基于这一效率曲线,我们可以得出一个PA高效率应用的基本原则:尽量让PA工作在接近高功率的状态。

然而,这种高效率状态并非没有代价。当PA越接近高功率饱和区,其线性度就会逐渐恶化。典型的增益随输出功率变化曲线显示,在饱和区,PA增益可能会出现几dB甚至十几dB的压缩,对于线性信号而言,这几乎使得PA处于不可用状态。

图:典型的PA效率与增益曲线

这一困境该如何应对?这就需要引入“功率回退”(Power-back off)的理念。所谓功率回退,即为了保持输出信号的线性度,在使用时将功率从饱和点适度降低。这意味着为了保证线性度,我们必须牺牲一部分功率输出,也就牺牲了一部分的效率。

图:PA的功率回退使用

在PA的应用中,效率和线性度始终是一对需要权衡的因素。这种权衡体现在多个方面:

1. 在调整输出功率时,效率随功率增加而提升,但线性度却随之下降;

2. 在进行负载匹配时,PA的最佳效率点和最佳线性度点往往并不重合;

3. 在选择供电电压时,更高的电压虽然有利于改善线性度,但也会降低效率。

因此,在PA设计中,如何平衡效率和线性度成为了一个永恒的挑战。

改善输入信号使PA在更高效率区域运行

在PA设计中,会致力于扩展PA的工作区域,以获得更出色的效率表现。例如,设计时会尽量推迟P1dB点的出现,使PA增益的压缩尽量延迟,从而让PA的工作点更接近饱和点,以减少效率损失。

同样,在不需要极高功率的设计中,也可以通过降低饱和功率的设计,也能使PA工作点更加接近饱和功率处的高效区域。

在系统设计层面,也可以采用类似的理念来提升效率。这里,CFR和DPD两项关键技术发挥着重要作用。

CFR:降低信号的峰均比

CFR(Crest Factor Reduction),即波峰因数降低技术,实质上是一种信号“削峰”技术。在现代通信系统中,传输的信号通常是幅度和相位均带有信息的编码信号,这导致信号存在较大的峰均比(PAPR)。峰均比越大,意味着信号中的峰值与均值之间的偏差越大。

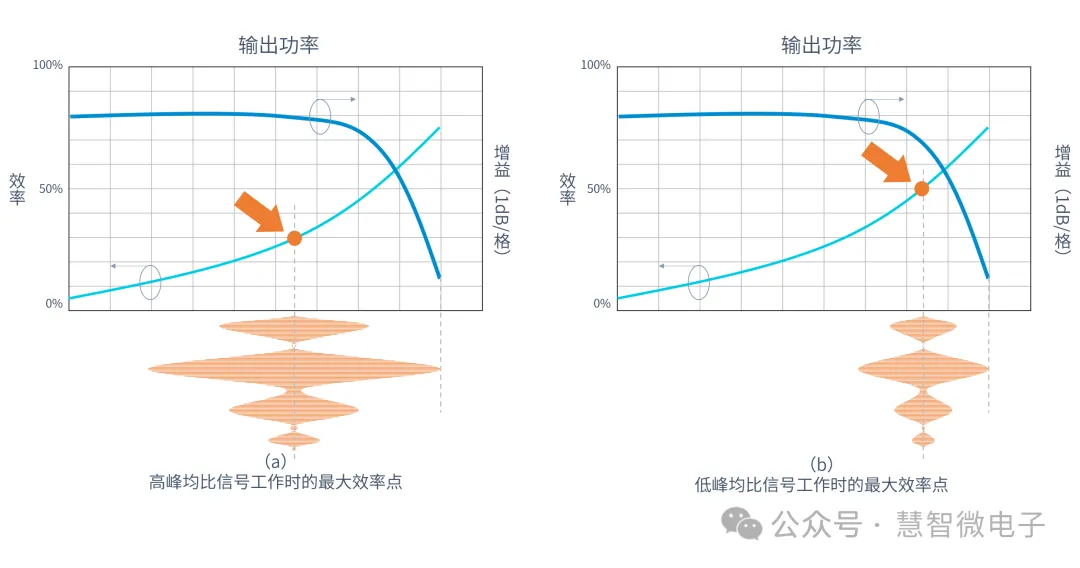

为了保证信号不失真,必须确保信号的最高功率点不超过PA的饱和区。因此,均值功率的工作点需要比饱和功率低至少一个峰均比。所以,信号的峰均比越大,需要回退的功率就越多,从而降低PA的效率。

图:高低两种峰均比信号对PA使用影响对比

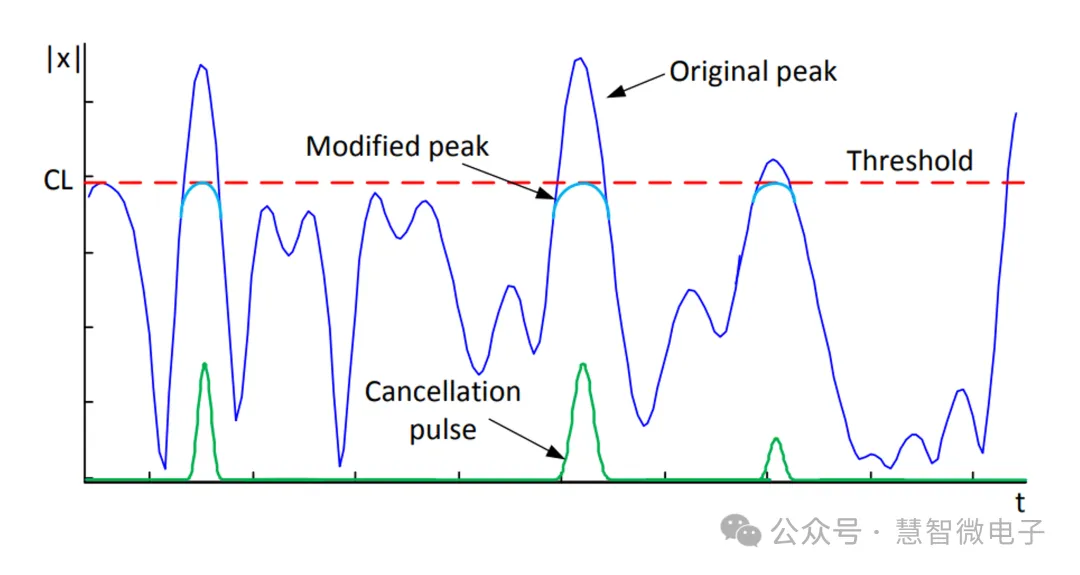

CFR技术通过算法处理原始信号,尽量减少高峰均值信号的出现,或通过限幅、削峰等方法对输入信号进行限制。这样,进入PA的信号就不会有过高的峰值,使PA能够在更高的功率范围内工作,从而提升效率。下图为经过CFR修改后的信号与原始信号对比图。

图:CFR技术对信号峰值的降低

由于OFDM信号的特性,4G/5G信号在时域中具有显著的峰均比(原因见文章《5G PA“记忆效应”的现象、形成与消除》),这使得CFR技术显得尤为重要。系统CFR能力的强弱直接影响到整个系统的性能表现。因此,在基站和手机终端等平台中,CFR技术已经得到了广泛的推广和应用。

DPD:校准PA失真

尽管CFR能够整形信号并降低峰均比,但信号的峰均比始终存在。当PA的功率向上提升时,必然会遇到线性度恶化的问题。此时,DPD技术便发挥作用。

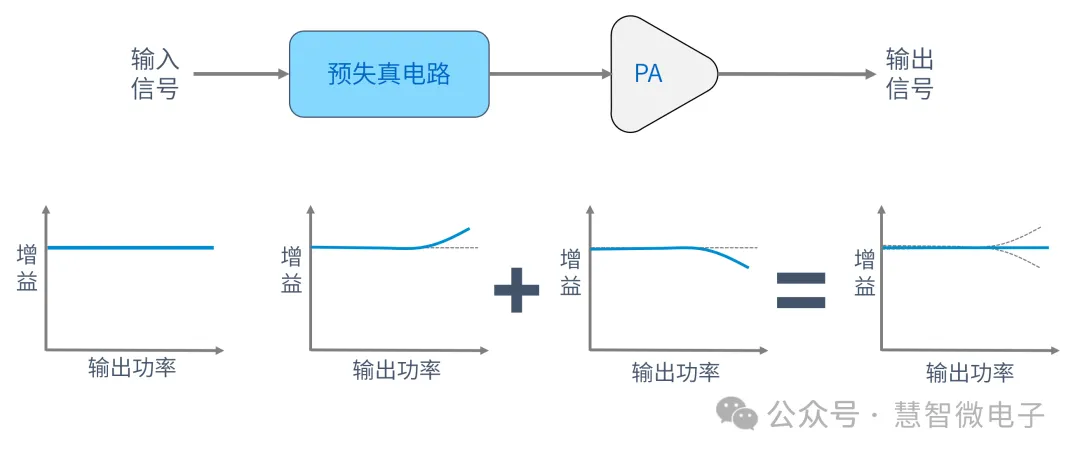

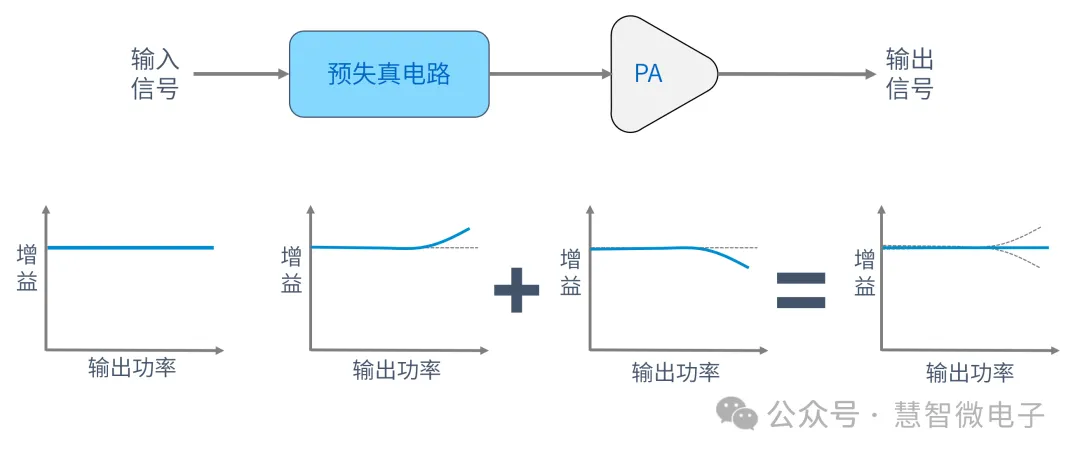

DPD(Digital Pre-distortion),即数字预失真技术,其核心理念是让输入信号提前产生一个与PA相反的失真,以抵消PA引入的失真,工作原理如下图所示。

图:DPD的原理

在DPD的帮助下,PA的线性度得到提升。系统也就能容忍更多的PA线性度恶化,从而使其能够在更高的功率范围内工作,进而提高效率。有DPD和没有DPD时,PA可工作的功率区域如下图所示。

图:DPD下,PA工作的功率区域可以提升

DPD操作完全在数字域进行,无需对PA进行特殊调整即可看到效果。然而,DPD并非万能,它也有自身的局限性。DPD的效果强烈依赖于算法,而移动终端由于功耗和算力的限制,无法支持过于复杂的DPD算法。此外,PA的特性会随温度、负载、偏压和批次等因素的变化而变化,为了获得良好的校正效果,DPD需要不断调整以适应这些变化。同时,DPD需要与PA进行联合调试和特定开发,以充分发挥二者的潜力。

尽管有所限制,DPD仍在蜂窝和Wi-Fi等应用中得到了广泛应用。最近Wi-Fi应用中较为热门的“非线性PA”,就是利用DPD技术和非线性PA技术结合实现的高效率PA技术。

无论是CFR还是DPD,它们都旨在通过算法降低系统对PA线性度的要求,从而提升PA的工作功率和效率。这些技术对平台的算法能力提出了更高的要求。

除了CFR和DPD之外,系统中还采用了另一种方法来提升PA在回退功率点的效率,即“动态调制”。这种方法通过动态调整系统参数,来优化PA的工作效率。

参数的动态调制

动态调制是指根据信号的输出功率,实时调整系统中的某些关键参数(如供电电压、供电电流、负载阻抗等),以达到优化功耗的目的。这种调制方式要求参数的变化必须非常迅速,以适应信号输出的瞬时变化需求,达到接近实时的状态。

以100MHz带宽的5G NR信号为例,调制信号的变化需要达到纳秒级别,才能与包络信号的变化保持同步。这样的速度要求远远超出了芯片内部数字接口电路的能力范围。举例来说,射频前端标准接口协议MIPI RFFE的最大通信时钟频率为52MHz,发送一个完整的MIPI指令需要25个时钟周期,即完成一个控制转变需要0.48us。这个速度比动态调制所需的切换速度慢了上百倍。

因此,为了实现参数的动态调制,通常会利用模拟控制接口,或者直接利用PA的内部特性来完成。

根据调节参数的不同,动态调制主要可分为以下三种类型:

1. Vcc动态调制;

2. Bias动态调制;

3. 负载动态调制。

这些调制方式能够更有效地管理功耗,尤其是功率回退时的功耗,提升系统的整体效率。

Vcc动态调制:供电电压的灵活调整

Vcc动态调制的核心思想在于,使PA的供电电源能够随信号幅度的变化而灵活调整,而非保持固定值。这种动态调整有助于显著提高PA效率,减少不必要的能量损耗。

图:固定电压供电及动态变化电压供电

上图是Vcc动态调制的基本原理。对于高峰均比信号,其幅度随时间快速变化。若采用固定电压供电,将会导致显著的能量浪费。而通过使电源电压跟随信号幅度变化,可以实时优化能耗。

实现Vcc动态调制的两种主要技术是EER(Envelope Elimination and Restoration,包络消除与恢复)和ET(Envelope Tracking,包络跟踪)。

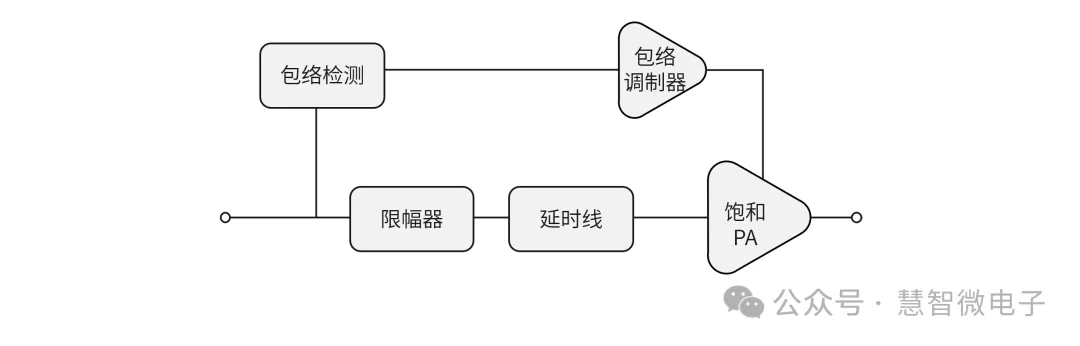

EER技术

EER技术由Kahn教授于1952年提出,其基本原理是将输入信号分解为两部分处理。其基本架构如下图所示。

图:EER PA系统架构

在EER架构中,一路信号忽略包络信息,直接传输至工作在开关状态的PA,从而实现高效放大。这一过程中,包络信息被主动消除,故称“包络消除”通路。

另一路则负责“包络恢复”。首先,通过包络检测电路提取包络信号,然后输入包络调制器。输出的包络信号用作饱和PA的动态供电电源,既实现了电源的动态调制,又完成了包络的恢复。

EER电路的优点在于巧妙地将包络信号和载波信号分离处理,使得两个通路各司其职,互不干扰,从而提高了系统效率。然而,它也存在一些缺点:

1. 由于信号的幅度和相位信息被拆分,因此需要精确对齐两个通路以确保信号的完整恢复。

2. EER过程中存在幅度消除和恢复两个环节,若处理不当可能导致信号失真。

3. 本质上,EER相当于包络信号与高频恒包络信号的混频,可能引发频谱扩展问题。

鉴于EER技术的复杂性和挑战性,另一种更为简洁的PA系统结构——ET技术应运而生。

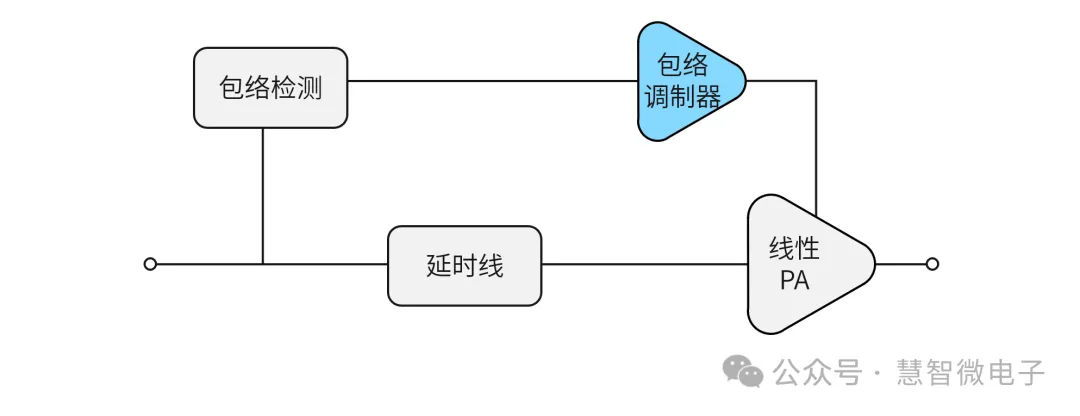

ET技术

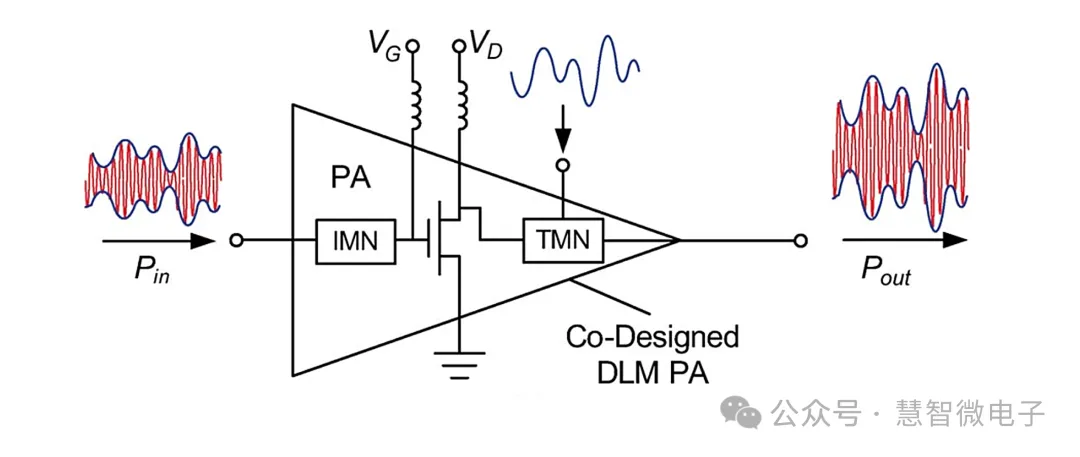

ET,即包络跟踪技术,其核心理念是“跟踪”信号所需的电源幅度,并为PA提供相应电源。这样既节省了功耗,又避免了EER技术中复杂的信号拆分与对齐过程。结合ET技术,可以显著提升系统整体效率。ET系统架构如下图所示。

图:ET PA系统架构

然而,ET技术的性能高度依赖于ET Modulator的表现。为了输出大带宽(100MHz及以上)、大电流(2A及以上)的包络信号,并保持高转换效率,ET调制器的设计面临巨大挑战。随着带宽和电流能力的增强,实现高效率变得愈发困难。

在5G应用中,即使信号带宽维持在100MHz,ET调制器的转换效率通常也仅约80%,意味着存在20%左右的能量损失。因此,ET PA系统的收益必须足以弥补这部分能量损失才能实现整体收益。随着未来信号带宽的不断增加,ET调制器的设计难度将进一步上升。

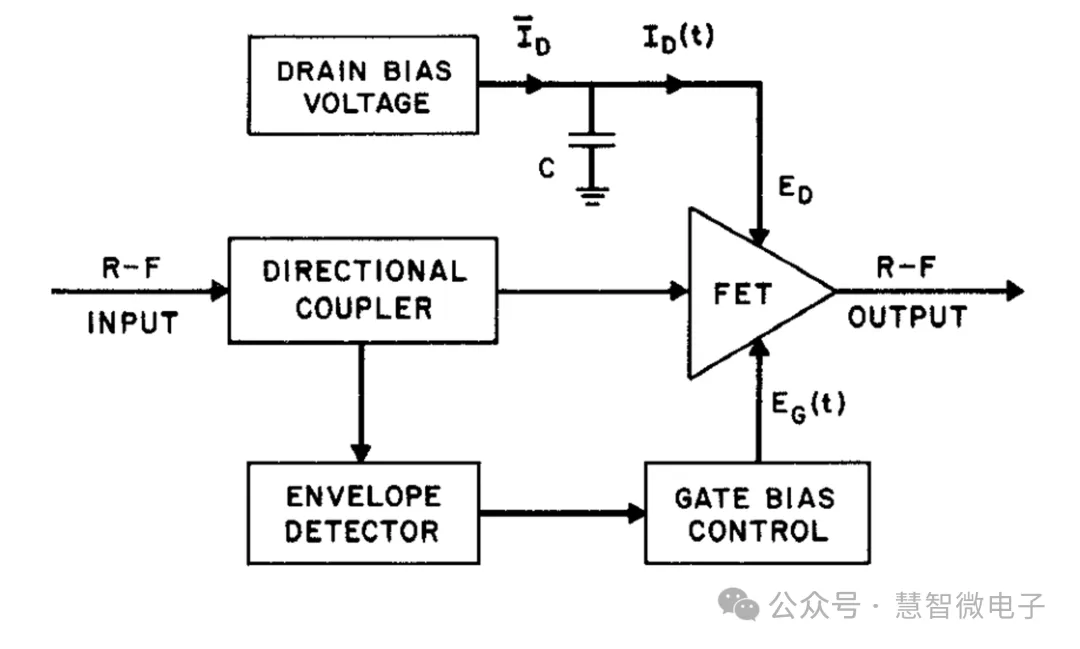

Bias的动态调制

除了对供电电压Vcc进行动态调制外,PA的偏置电流,即Bias,同样可以进行动态调制以优化性能。

Saleh教授等人在1983年的一篇文章中,提出了一种创新的系统架构来提升PA的效率。该架构的核心在于,通过提取输入信号的包络来控制PA的Bias,使Bias能够随输入信号包络的变化而动态调整。这种调整方式目标是实现PA效率的最优化。

图:Saleh教授等于1983年提出的Bias调制PA架构

在现代PA设计中,“动态偏置”特性被巧妙地融入Bias电路的设计中,以提升效率并优化线性度。

以HBT PA为例,利用其偏置电压Vb与Ic电流之间的指数关系,设计师们可确保偏置中心点Vb的尽量稳定。这时当大信号输入时,Ic电流会自动增加,其工作原理如下图所示。这种设计使得在大功率时提升Ic电流,而在小功率时减少Ic电流,从而实现了高效的动态调制。

图:电流的动态调制效应

负载的动态调制

除了电压和电流的动态调制外,还存在一种独特的调制技术,即负载动态调制(Load Modulation)。正如《5G PA的Load-line与Load-pull》一文中所探讨的,PA的负载线(Load-line)在PA设计中占据至关重要的地位。负载线的高低直接影响着PA输出功率的大小。

为了达到理想的输出功率,PA的负载线通常是根据最大输出功率来设计的。然而,这种设计在小功率输出时显得并不经济:此时PA的工作功率远低于其饱和功率。根据先前关于PA特性的讨论,我们知道当PA的工作功率远离饱和功率时,其效率会显著降低。

尽管可以通过降低Vcc电压来减少功率浪费,并降低输出的饱和功率以提升PA在小功率输出时的效率,但这种方法需要依赖ET技术。然而,ET调制器的成本相对较高,并且其在大带宽下的效率是设计中的一大难题。

在这种情况下,对于小功率输出的场景,我们可以利用负载线的特性来降低输出饱和功率,从而提高效率。放大器的输出功率与供电电压成正比,与负载阻抗成反比。在供电电压固定的情况下,可以通过增加放大器输出负载的方式来降低PA的饱和输出功率,从而提升小功率输出点的效率。这正是负载动态调制的核心理念。

在实施方面,负载动态调制主要采用以下几种方法:

1. 通过可调匹配网络实现;

2. 利用Doherty架构实现;

3. 借助Out-phasing架构实现;

4. 采用Load Modulation Balance PA架构。

可调匹配网络实现

可调匹配网络方法的核心在于,在PA的匹配网络中融入可由包络信号控制的可调无源器件。经过精心设计,这种匹配网络能够实现负载阻抗随功率的特定变化。以下是Kenlen Chen教授于2012年所发表论文中展示的架构图。

图:可调匹配网络示意

此方法的直观性和易于理解性是其显著优点。不同功率点对应不同的阻抗,设计师只需通过匹配网络和相应的控制信号设计到相应的目标阻抗,便可实现阻抗的特定转换。

然而,这种方法也存在局限性。其可控范围有限,且受限于匹配网络的固有特性,目标阻抗可能无法完全符合预期变化。此外,寻找满足低插损、高集成度、大范围调节和快速响应的可调器件也是不小的挑战。

因此,多种等效负载阻抗调谐方法应运而生。在这些方法中,负载阻抗并非真正被调节,而是通过电路等效方式使其发生变化,从而达到相应改变PA特性的目的。其中,Doherty、Out-phasing和Load Modulation Balance PA三种实现方案尤为突出。

Doherty架构实现

尽管在之前的《5G射频PA架构》文章中已详细阐述Doherty PA的设计理念,但从负载动态调制的系统角度来看,仍有必要重新审视Doherty PA。深入理解Doherty PA中的动态负载调制效应,将有助于更好地理解其他两种负载动态调制架构。

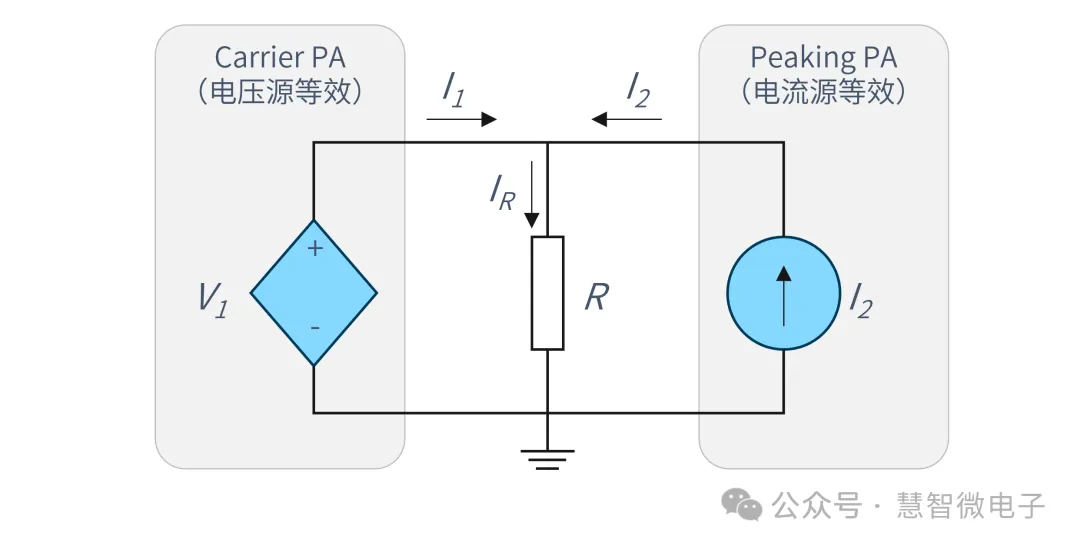

Doherty PA由两个PA组成,但它们并非简单合成。通过对两个PA进行阻抗转换,其工作原理可简化为下图所示。

图:Doherty PA的简化电路

在此图中,左右两个电源分别代表Doherty PA中的Carrier和Peaking两个PA。左侧的Carrier PA通过阻抗变换被设计为等效电压源,而右侧的Peaking PA则设计为等效电流源。这两个PA共同作用于同一个负载阻抗R上。

由于负载R直接连接在电压源V1两端,因此R两端的电压即为V1。根据欧姆定律,流过R的电流为V1/R。

值得注意的是,虽然电压源为电阻R提供电压,但它并不能控制其流向电阻R的电流。因为R上的电流由两部分组成:一部分是电流源I2强制输出的电流,另一部分是向电压源请求的电流。电流源I2会强制输出一个电流I2,因此电阻R向V1请求的电流仅为V1/R-I2。

对于电压源V1而言,其输出电流的大小会受到另一个电流源I2的影响。根据V1输出的电压和电流,我们可以计算出电压源V1看到的等效阻抗为RLoad=V1/(V1/R-I2)。

从上述公式中可以看出,V1看到的阻抗会随着I2输出的大小而变化,仿佛V1的负载阻抗被外部控制了一样。这就是动态负载调制效应。

在Doherty PA设计中,正是利用了这种效应。通过Peaking PA的开启与关闭,可以控制Carrier PA看到的阻抗变化。通过匹配转换网络的设计,当Peaking PA开启时,Carrier PA看到的阻抗降低,从而提升PA的输出功率以实现高功率输出;同时,当关闭Peaking PA时,Carrier PA看到的阻抗提升,此时PA的输出功率降低,换回了较高的效率。

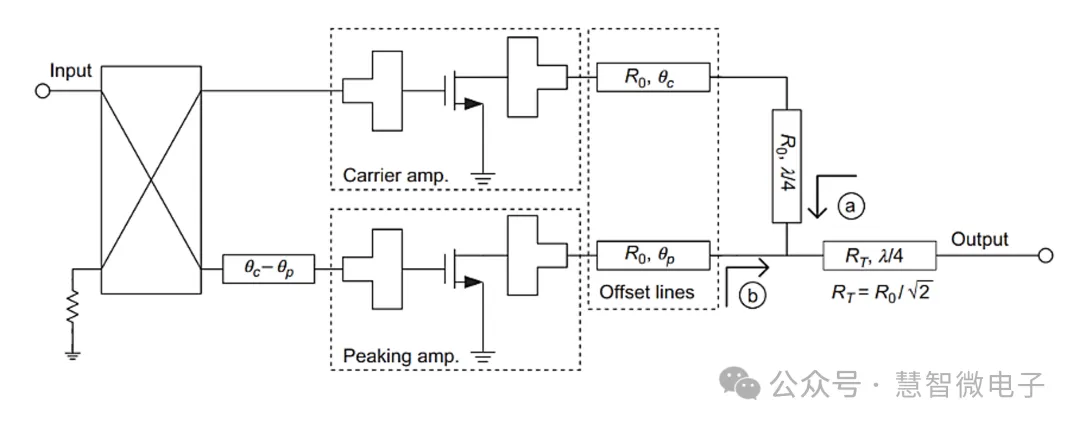

通过这种方式,Doherty PA通过负载线的动态调整实现了高功率和高效率的兼顾。以下为Doherty PA的完整实现架构以及典型的效率特性曲线图。

图:完整的Doherty PA电路

图:理想的Doherty PA效率曲线

尽管Doherty PA在高功率和效率方面表现出色,但它也存在一些明显的缺点。首先,两路PA在切换时会影响线性度,因此通常需要与DPD技术结合使用;其次,Doherty PA利用了大量的阻抗变换网络来实现电压源和电流源的等效变换,这些网络的相对窄带特性限制了Doherty PA的带宽;最后,Doherty PA对负载变化较为敏感,需要相对固定的PA输出阻抗。

在过去几十年的发展中,Doherty PA在基站中得到了广泛应用。在这些应用场景中,有强大的DPD支持、只需针对特定运营商的较窄频段设计、负载相对固定(如固定天线),这些条件恰好满足了Doherty PA的系统需求。

近年来,一些厂商尝试将Doherty PA应用于手机中。为了适应手机等移动终端有限的DPD算力、全球频段支持和不断变化的负载等挑战,手机中应用的Doherty PA通常会弱化其Doherty特性。这样一来,PA就不会对周围环境和带宽过于敏感。然而,这种设计也会相应地削弱Doherty PA对效率的改善效果。

Out-phasing架构的实现

在理解了Doherty PA架构之后,Out-phasing架构就变得相对容易掌握了。

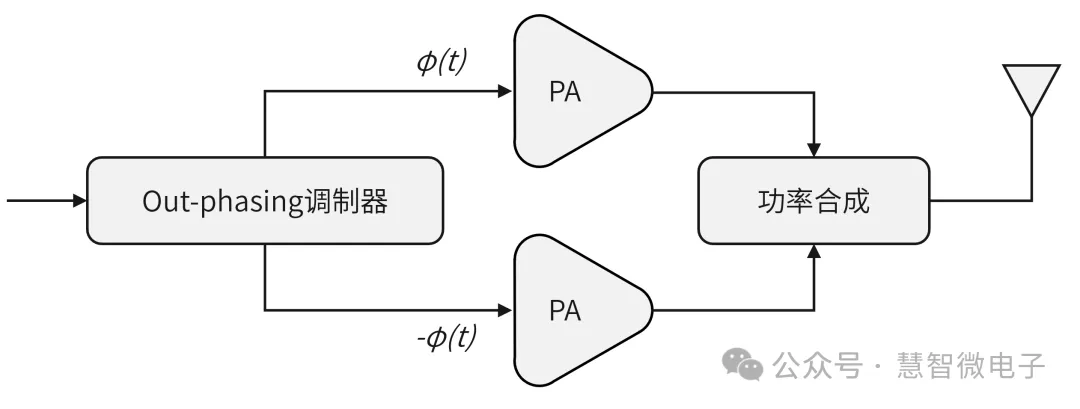

顾名思义,Out-phasing技术是通过利用不同“相位”(Phase)的PA来实现特定设计的。其代表性的架构图如下图所示。

图:Out-phasingPA架构

与理解Doherty PA类似,我们同样可以将Out-phasing PA简化,简化后的等效电路图如下所示。

图:Out-phasing PA简化电路图

从图中可以看出,负载阻抗RL两端的电压随着两个电压源的相位变化而波动,因此流过RL的电流也会随之调整。

需要注意的是,每个电压源所见的等效阻抗并非RL,而是其自身电压与电流的比值。因此,每个电源的等效阻抗也随相位的变化而改变。这意味着,通过调控输入到两路PA的相位,我们可以实现对两路PA负载阻抗的精准控制。这也就是利用Out-phasing架构,对负载进行调制的原理。

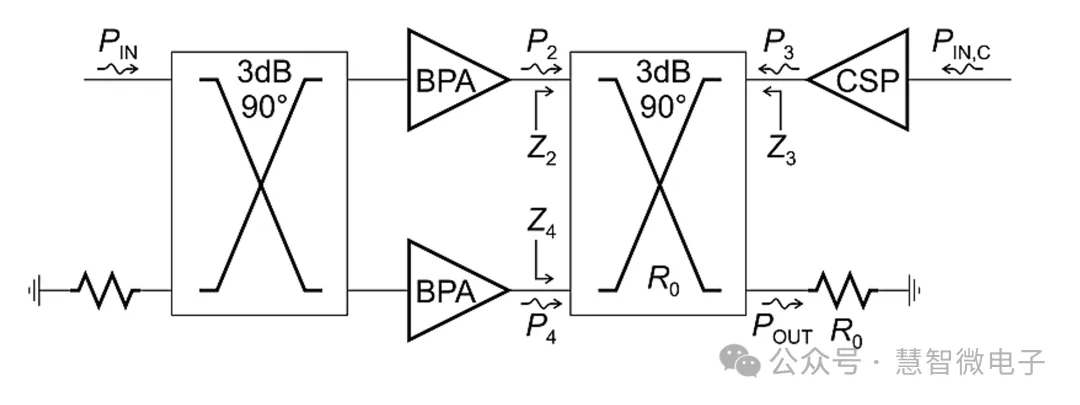

Load Modulation Balance PA架构

Load Modulation Balance PA(LMBA)是射频功率放大器领域的杰出专家Cripps在2016年提出的一种创新型架构。该架构的示意图如下所示:

图:LMBA架构

LMBA是在传统Balance PA(BPA)的基础上进行改造而来的。与传统的BPA(通常只有两路PA进行90度合成)不同,LMBA增加了一路PA,Cripps教授将其命名为CSP(控制信号功率)。CSP信号被注入到90度合成网络的隔离端口中,这一信号的引入会影响两路BPA所见的负载阻抗。通过调整CSP信号的大小,可以等效地控制BPA的负载阻抗,进而影响PA的输出功率和效率。

LMBA的独到之处在于它将影响负载阻抗的PA独立出来,并允许通过单独的信号进行控制。这与Doherty PA和Out-phasing PA只能依赖两路PA自行调节的方式不同,从而极大地便利了负载调制PA的应用。

基于这一基本架构,一些文章已经开展了对Doherty与LMBA结合、不同类别的PA作为CSP PA的影响等方面的研究。对此感兴趣的同学可以查阅相关论文。

总结

在射频系统中,PA是主要的能耗器件。为了有效降低PA的功耗,针对PA的研究也不能只停留在PA单体层面,还应更广泛地从系统角度来探索解决方案。

从系统角度考虑,优化PA效率可能的方案有:

随着技术平台的不断进步和PA技术的持续发展,未来肯定还会有更多创新的系统级手段涌现,以进一步降低PA的功耗。