12月11日,上海集成电路2024年度产业发展论坛暨第三十届集成电路设计业展览会在上海世博展览馆开幕,聚焦“智慧上海,芯动世界”主题,共同探讨集成电路产业未来图景。

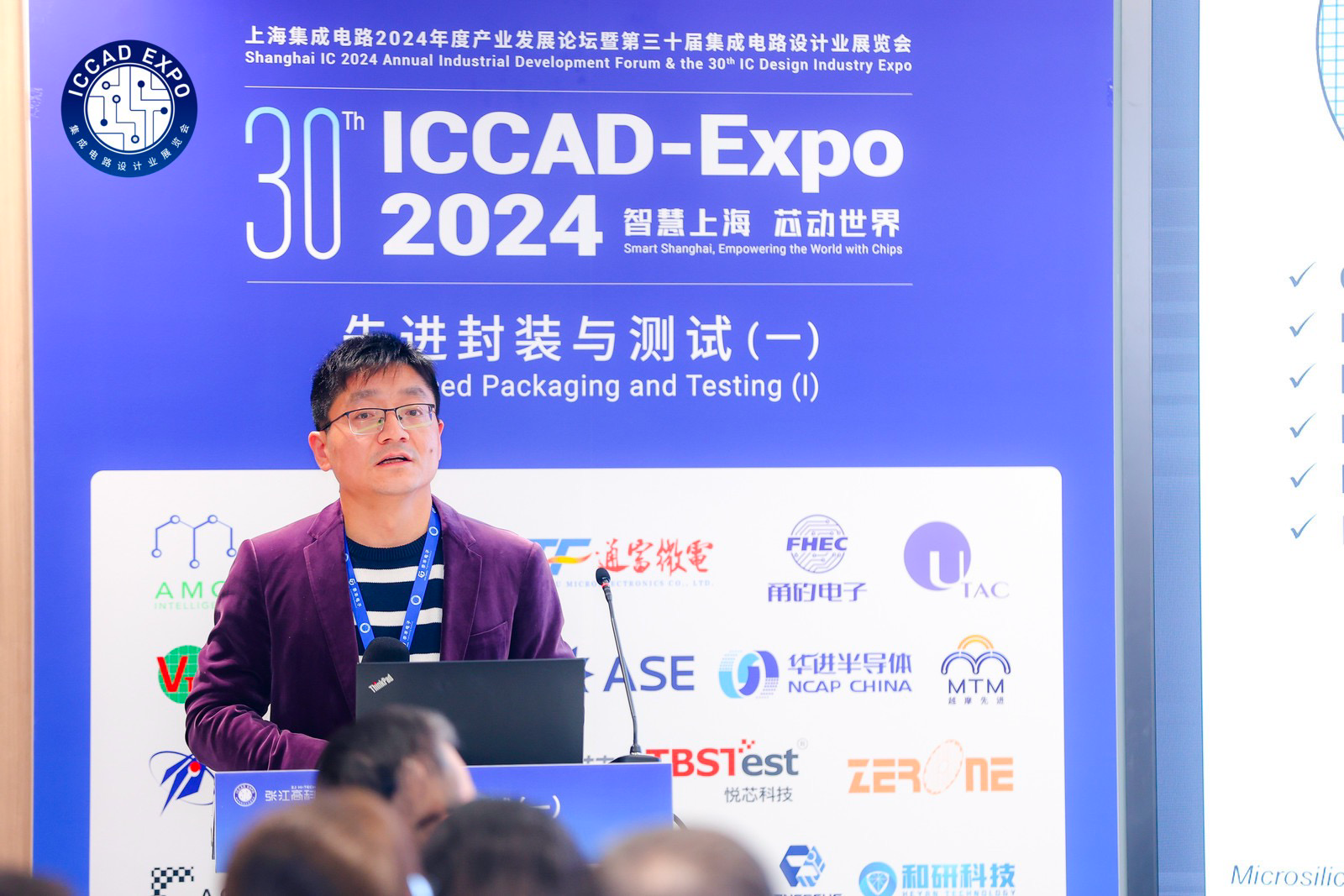

在12日先进封装与测试论坛下午场,杭州晶通科技有限公司(简称:晶通科技)作为国内先进封装行业佼佼者,由其CTO王新带来了重磅演讲——《用于芯粒集成的嵌入式扇出硅桥封装方案解析》,分享了晶通科技对于先进封装行业的预测与分析,及公司的发展状况和技术演进,并重磅发布了其全新的Chiplet封装技术方案MST Fobic,数百名与会观众现场聆听了该演讲报告。

晶通科技CTO王新 图片来源:ICCAD

重磅发布硅桥Chiplet方案,引领技术新纪元

随着AI、HPC等高算力需求日新月异,作为算力载体的高性能芯片的需求也随之水涨船高。然而,先进制程的进阶之路已困难重重,一方面,摩尔定律迭代进度的放缓使芯片性能增长的边际成本急剧上升;另一方面,受限于光刻机瓶颈,前段制程的微缩也愈发困难。

而先进封装是超越摩尔定律、提升芯片性能的关键。随着硅芯片将达到物理极限,通过缩小晶体管实现芯片性能提升成本越来越高,以Chiplet为核心的先进封装技术,成为了集成电路发展的关键路径和突破口。

在先进封装与测试论坛上,王新就多种封装技术进行剖析,并指出硅桥Chiplet将是未来先进封装的主流趋势。随后其重点介绍晶通科技全新的Chilpet封装技术方案MST Fobic。

具体来看,晶通硅桥Chiplet利用Bridge Si技术,实现了亚微米级别的互联,与CoWos或者Interposer方法相比,成本具有明显优势。这种技术使得芯片间的连接更加紧密,有助于提高性能和减少功耗。

晶通硅桥Chiplet封装技术方案MST Fobic 图片来源:记者拍摄

而TMV技术使得晶通硅桥Chiplet能够实现2.5D/3D互联,可以提高芯片间的连接密度和性能。同时,它规避了TSV的Re-Design问题,降低了设计复杂性和成本。

晶通硅桥Chiplet既可灵活实现BGA/Bump封装方式,也可以与基板整合形成hybrid package,这种优化的结构可以满足不同应用场景的需求。而通过采用Face up FO方式,能够实现2um级别的Fine Pitch RDL。这种高密度的重布线层设计超越了eWLB等传统方案,有助于实现更紧凑的封装设计。

另外,晶通硅桥Chiplet技术提供了优异的贴片与解键合方式,能够实现±1微米量级的位置精度。这对于提高封装良率和可靠性至关重要。

随着半导体产业的不断发展,硅桥Chiplet有望成为先进封装的主流趋势。这一技术以其独特的优势,如布线精度高、可封装引脚密度高、封装体积小等,满足了高性能计算、网络等领域对超高密度封装的需求。

目前,硅桥Chiplet技术已被广泛应用于AI服务器、AI手机、AI PC等高性能计算领域,成为推动这些领域发展的关键技术之一。数据显示,2024年硅桥封装方案的市场占有率达到24%,预计2025年将达到55%,该技术显示出强劲的市场增长潜力。

Cowos Distribution预测 图片来源:记者拍摄

由于技术门槛较高,国内真正掌握该技术的企业并不多,这使得晶通科技在市场中具有显著的竞争优势。随着技术的不断成熟和市场的不断拓展,晶通科技有望凭借嵌入式扇出硅桥封装技术迎来高速发展阶段,为股东和客户创造更多价值。

团队之道:低调务实,高效前行

功以才成,业由才广,技术研发归根结底要靠人才。

晶通科技团队核心成员在先进封装领域有着深厚的技术积累。据悉,晶通科技是国内最早布局和研究Chiplet的团队之一,通过在国外多年的积累,在国内最早实现了高密度晶圆级扇出型工艺,并自主开发了FOSiP技术路线,能满足不同线宽需求的扇出型封装,实现了从普通线宽到细线宽、高精度的扇出型封装,展现了强大的技术研发能力。

业内人士透露,晶通科技专注于产品研发和客户服务,致力于通过技术创新为客户创造价值,不过度宣传或夸大自身实力。公司以低调务实的态度,持续推动先进封装技术的发展,为公司在行业内树立了良好的口碑和形象。

经过多年的发展,晶通科技已具备丰富的先进封装方案设计、仿真验证、工艺开发、产线管理的核心knowhow,经过在核心制程、工艺、设备、耗材等层面的长期研发投入,成功解决了产品在翘曲、位移、重构晶圆、超高密度等方面的难度挑战,是国内鲜有的同时掌握晶圆级fan-out和Chiplet方案的集合体。目前公司已在Fan-out和Chiplet领域布局完整专利,在芯片设计选型、模组的功能实现等方面为客户提供国际领先水准的定制封装方案。