1.南科大林龙扬课题组在ISSCC 2026发表两项智能视觉芯片研究成果;

2.中科院实验室关于大模型容错和FHE统一硬件架构等三篇论文被DAC2026录用;

3.西安交大雷铭教授团队在结构光照明三维成像领域取得新进展;

4.中国科大揭示二维材料hBN中色心自旋弛豫的温度依赖特性

1.南科大林龙扬课题组在ISSCC 2026发表两项智能视觉芯片研究成果

近日,国际固态电路大会(ISSCC 2026)在美国旧金山举行。ISSCC被学术界和工业界公认为集成电路设计领域的最高水平会议,享有“芯片奥林匹克大会”之美誉。该会议始于1953年,历来是国际最尖端集成电路技术的首发平台,每年吸引超过3000名来自全球工业界与学术界的参会者,每篇录用的论文均代表了芯片领域最前沿的研究成果。

南方科技大学深港微电子学院林龙扬课题组在智能视觉芯片方向取得重要进展,两项最新研究成果入选ISSCC 2026。其中一篇为面向边缘智能视觉应用的“感存算一体”智能视觉SoC芯片,题为“A 55nm Intelligent Vision SoC Achieving 346TOPS/W System Efficiency via Fully Analog Sensing-to-Inference Pipeline”,由南科大联合犀灵视觉、睿科微电子共同研发。另一篇为面向航天场景的自修复图像传感器芯片,题为“A Radiation-Hardened Self-Healing CMOS Imager with Online Pixel/Logic Annealing and Tile-Adaptive Compression for Space Applications”。林龙扬助理教授为两篇论文的通讯作者,南方科技大学深港微电子学院为第一通讯单位。两项工作分别攻克了边缘视觉系统中的模数转换能效瓶颈及太空任务中的辐射损伤与通信带宽瓶颈,实现了智能视觉芯片技术的突破性创新。

以上研究得到了国家自然科学基金、广东省项目、南科大-犀灵视觉联合实验室以及南科大-存厚科技联合实验室的支持。

论文1:全模拟端到端智能视觉芯片,打破模数转换能效瓶颈

随着人工智能的发展,能够处理特征提取、目标检测等复杂任务的边缘AI视觉系统需求日益增长。传统的智能视觉芯片多采用传感器与数字处理器芯片堆叠的架构,虽在一定程度上缓解了数据传输压力,但仍严重依赖功耗极高的模数转换器(ADC)。为突破功耗瓶颈,学术界曾提出“传感器内”(in-sensor)或“近传感器”(near-sensor)计算技术,但现有方案往往只能处理特定任务,受限于存储容量与硬件固化,难以支持复杂的卷积神经网络。更严峻的是,在处理多层神经网络时,计算节点之间频繁的模数/数模信号转换带来了巨大的延迟与能耗开销,已成为制约边缘视觉芯片迈向高算力与高能效的核心技术瓶颈。

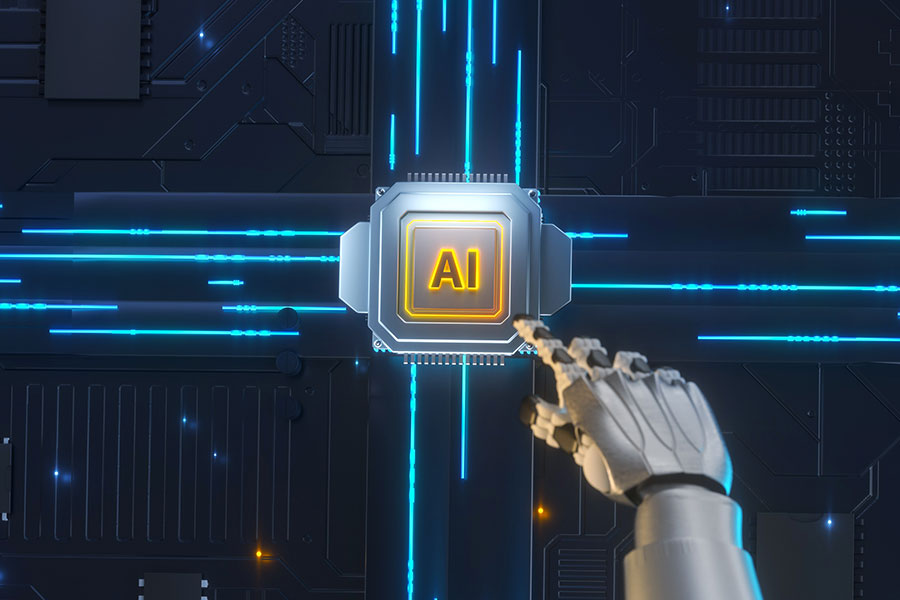

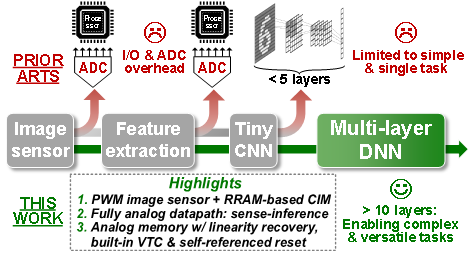

图1:智能视觉处理范式对比与本文亮点

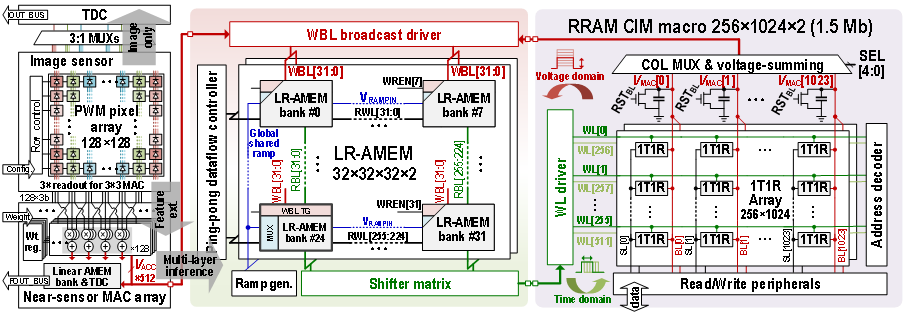

为此,本研究提出了一种基于“全模拟”计算范式的多功能智能视觉SoC芯片(图1、图2),彻底消除了端到端视觉任务中传感器与计算单元之间、以及神经网络各层之间的模数转换操作。芯片创新性地将脉宽调制图像传感器与基于阻变存储器(RRAM)的存算一体架构深度融合,并引入核心模块—带有内置电压-时间转换器和线性恢复能力的模拟存储电路(LR-AMEM)。在运行多层网络时,传感器输出的时间脉冲直接驱动存算阵列,计算所得的电压被存入模拟存储单元;随后,存储器内置的转换电路将电压无缝还原为时间脉冲,直接驱动下一层计算。这种“时间-电压-时间”的纯模拟信号流,不仅规避了高功耗的模数转换与量化噪声,还利用底层电路特性有效抵消了电荷域RRAM模拟存算中固有的非线性误差,并在不增加额外校准电路的前提下,实现了对工艺偏差、环境温度和电压波动的强鲁棒性。

图2. 全模拟域智能视觉SoC芯片架构图

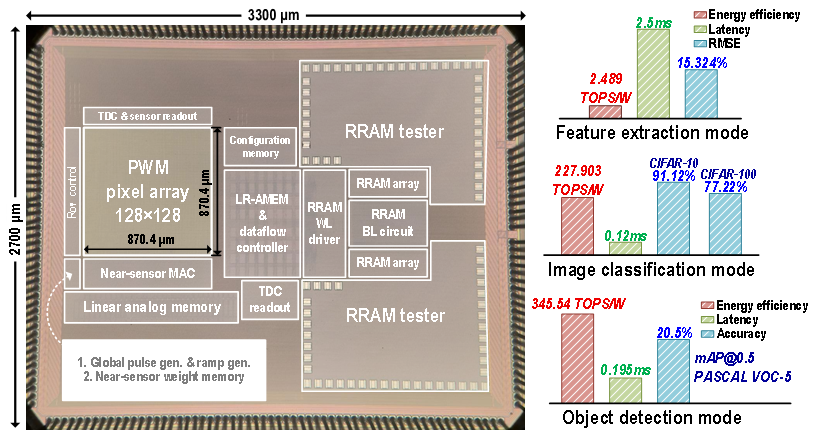

该方案采用55nm CMOS工艺进行了流片验证(图3)。实测数据显示,该芯片实现了11 pJ/(像素·帧)的极低传感能耗,乘加运算峰值能效高达8,791 TOPS/W,系统级端到端能效达到346 TOPS/W,能够高效、低延迟地完成从特征提取、图像分类及目标检测等多种边缘视觉任务。与现有的智能图像传感器相比,这颗全模拟视觉芯片的系统级能效提升了75.6倍至966倍。该成果充分验证了全模拟信号链路在边缘端复杂视觉计算中的可行性与巨大潜力,为未来超低功耗、全集成的边缘智能视觉系统提供了极具竞争力的技术方案。

图3:芯片照片与三种视觉任务性能

论文2:面向航天应用的自修复CMOS图像传感器,突破辐射损伤与带宽双重瓶颈

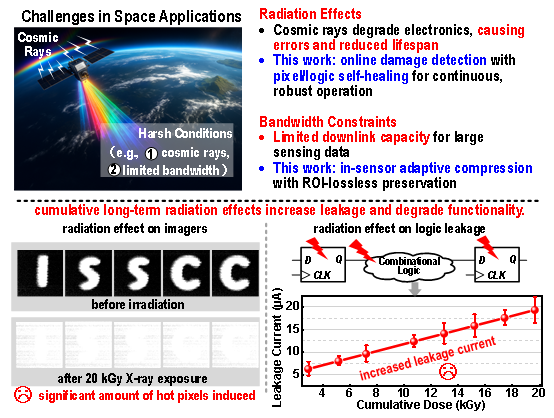

航天探测与地球观测任务离不开高可靠的CMOS图像传感器,但在太空恶劣的辐射环境下,芯片的像素阵列和逻辑电路极易因辐射累积产生“热像素”、漏电流和时序错误等硬件损伤,最终导致成像质量严重退化。传统的抗辐射加固技术(如特殊器件版图或硬件冗余)往往只能被动防御,不仅面积开销大,且无法主动“治愈”已经发生的物理损伤。虽然此前有研究引入了热退火技术来修复受损器件,但这些方案必须中断拍摄才能进行修复,且无法覆盖逻辑电路的损伤。与此同时,航天器在轨产生的海量图像数据远超卫星下行链路的带宽极限。因此,如何打造一款既能在强辐射下“边工作边自愈”,又能智能压缩数据的图像传感器,成为太空视觉探测领域的重大挑战。

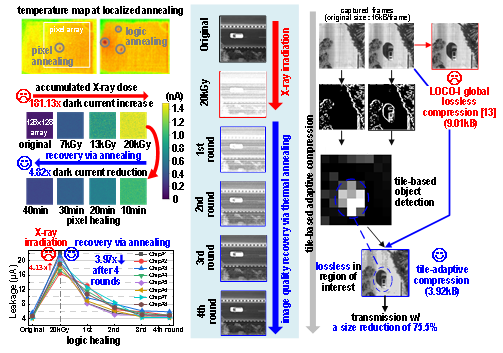

图4:太空应用的挑战与本工作的贡献

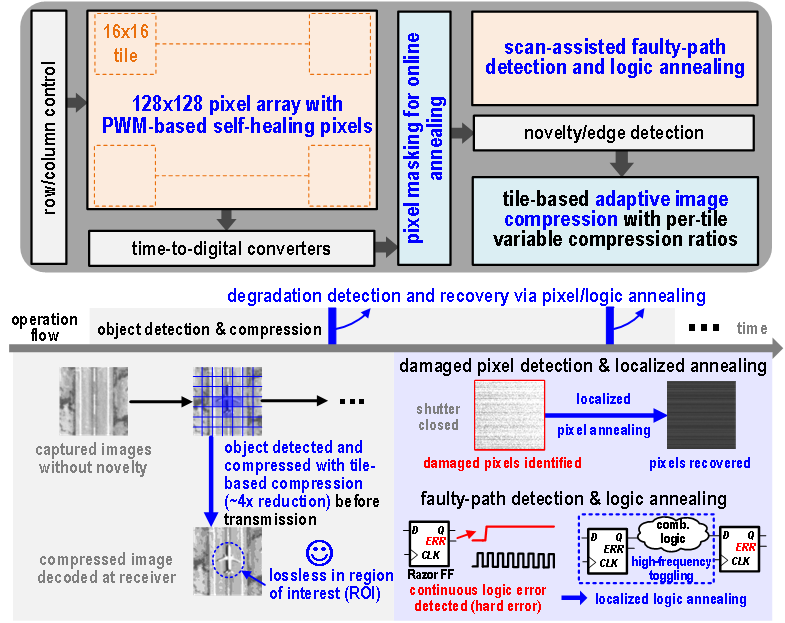

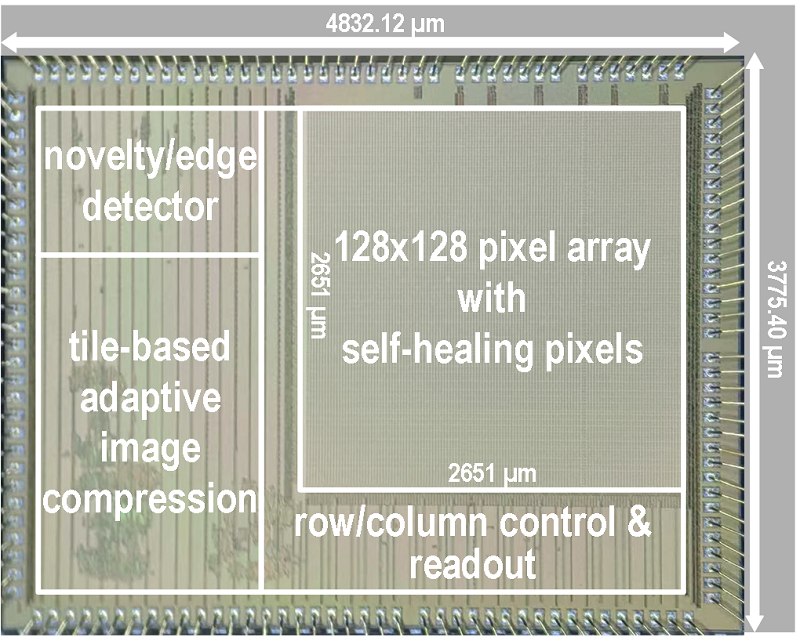

为应对上述挑战,本项研究提出了一款可自修复辐射损伤的CMOS图像传感器(图4,图5)。该芯片的创新之处在于,同时集成了针对像素电路和数字逻辑电路的“局部在线热退火”修复技术,以及基于图像分块的自适应压缩引擎。在像素端,芯片采用特殊的6T脉宽调制像素电路设计。当系统检测到因辐射受损的异常像素时,会对其施加正向偏置以触发局部高温退火,从而缓解晶格位移缺陷和俘获电荷引起的辐射损伤。值得一提的是,该芯片在修复期间无需停机,而是通过“像素掩蔽”技术利用相邻像素的数据进行智能插值补偿,实现了在线修复下的连续成像。在逻辑电路端,系统利用改进的冗余触发器精准捕捉因辐射累积导致此时序错误的故障路径,随后通过局部高频时钟产生焦耳热,精准地对受损逻辑电路进行热修复,整个过程对帧率几乎无影响。同时,芯片内置的自适应图像压缩引擎能够实时评估画面复杂度,对画面中的关键目标或复杂边缘(感兴趣区域)实施无损保留,对平缓背景区域则进行高强度压缩。

图5:抗辐射自修复CMOS图像传感器架构与工作流程

极端环境实测结果显示(图6),该芯片在经受高达20kGy的X射线强烈辐射后,初始暗电流暴增近181倍,画面严重退化;但在启动数轮在线退火修复后,相较于20kGy的受损状态,像素和逻辑电路的漏电流分别大幅下降了4.82倍和3.97倍,图像质量得到显著恢复,接近初始清晰水平。此外,其自适应压缩技术在保留关键细节的前提下,将图像数据量有效压缩了约75%。该项成果成功突破了太空辐射损伤与通信带宽受限的双重技术瓶颈,为未来需求超长续航和极高可靠性的太空探测任务提供了强有力的视觉芯片支撑。

图6:X射线辐射修复与自适应图像压缩测试

图7:芯片照片

相关论文

论文1:Z. Yang, H. Yu, X. Liu, Z. Kong, H. Li, L. Ran, Z. Lyu, X. Feng, L. Zhao, Y. Li, J. Li, F. Zhou and L. Lin, "A 55nm Intelligent Vision SoC Achieving 346TOPS/W System Efficiency via Fully Analog Sensing-to-Inference Pipeline," 2026 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 2026, pp. 126-128, doi: 10.1109/ISSCC49663.2026.11409209.

论文2:Q. Cheng*, Z. Yang*, H. Li, Q. Li, Z. Kong, G. Niu, Y. Liang, J. Li, J. Yoo, M. Hashimoto and L. Lin, "A Radiation-Hardened Self-Healing CMOS Imager with Online Pixel/Logic Annealing and Tile-Adaptive Compression for Space Applications," 2026 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 2026, pp. 390-392, doi: 10.1109/ISSCC49663.2026.11408995.

(来源:南方科技大学)

2.中科院实验室关于大模型容错和FHE统一硬件架构等三篇论文被DAC2026录用

近日,中国科学院计算技术研究所处理器芯片全国重点实验室关于大模型容错《STAC: Spatial-Temporal Activation Contextualization for Resilient LLM Inference》和全同态加密(FHE)统一硬件架构的论文《Chimera: A Unified FHE Accelerator with Enhanced Compatibility for TFHE》分别被电子设计自动化领域顶级会议DAC 2026(Design Automation Conference,CCF-A类)接收。

论文

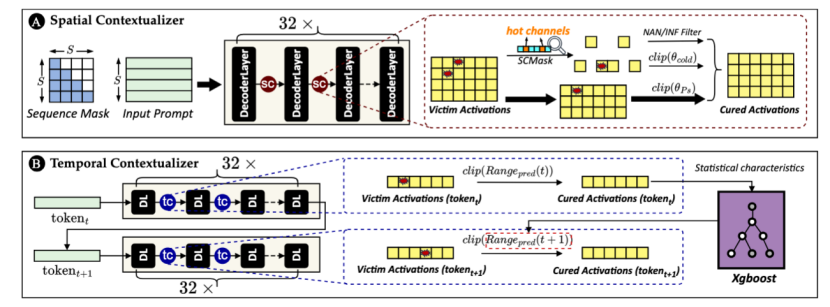

《STAC: Spatial-Temporal Activation Contextualization for Resilient LLM Inference》

该论文第一作者为实验室集成电路课题组博士生张仁刚,通讯作者为刘自臻特别研究助理和李华伟研究员。针对大语言模型(LLM)在安全关键领域部署时面临的软错误威胁,研究团队提出了一种轻量级的时空激活上下文感知容错推理框架STAC。现有低成本防御方法普遍依赖静态阈值,难以适配LLM推理过程中独特的“异常值二分性”问题:高幅值激活既可能是语义表达所必需的功能性异常,也可能源于软错误引发的故障性异常。此外,LLM推理中预填充阶段存在结构化功能异常,解码阶段激活特征随自回归过程发生时间漂移,静态阈值难以同时兼顾两者。为此,团队提出STAC框架,采用“空间感知+时间预测”的解耦机制:预填充阶段利用热点通道掩码区分合法的大数值功能异常,对冷通道严格裁剪;解码阶段提取轻量级统计特征构建XGBoost动态预测器,自适应调整每个token的保护边界。实验表明,STAC在保持无故障精度的同时,将最大可容忍故障率提升至10-6,相比现有低成本防御方法实现10倍可靠性提升,平均延迟开销仅3.85%。该工作基于激活的时空演化特性构建自适应容错机制,在保证效率的同时显著提升系统可靠性,为大语言模型在安全关键场景中的部署提供了可行路径。

论文

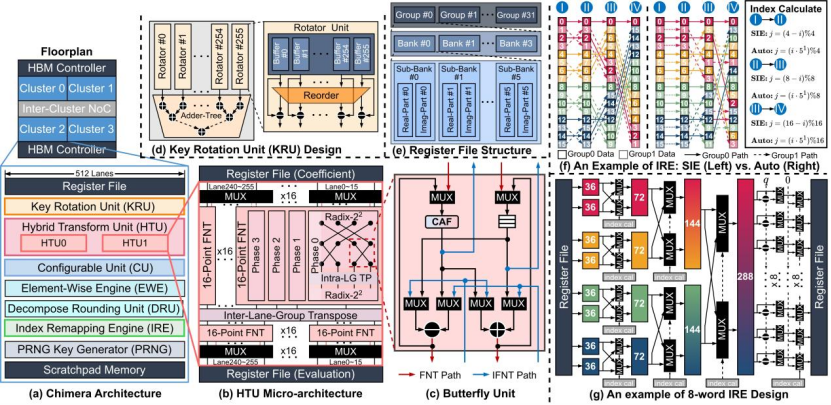

《Chimera: A Unified FHE Accelerator with Enhanced Compatibility for TFHE》

该论文第一作者是实验室在读研究生华腾辉,通讯作者和合作者包括穆嘉楠特别研究助理、叶靖副研究员和李华伟研究员等。为了提升FHE加速器通用性,需要探索统一架构支持不同加密体系。针对现有统一FHE加速器普遍存在兼容性不足、硬件利用率不高以及关键路径性能受限等问题,研究团队提出了新型统一加速器 Chimera。面向多样化 FHE 工作负载在计算模式、数据组织与资源需求上的显著差异,Chimera 从计算架构、功能单元、存储组织以及配置优化等多个层面开展协同设计,在保持统一架构通用性的基础上,显著增强了对复杂逻辑型 FHE 计算的支持能力。与此同时,Chimera 还结合面向系统约束的自动化配置优化方法,能够根据算法参数和硬件配置对运行参数进行协调优化,从而进一步提升整体执行效率与硬件资源利用水平。实验结果表明,与当前先进的统一 FHE 加速器Trinity相比,Chimera 在 TFHE 类工作负载上平均实现 14.64×的性能提升,同时在 CKKS 类工作负载上保持可比性能,且面积开销仅增加 9.6%。该工作展示了统一 FHE 加速器在兼顾通用性、高性能与可扩展性方面的显著潜力,为高效支撑多体系 FHE 应用提供了新的技术路径。

此外,实验室集成电路课题组与北京邮电大学、香港中文大学合作的另一篇关于芯片可靠性评估的论文《ATLAS: Asynchronous Topological Learning for Accurate FIT Prediction via Decoupled Graph Neural Networks》也被本次DAC 2026接收,该论文第一作者来自北京邮电大学,刘自臻特别研究助理为共同通讯作者。

DAC 2026

DAC是电子设计自动化领域的国际顶级会议,主要聚焦集成电路设计、芯片设计方法学、电子系统自动化工具及其软硬件协同优化技术的前沿研究成果。自1964年创办以来,DAC始终引领全球电子设计自动化(EDA)领域的创新与发展,被誉为“芯片设计领域的风向标”,对推动半导体技术、人工智能驱动的设计工具以及高能效计算架构的研究起到了核心推动作用。第63届DAC会议将于2026年7月在美国加利福尼亚州举行,本届会议最终录用率仅为22.3%。

处理器芯片全国重点实验室依托中国科学院计算技术研究所,是中国科学院批准正式启动建设的首批重点实验室之一,并被科技部遴选为首批 20个标杆全国重点实验室,2022年5月开始建设。实验室学术委员会主任为孙凝晖院士,实验室主任为陈云霁研究员。实验室近年来获得了处理器芯片领域首个国家自然科学奖等6项国家级科技奖励;在处理器芯片领域国际顶级会议发表论文的数量长期列居中国第一;在国际上成功开创了深度学习处理器等热门研究方向;直接或间接孵化了总市值数千亿元的国产处理器产业头部企业。(来源:处理器芯片全国重点实验室)

3.西安交大雷铭教授团队在结构光照明三维成像领域取得新进展

看得更深、更清、更快,是生命科学研究的永恒追求。从神经元的复杂网络到线粒体的瞬息动态,每一个生命过程都在三维空间中上演。然而,传统成像技术往往需要在成像深度、速度、分辨率之间做出取舍。西安交通大学雷铭教授团队设计的高信噪比光学切片结构光显微系统,如同为显微镜装上“智能降噪器”,让结构光显微镜既能穿透毫米级厚组织,又能捕捉细胞器级的精细动态。

图1 高信噪比光学切片结构光显微系统

想象一下,你想观察一个完整的器官,比如老鼠的大脑,看里面的神经元是如何连接成网的。传统的显微镜往往只能看薄薄的切片,想看厚一点的样本,光线就会被散射和吸收,图像变得模糊不清,就像隔着毛玻璃看东西。为了看清活体组织内部的3D结构,科学家们开发了各种显微技术。比如,共聚焦显微镜,它像用一个小针眼挡住杂散光,图像对比度高,但扫描速度慢,光照强,容易把活细胞“照死”。光片显微镜光照温和、速度快,但对样本的大小和透明度要求苛刻。光场显微镜能一次拍下整个3D图像,速度极快,但牺牲了图像的精细度。在众多技术中,有一种叫光学切片结构光照明显微镜(Optical Sectioning Structured Illumination Microscopy, OS-SIM)的方法具有综合性优势。它的原理很巧妙:不是用“针眼”挡光,而是向样本投射一组有明暗条纹的光,像给样本“打上码”。由于只有焦平面上的条纹是清晰的,离焦背景是模糊的,通过计算,就能把属于焦平面的清晰信息解调出来,实现光学切片。这就像从一张叠影重重的照片里,只提取出你想要的那一层。OS-SIM的优点很明显:速度快、光毒性低,非常适合观察活细胞的动态。但它有一个致命伤:看不了厚组织。当光线穿透到组织深处,比如几百微米甚至几毫米厚的大脑,荧光信号会急剧衰减,同时背景噪声(杂散光)会大大增强。这导致投射的条纹对比度变差,就像在浓雾里打光,看不清条纹了。此时,传统的解码算法就会失效,输出的图像信噪比极低,结构淹没在噪声里。因此,OS-SIM一度被认为只适合看20微米以下的薄样本。这就是当前领域面临的核心科学问题:如何在保持OS-SIM高速、低毒优势的同时,突破厚组织带来的信噪比瓶颈,实现更深、更清晰的3D成像?

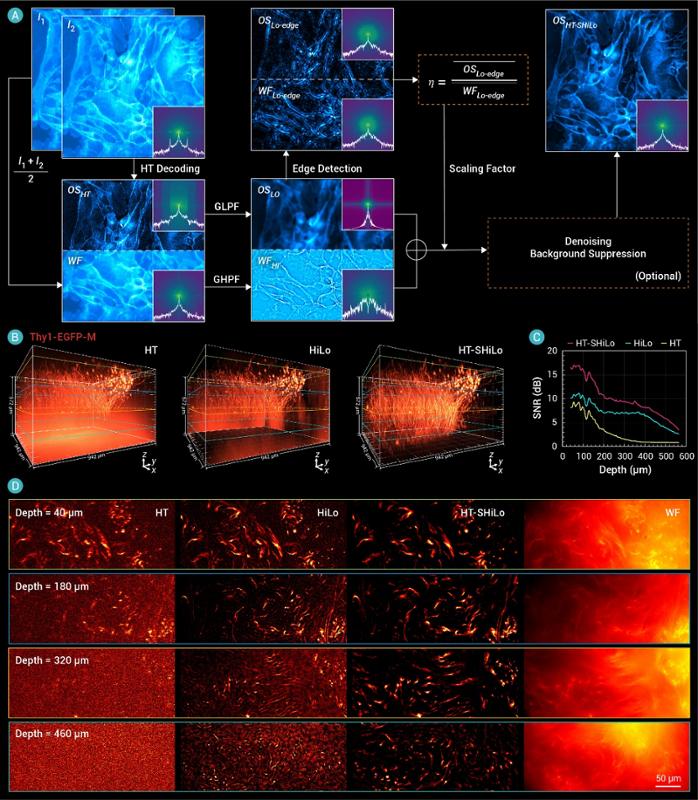

针对这个难题,西安交通大学物理学院雷铭团队最近开发了一套全新的策略——“HT-SHiLo”(图2A)。它不像传统方法那样“硬啃”那些已经变模糊的条纹信息,而是采取了一套组合拳:

取长补短——它从两张带条纹的图像中提取可靠的、包含结构轮廓的低频信息;同时,从常规的宽场图像中提取精细的边缘细节(高频信息)。把这两者巧妙地融合,就得到了一幅既清晰又干净的光切片图像。

空域重构——整个过程在空间域进行,避免了耗时的傅里叶变换,处理速度极快,单层图像仅需5.4毫秒,为实时3D成像铺平了道路。

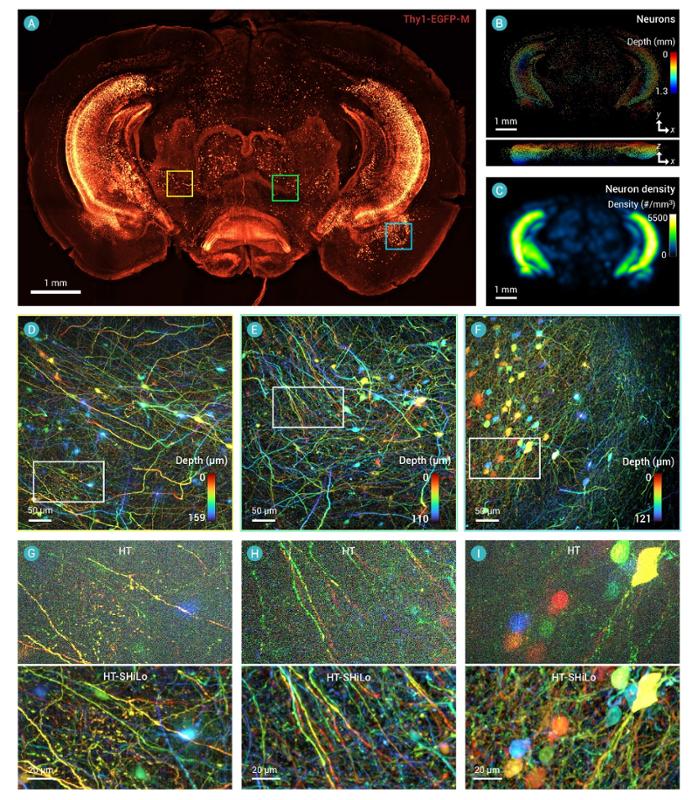

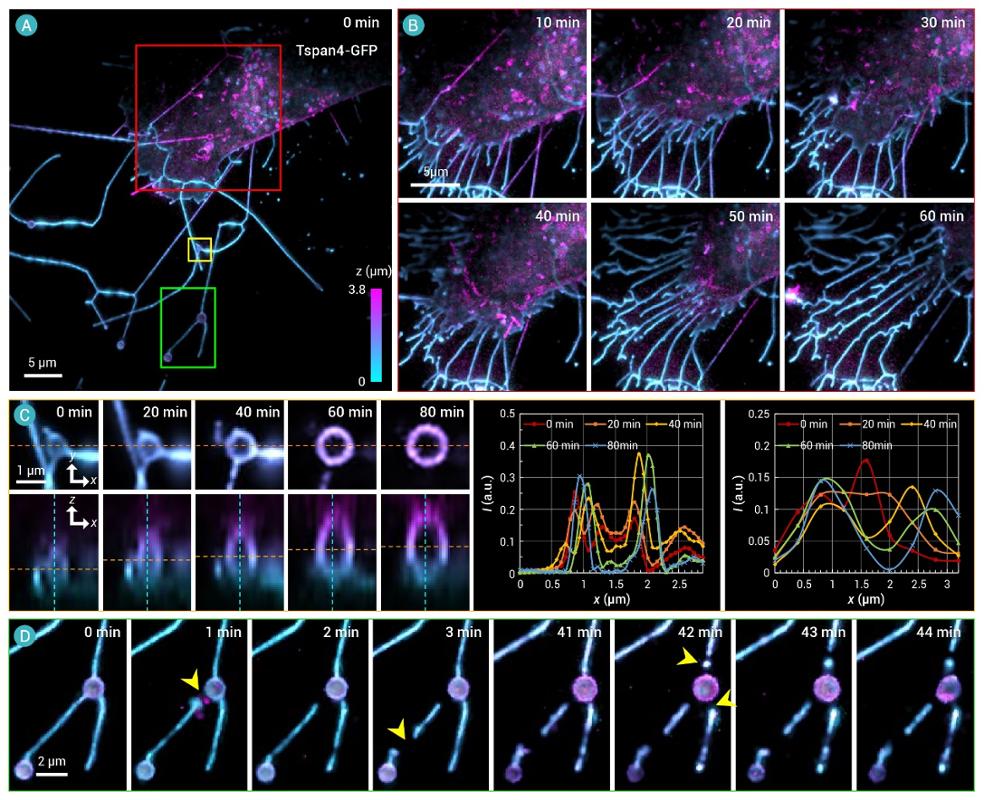

令人惊喜的是,这项技术能将图像的信噪比提升约10分贝,成像深度直接翻倍(图2B-D)。用它观察经过透明化处理的老鼠大脑,穿透深度能达到惊人的2.4毫米。无论是小鼠脑中密密麻麻的神经元(图3)、果蝇大脑里调控昼夜节律的时钟神经元,还是人类结肠类器官的精细结构,都展现出了前所未有的清晰度。更重要的是,它依然保持着OS-SIM“温柔”的本色。使用极低的光照,他们成功记录下了活细胞中线粒体长达5分钟的3D动态变化(包括融合与分裂),以及迁移体——一种在细胞迁移过程中产生的新细胞器——长达80分钟的生长和脱落全过程(图4)。

图2 基于HT-SHiLo的OS-SIM实现高信噪比3D成像。(A) HT-SHiLo算法流程图。HT,希尔伯特变换;OS,光学切片图像;WF,宽场图像;GLPF,高斯低通滤波器;GHPF,高斯高通滤波器;Lo,低频;Hi,高频。(B) HT、HiLo和HT-SHiLo算法重建的透明化小鼠脑切片神经的3D图像对比。(C) 各算法在不同成像深度下的信噪比。(D) 不同成像深度下各算法所得光学切片与WF图像的对比。

图3 组织透明化的小鼠脑切片中神经与神经元的三维图像。(A) 全脑切片的最大强度投影(MIP)图像。(B) 检测到的神经元三维分布图。(C) 神经元密度分布图(单位:个/mm³)。(D-F) 图A中对应区域的高度伪彩MIP图像。(G-I) 图D-F中放大区域的HT算法与HT-SHiLo算法成像效果对比。

图4 迁移中的Tspan4-GFP标记的NRK细胞及其迁移体的动态延时成像。(A) 初始时刻迁移细胞的高度伪彩MIP图像。(B) 图A中红框区域的细胞迁移过程,可见细胞尾部留下收缩纤维。(C) 图A中黄框内迁移体的生长过程。分别展示了沿橙色线的xoy平面和xoz平面截面图,并测量了沿橙色线和蓝色线的荧光强度变化。(D) 图A中绿框内迁移体的断裂过程。

HT-SHiLo算法让OS-SIM从一个“浅层观察者”升级为能深入组织内部的“探索者”,同时保持了高速、低光毒性的核心优势。该技术已在小鼠脑组织、果蝇神经、人类类器官、活细胞线粒体和迁移体等多种生物样本中得到验证,展现出广泛的适用性。使用该技术,生物学研究者可以用更快的速度、更低的成本、更保护样本的方式,去探索那些以往难以触及的领域——比如完整器官内的神经网络连接、肿瘤组织深处的微环境,以及发育过程中细胞群的协同行为。这项技术提供的不只是一张更清晰的图片,更是一个连接微观动态与宏观结构的桥梁,期待能够与更多领域的科学家合作,共同开启生物3D成像的新篇章。

上述研究成果以《结构光照明显微镜技术:实现从毫米厚组织到细胞动力学的高信噪比三维成像》(Structured illumination microscopy for high SNR 3D imaging from millimeter-thick tissues to cellular dynamics)为题发表在《创新》(The Innovation)。西安交通大学物理学院为论文第一单位,合作单位包括北京脑科学与类脑研究所、西安交通大学基础医学院、中国科学院上海有机化学研究所、华夏成像科技有限公司等多家单位。论文第一作者为西安交通大学物理学院王孟瑞博士,通讯作者为西安交通大学物理学院雷铭教授。这项工作得到了国家重点研发计划、国家自然科学基金等项目的资助。

雷铭教授团队长期从事先进光学显微成像技术及其在生物学中的应用研究,所研制的结构光照明超分辨显微镜具有国际领先水平,与国内外多家科研机构开展了研究合作。团队获批“先进光学成像融合人工智能”陕西省科技创新团队。(来源:西安交通大学)

4.中国科大揭示二维材料hBN中色心自旋弛豫的温度依赖特性

我校郭光灿院士团队在二维范德瓦尔斯材料固态自旋色心领域取得重要进展。该团队李传锋、唐建顺研究组与武汉理工大学吕海飞等人合作,实验研究二维材料六方氮化硼(hBN)中带负电荷的硼空位色心(VB-)中自旋态的两种弛豫过程,并利用理论模型对弛豫速率随温度的变化进行分析。其结果对影响VB-色心退相干过程的自旋-声子相互作用提供深入的理解,也对基于VB-色心的量子传感器实际应用具有指导意义。相关成果3月25日发表在知名学术期刊《物理评论快报》上。

hBN中的VB-色心作为具有光学可寻址特性的电子自旋系统,已被证实是量子传感领域极具潜力的候选材料。然而,在基于VB-色心的量子传感器实际应用中,可能出现机械振动或热量积累等因素造成的局域温度升高现象。由于VB-色心中存在的温度依赖性弛豫,温度变化会影响其自旋相干时间,进一步影响传感器的性能。

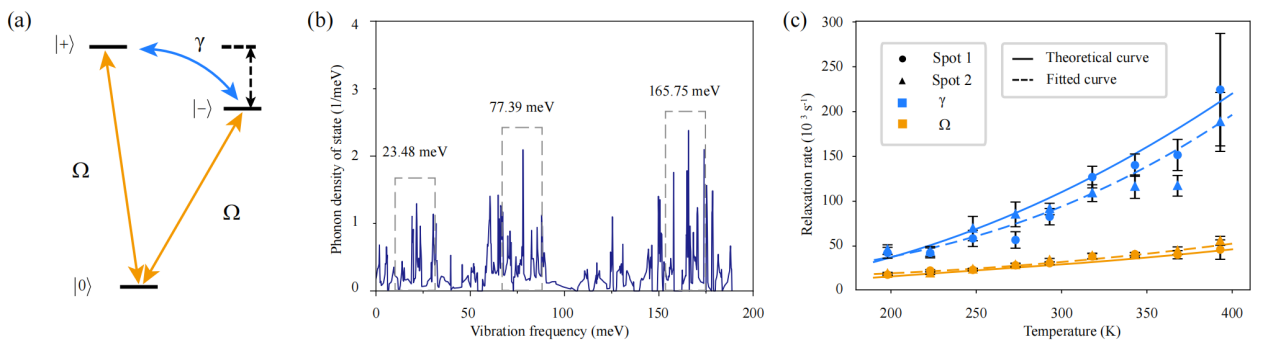

研究团队选择以hBN中的VB-色心为研究对象,测量了198-393 K温度范围内自旋态∣0〉⟷∣±〉间的弛豫速率(即单量子弛豫,简称为SQ)和自旋态∣+〉⟷〡-〉间的弛豫速率(即双量子弛豫,简称为DQ),并发现两种弛豫速率均随温度的升高而增大。其中DQ弛豫速率增速更快,在超过393K后数值将超过SQ弛豫速率数值的3倍,即DQ将在由自旋-声子相互作用导致的退相干过程中起主要贡献作用。

此外,研究通过建立基于二阶自旋-声子相互作用的理论模型描述SQ和DQ两种弛豫速率的温度变化,其结果与实验数据基本符合。通过进一步将理论模型简化成自旋与3种有效声子模式(对应能量分别为23.48,77.39和165.75meV)耦合,再对实验数据进行拟合,其结果和理论预测也基本一致。

图:(a)VB-色心简化的基态三重态,∣0〉⟷∣±〉的弛豫速率记作Ω,∣+〉⟷〡-〉的弛豫速率记作γ;(b)VB-色心的声子态密度图像,选取三个峰值为有效声子模式;(c)温度依赖的Ω和γ拟合曲线与理论计算曲线的对比。

本研究为VB-色心温度依赖性的退相干路径提供了有价值的见解,对超过393K后影响VB-色心相干时间的弛豫行为进行预测,这种研究方法具有延伸到hBN中其他自旋色心的潜力,对传感领域具有重要意义。

中国科学技术大学博士生解琳珂、博士后刘伟和武汉理工大学硕士生黄凯宇为该论文共同第一作者。该工作得到了国家自然科学基金、安徽省自然科学基金、中国博士后科学基金、中国科学院、合肥国家实验室、中国科学院青促会以及中国科学技术大学-六盘水师范学院对口合作发展联合基金的支持。(来源:中国科学技术大学)