【嘉德点评】台积电的此项发明能够为MOS晶体管性能带来改善,主要包括驱动电流的改善、泄露电流的减小以及高的开关电流比等等。相较之下,三星采用了GAA的工艺架构,使得两者再次走上了不一样的道路,不过随着后续产品的落地,台积电和三星势必要殊“死”一搏,一争高下!

台积电和三星是半导体领域的两大“霸主”,他们在整个半导体行业都有着举足轻重的分量,甚至每一次的技术革新,都会牵动着业内的发展方向。而随着摩尔定律进入3nm工艺节点之后,两家公司却选择了不同的3nm工艺架构,其中台积电选择在3nm中继续沿用FinFET架构。

“当价格不变时,集成电路上可容纳的晶体管的数目,约每隔18~24个月便会增加一倍,性能也将提升一倍”,这就是著名的摩尔定律。如果要增加集成电路上晶体管的数目,最有效的方法就是减小晶体管的尺寸,我们就拿常见的MOS晶体管来举例。

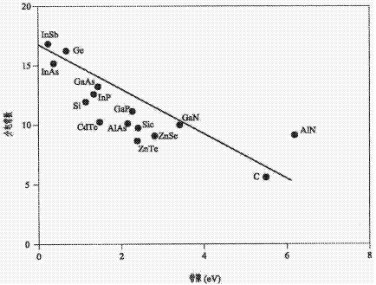

半导体产业面对的挑战是虽然在锗和Ill-V化合物半导体上形成的MOS晶体管具有高驱动电流,但是这些MOS晶体管的泄露电流也高。当漏电达到一定程度的时候,就相当于晶体管一直处于开启状态,这些漏电流会全部转换成发热量,因此漏电变大会直接导致 CPU 发热量上升。而这部分的问题主要是由于锗和III-V化合物半导体的低带隙和高介电常数而造成的。

图1半导体材料的带隙和介电常数比较示意图

图1表示了一些半导体材料的带隙和介电常数的比较。可以看到锗和一些常用的III-V化合物半导体的带隙很小。因此,各MOS晶体管在它们的栅和源/漏区之间将产生带-带泄露电流。这些材料的高介电常数进一步恶化了泄露电流。进而就导致这些MOS晶体管的开关电流比(Ion/Ioff)也相对较低。

为此,台积电早在2009年就申请了一项名为“具有改进的开关电流比的高迁移率多面栅晶体管”的发明专利(申请号:200910210197.0),申请人为台湾积体电路制造股份有限公司。该发明提出了一种新型的鳍式场效应晶体管(FinFET)架构。

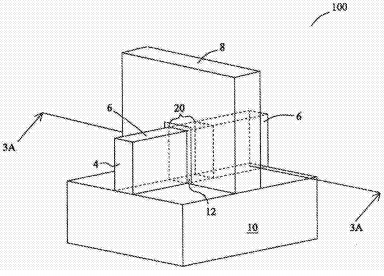

图2 一种FinFET架构的透视图

图2显示了形成在基体材料10上的FinFET 100的透视图,基体材料10可以由电介材料或半导体材料(比如二氧化硅、锗、砷化镓等)形成。FinFET 100主要包括源区4、漏区6以及其间的鰭20。图中的12是指的栅电介质12,它可以形成在鳍20的顶端和相对侧壁上,而栅电极8是形成在栅电介质12上的。

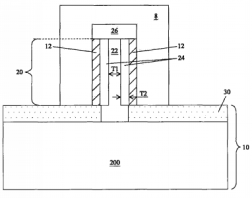

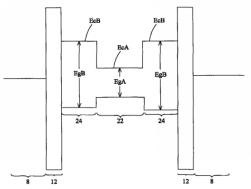

图3A 双栅FinFET剖面图 图3B 3A实例的能带图

剖面图3A为通过穿过图2中的线A-A'的垂直面而做出,其中鰭20包括由第一半导体材料形成的中心鰭22以及半导体层24。而栅电介质12可以由常用的电介质材料,如二氧化硅、氮化硅、氮氧化物及其多层,以及它们的组合而形成。栅电极8可以由掺杂多晶硅、金属、金属氮化物、金属硅化物等等形成。

图3B示出了图3A所示的双栅FinFET的能带示意图。中心鳍具有带隙EgA,同时半导体层24具有大于带隙EgA的带隙EgB。参考图3A,在中心鳍22的带隙EgA低于半导体层24的带隙Egg时,鳍20(包括中心鳍22和半导体层24)形成量子阱。当非零栅电压施加到栅电极8上时,由于量子限制效应,电子趋于流经鳍20的中心部分,也就是中心鳍22。因此,载流子迁移率由于低的带隙EgA而很高,从而各FinFET 100的开电流Ion很高。

另一方面,当FinFET 100被关闭时,栅电压为零伏,电子趋于流经鳍20的表面层,也就是半导体层24。因此,载流子迁移率由于高的带隙EgB面很低,从而各FinFET 100的关电流(泄露电流)Ioff很低,这样就使得FinFET 100具有高的开关电流比。而且为了改善FinFET 100的性能,量子阱需要增强。所以,中心半导体鳍20的厚度Tl一般都会比较小。

台积电的此项发明能够为MOS晶体管性能带来改善,其包括驱动电流的改善,泄露电流的减小,以及高的开关电流比等等。相较之下,三星采用了GAA的工艺架构,使得两者再次走上了不一样的道路,不过随着后续产品的落地,台积电和三星势必要殊“死”一搏,一争高下!

关于嘉德

深圳市嘉德知识产权服务有限公司由曾在华为等世界500强企业工作多年的知识产权专家、律师、专利代理人组成,熟悉中欧美知识产权法律理论和实务,在全球知识产权申请、布局、诉讼、许可谈判、交易、运营、标准专利协同创造、专利池建设、展会知识产权、跨境电商知识产权、知识产权海关保护等方面拥有丰富的经验。