芯观点──聚焦国内外产业大事件,汇聚中外名人专家观点,剖析行业发展动态,带你读懂未来趋势!

集成电路行业的金科玉律——摩尔定律正面临着失效的严峻挑战。随着晶体管通道尺寸逼近物理极限,只追逐线宽缩小,已无法满足新技术所需的标准。“后摩尔时代”来临,业界都开始探寻延续摩尔定律生命周期的方法,而3D先进封装技术则是其中一个新的突破口。

纵向扩展

此前芯片多采用2D平面封装技术,大部分一个封装只有一块芯片。但随着异构计算应用需求的增加,能将不同尺寸、不同制程工艺、不同材料的芯片集成整合的3D封装技术,已成为兼顾更高性能和更高灵活性的必要选择。

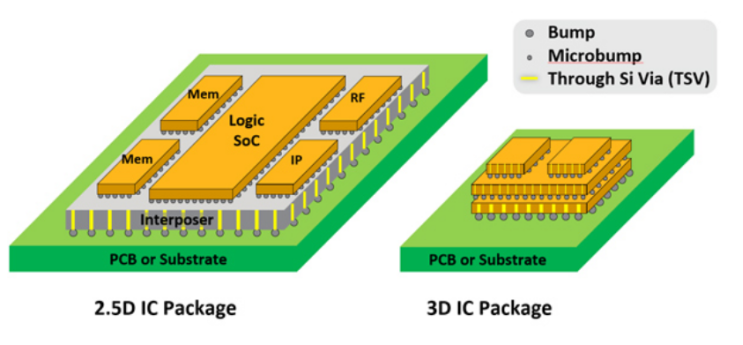

说到2D和3D封装,就绕不开两者之间的过渡性技术:“2.5D”封装。2.5D结构封装是在2D封装结构的基础上,在芯片和封装载体之间加入了一个硅中介转接层,该中介转接层上利用硅通孔(Through Silicon Via,TSV)连接其上、下表面的金属,多采用倒装芯片组装工艺。由于采用了中介转接层,其表面金属层的布线可以使用与芯片表面布线相同的工艺,使产品在容量及性能上比2D结构得到巨大提升。

相较于2.5D封装,3D封装的原理是在芯片制作晶体管(CMOS)结构,并且直接使用硅穿孔来连结上下不同芯片的电子讯号,以直接将存储器或其他芯片垂直堆栈在上面。此项封装最大的技术挑战便是,要在芯片内直接制作硅穿孔困难度极高。简单地说,相比于传统的封装,2.5D/3D封装相当于让芯片在纵向上有了一个扩展。

图:2.5D和3D封装技术(Source:ANSYS)

随着芯片越来越小型化,同时功能越来越强大,3D架构变得越来越重要。随着每一代便携式消费设备(例如智能手机和笔记本电脑)的问世,都需要比上一代设备具有更强大的功能和更高的性能。同时,可用于电气和电子元件的空间非常有限。而采用3D技术可缩短尺寸、减轻重量达40-50倍;在速度方面,3D技术节约的功率可使3D元件以每秒更快的转换速度运转而不增加能耗,寄生性电容和电感得以降低,同时,3D封装也能更有效地利用硅片的有效区域。

总体上看,3D封装在集成度、性能、功耗等方面更具优势,同时设计自由度更高,开发时间更短,是各封装技术中最具发展前景的一种。当前,随着高效能运算、人工智能等应用兴起,加上TSV技术愈来愈成熟,可以看到越来越多的 CPU、GPU 和存储器开始采用3D 封装。

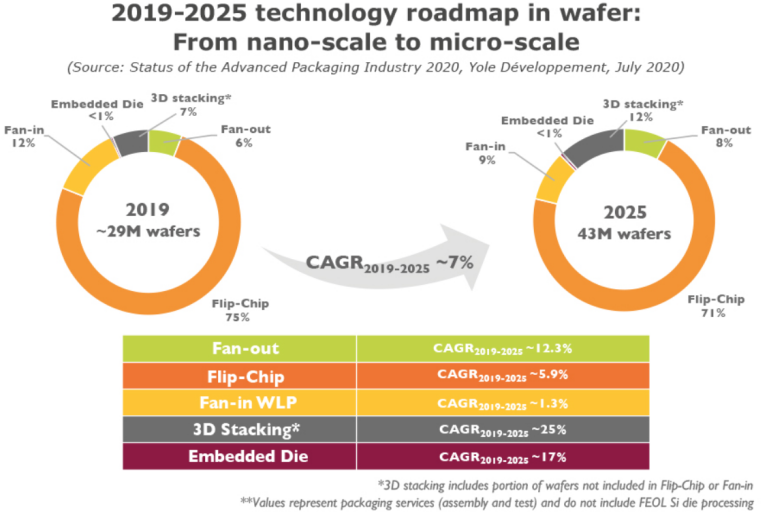

根据Yole、集微咨询综合整理,按晶圆数量(折合12英寸)来看, 2019 年约 2900 万片晶圆采用先进封装, 这一数字到 2025 年增长为 4300 万片,复合年均增长率为 7%。其中倒装技术占比最高,晶圆数量达3072万片,3D 封装增速最快,CAGR 约为 25%。

“意外”的入局者

有意思的是,3D先进封装并不只是传统封装企业的天下,反倒吸引了全球领先的三家晶圆代工巨头台积电、三星、英特尔先后入局。

不管是先进制程还是先进封装,台积电都走在行业领先地位。2018年,台积电宣布推出系统整合芯片(System on Integrated Chips;SoIC)的异质整合多芯片3D IC封装技术。SoIC是一种创新的多芯片堆叠技术,是一种将带有TSV的芯片通过无凸点混合键合实现三维堆叠。

SoIC技术的出现表明未来的芯片能在接近相同的体积里,增加双倍以上的性能。这意味着SoIC技术可望进一步突破单一芯片运行效能,更可以持续维持摩尔定律。对于台积电而言,SoIC更重要的意义在于能对10纳米或以下的制程进行晶圆级的键合技术,这将有助于台积电强化先进工艺制程的竞争力。

2020年,台积电表示已整合旗下 SoIC、InFO 及 CoWoS 等 3D IC 技术平台,并命名为“3D Fabric”。

英特尔同样倾心于3D封装。2018年12月,英特尔首次展示了逻辑计算芯片高密度3D堆叠封装技术Foveros,采用3D芯片堆叠的系统级封装(SiP),来实现逻辑对逻辑(logic-on-logic)的芯片异质整合。

多IP组合灵活(异构),并且占用面积小、功耗低,是Foveros最显著的特点。特别是结合上英特尔10nm制程,摩尔定律从晶体管密度(2D)到空间布局(3D)两个维度得到延续。Foveros 有望首次将芯片的堆叠从传统的无源中间互连层和堆叠存储芯片扩展到CPU、GPU和人工智能处理器等高性能逻辑芯片。英特尔计划于 2023 年推出其首款基于 Foveros 的个人电脑旗舰中央处理芯片,代号为 Meteor Lake。

三星也不甘落后,于2020年8月宣布推出名为“X-Cube”3D IC封装技术。事实上,三星已通过X-Cube封装技术将4颗SRAM堆栈在逻辑核心运算芯片上,并通过TSV技术进行连接,X-Cube封装技术已应用于7nm EUV制程,并在下一代5nm制程进行验证,未来将锁定HPC、5G、AI等应用领域。

过去,晶圆代工与封装厂基本都是各司其职,为何到了“后摩尔时代”,晶圆代工厂会选择自己做先进封装?

据集微网综合分析,主要有以下几个原因。一是,集成电路设计的复杂性和流片成本不断提高,微系统集成封装和系统组装的作用越来越大。集成电路和封装的协同设计已成为产品成功的关键。这也是芯片巨头积极探索 3D 封装技术及其他先进封装技术的重要原因。

二是,先进封装大部分是利用晶圆厂的技术,直接在晶圆上进行,由于这种技术更适合晶圆厂来做,因此台积电的先进封装大多是自己来做的。

三是,这也是晶圆代工取得订单的重要手段。在高效能、高整合、小面积、低功耗等IC产品要求下,加上各晶圆代工厂都希望能与客户达成更紧密的合作,先进封装技术就成了拿下客户的法宝之一。2016年,台积电击败三星电子,取得苹果(Apple)A系列应用处理器独家晶圆代工订单,其中所凭借的,除先进的制程技术外,当时台积电所开发全新IC封装技术整合型扇出晶圆级封装(Integrated Fan Out Wafer Level Package;InFO WLP)亦成为胜出关键因素之一。自此,也让后段IC封装技术成为IC制造的重要显学。

四是,领先的晶圆厂也借此拉开与其它晶圆厂的工艺差距。台积电和三星等晶圆厂在先进封装技术上的布局,助其在摩尔定律的法则中不断延续,向5nm、3nm、2nm甚至1nm工艺上突进,这也使得其它晶圆厂在工艺上的差距与他们越来越远。

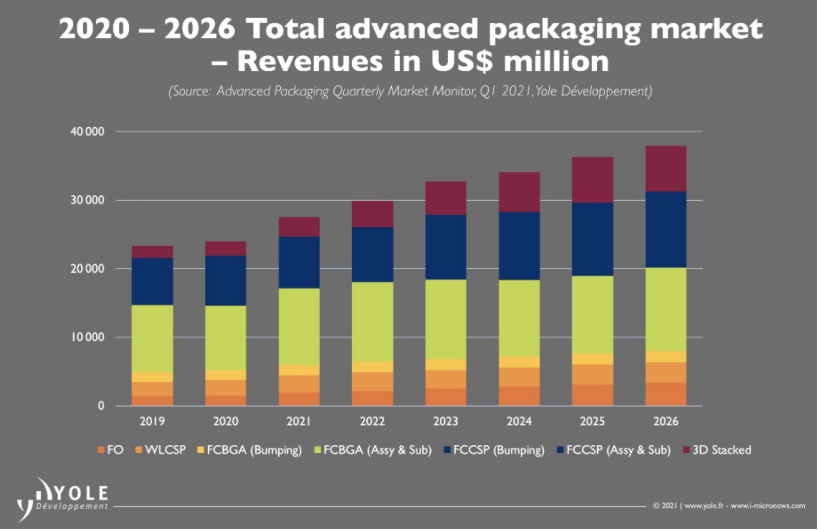

最后,可期而庞大的市场发展前景也是晶圆厂入局先进封装的原因之一。根据Yole Developpement最新的数据,2020年至2026年,先进封装市场复合年增长率约为7.9%。到2025年,该市场营收就将突破420亿美元,这几乎是传统封装市场预期增长率(2.2%)的三倍。

冲击传统封测厂商?

对于入局3D封装技术的行为,尽管英特尔、台积电等均表示,开发3D封装技术的主要目标,并非要与专业封测代工厂(OSAT)竞争,但不可避免的是,这一趋势必然会对原有产业格局造成影响。

事实上,自从台积电创始人张忠谋 2011 年宣布进军封装领域以来,台积电对其他封测厂的“威胁论”就不曾间断。据此前台媒报道,面对外界疑问,全球封测巨头日月光投控营运长吴田玉先前就曾回应,台积电的先进封装布局,与日月光的运营模式、生意模式都不同,而两家公司所锁定的客户群、产品应用也不一样。

对于晶圆代工厂入局先进封装领域,业内一家知名的封测公司也指出,晶圆代工龙头所发展的 2.5D/3D IC 封装制程属于晶粒堆栈的高端技术,而公司主要产品为导线架封装,如 QFN、QFP、SOP 等,均属中低阶、成熟的技术,两者的产品定位不同,并没有冲突。

除了产品定位之外,客户定位同样不一样。据拓墣产业研究院分析师王尊民此前分析,台积电与其他封测厂(OSAT)之间最主要的分水岭,还是在先进制程的应用上面。台积电的先进封装技术锁定第一线大厂如英伟达、AMD,甚至是未来英特尔的高端产品;而其他非最高端的产品,则会选择 Amkor、长电、日月光等封测厂来进行代工。

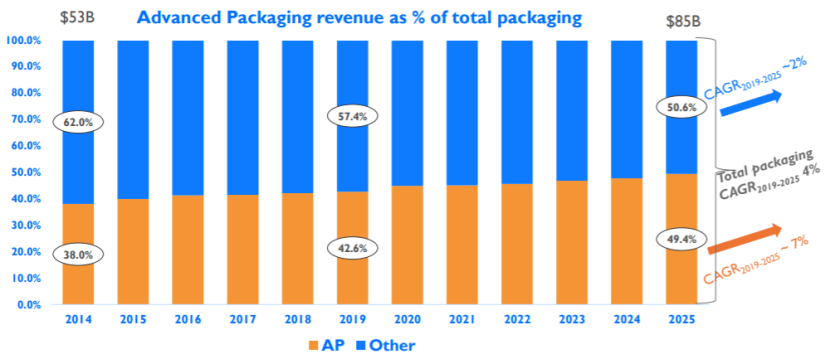

图:先进封装市场规模,来自Yole

虽然先进封装未来发展势头迅猛,但需要指出的是,目前传统封装市场规模仍高于先进封装,分别占约50%以上、40%以上,如上图所示。许多终端电子产品及应用(如家电、工业用 IC),并不需要用到最先进的制程和封装技术,因此,传统封装仍具有一定市场需求。

业内人士曾指出,从技术应用来看,虽然大家的焦点都锁定在高级的封测技术,但封测产业中,传统封测由于产品覆盖面广、成本低等优势,市场贡献值依旧不低于先进封装,而且未来这些传统封装并不会消失,因为市场上还有许多这方面应用的需求,但比例会逐年减少。而高级封装则多半是应用在移动装备上。

另有业内人士还表示,对晶圆厂来说,先进制程成本越来越贵,相较之下,先进封装投资较低,却可带来显著的效益,自是积极投入的领域;而封测厂在先进封装的策略就截然不同,其优势在于多样化的封装技术以及庞大产能,可为客户提供一站式且平价的解决方案。

因此,从大方向来看,不论是传统还是先进封装,各有各的市场与需求,对封测厂来说,至少在未来几年内,都将与上游晶圆代工厂呈现“合作中又有竞争”的态势。面向未来,不论对晶圆厂还是封测厂来说,如何在封装中堆栈多种芯片,并且还要做到小而薄,都是先进封装的关键因素。

结语:可以预见,“后摩尔时代”,任何先进技术、先进材料的争夺赛都将更为激烈,而3D封装技术也终将在新时代大展拳脚,拿下属于自己的市场。(校对/holly)

评论

文明上网理性发言,请遵守新闻评论服务协议

登录参与评论

0/1000