在3nm的争夺才初见分晓之际,2nm却已看似刀光剑影。

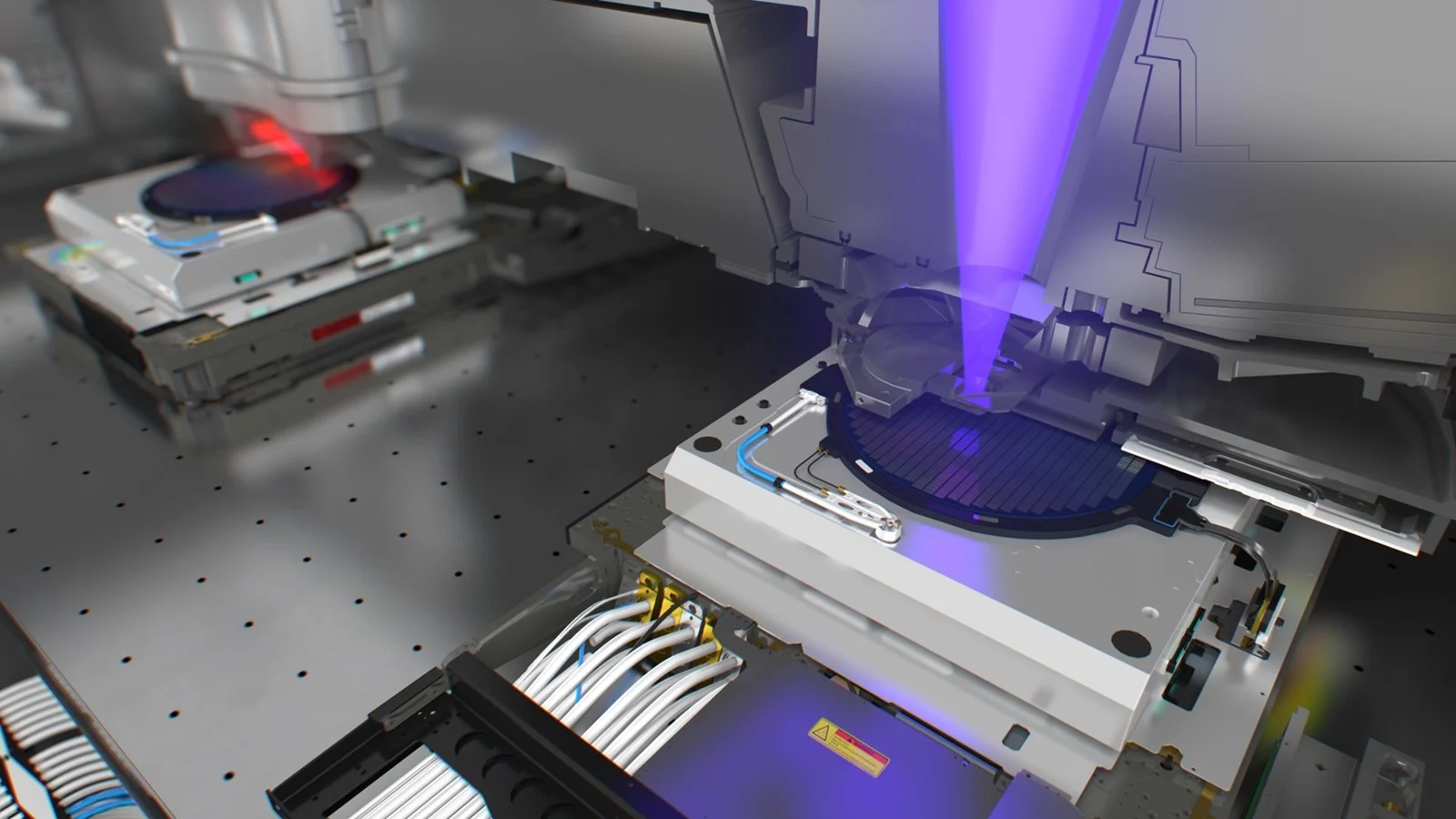

全球代工三大龙头台积电、三星以及英特尔均在加速开发更先进的2nm工艺,且各有绝招,英特尔的背面供电、TGV;台积电的GAA、CoWoS;三星的MBCFET等等。但在关键的设备领域,无疑High NA EUV成为必须争抢的“堡垒”。

看起来是英特尔先声夺人。近日英特尔大举采购ASML即将在2024出货的下一代高数值孔径High NA EUV光刻机,采购数量为6台,将在2025年及以后用于使用18A或其它工艺的芯片制造。行业估计,ASML明年余下4台产能将由三星晶圆代工和台积电瓜分,三星预计拿到3台,台积电明年很可能只有1台。

难不成台积电“慢了半拍”?但多位行业人士分析,台积电不疾不徐背后有着深厚的底气和实力,台积电是着眼于未来稳扎稳打,未来2nm争夺不只命系高数值孔径EUV,地缘政治的因素或更难预料。

2nm命系High NA EUV?

这也引发一大思考:2nm真的命系High NA EUV?

知名市调机构资深分析师对集微网表示,从目前来看,7nm工艺可采用DUV,而通过多重曝光则可支持5nm,但到了3nm以及2nm之后,想要比其他竞争者更快地推进摩尔定律,必须采用EUV。目前,EUV光刻机可支持工艺推进到3nm左右,但代工厂商若要继续推进到2nm甚至更小尺寸,就需要更高数值孔径的High NA EUV。

为进一步提升EUV光刻机的分辨率,适应下一代2nm以下制程的要求,独步天下的光刻机厂商ASML已经推出高数值孔径NA为0.55的光刻机平台EXE。目前第一代EUV光刻机NXE平台型号已经升级到3600D,而即将推出的第二代High NA EUV——EXE平台的试产型号是5000,量产型号是5200。

据悉,配备0.55 NA镜头的High NA EUV光刻设备可实现8nm的分辨率,与配备0.33 NA镜头的标准EUV 13nm分辨率相比,进步显著。预计High NA EUV将成为2nm以下工艺的关键工具,将在后2nm级工艺中发挥至关重要的作用,而这些技术要么需要使用低数值孔径EUV多重曝光,要么需要使用高数值孔径EUV。

从时间表来看,2nm开发已然愈行愈近。

目前,最先进的量产技术是3nm工艺,三星于去年6月开始量产,而台积电则于去年年底量产。在2nm层面,三星计划在2025年上半年量产,台积电也将量产时间表定于2025年下半年。而英特尔最为激进,自提出IDM2.0转型以来提出了四年五个节点计划,计划于今年上半年量产20A即2nm级产品,下半年开发18A工艺1.8nm产品,以期后来居上在2nm节点重塑格局。

由此,High NA EUV的争夺大戏已然全面上演。

英特尔进可攻退可守

之所以英特尔先发制人,除前文提及其欲在2nm后发先至之外,更是决定英特尔未来代工走向的X因素。

有分析指出,2nm的量产对英特尔未来发展有决定性的关键影响,是对台积电发起进攻的成败节点。如果英特尔在2nm节点抢占先机,比台积电更快推出以及提升良率,那将是首家使用高数值孔径EDU并启动大批量生产的公司,有望获得一部分客户的认可及下单,那么其IDM2.0战略将顺利推进,有望在未来的代工格局中超越三星,走向新巅峰。

而且不止是设备领先,英特尔还有一招绝技傍身:英特尔将在Intel 20A制程节点首次采用背面供电BSPDN技术。与EUV光刻机类似,BSPDN被视为继续开发下一代先进工艺的创新技术,是代工巨头争夺的又一个竞争高地。而在背面供电层面,英特尔一马当先,台积电和三星要落后一两年后采用。双重保险之下,英特尔看似胜券在握。

但如果失去这一良机,有激进分析说,英特尔或将Fab-lite进行到底,甚至转身成为Fabless。只是从目前来看,英特尔可谓进可攻退可守,无论是固守还是剥离,都将是一笔可观的资产。

正因2nm节点对英特尔来说至关重要,英特尔的大举押注自不在话下。英特尔目前购买的是ASML的EUV测试设备Twinscan EXE:5000,以学习如何更好地使用High NA EUV设备,获得宝贵的经验,并计划从2025年开始采用Twinscan EXE:5200量产18A制程芯片。

关键的问题是英特尔能否借此扭转战局?目前来看,英特尔面临的挑战重重。一方面,High NA EUV成本居高不下,试产的高数值孔径EUV光刻机的造价成本也超过3亿美元。另一方面,High NA EUV设备本身还面临不少难题,如可以支持光子散粒噪声和生产力要求的光源;满足0.55NA小焦点深度的解决方案;计算光刻能力;掩膜制造和计算基础设施包括新型材料等等,这些都需要英特尔付出时间和心血持续打磨。

而且,英特尔的竞争对手也在寻求获得高数值孔径EUV。三星电子副董事长兼设备解决方案部门负责人Kyung Kye-hyun在前不久表示,该公司与ASML就采购高数值孔径EUV达成协议。“三星已经确保了高数值孔径设备技术的优先权,”Kyung Kye-hyun说:“我相信,从长远来看,我们创造了一个机会,可以优化高数值孔径技术在DRAM存储芯片和逻辑芯片生产中的使用。”

此外,虽说台积电不疾不徐,或晚于英特尔导入High NA EUV,但凭借20多年与ASML的革命“友谊”和实战经验,台积电未必不能反超。

2nm的战局走向

对于为何台积电不急着导入高数值孔径EUV的原因,台湾专家吴梓豪发文表示,由于目前ASML高数值孔径EUV的采购以及生产成本过高,从制程稳定度以及量产经济效益来看,未必有利于台积电在第一时间导入并占据优势。台积电是着眼于未来,其将会大力采购WPH达到220的下一代量产机型Twinscan EXE:5200,5200甚至WPH更高的5400机型的数量才是三大代工巨头未来竞争的重点。

还要看到的是,由于台积电在全球扩产建厂,资本支出或将大幅往海外扩厂倾斜。

而且台积电的“筹码”还在于:台积电对高数值孔径EUV是与ASML几乎同步开发,早在2021年ASML就与台积电合作前期研发比高数值孔径EUV更早的Alpha,并在台积电完成一系列量产优化之后,ASML才正式推出第一代的测试用高数值孔径EUV设备Twinscan EXE:5000,在高数值孔径EUV的使用上台积电的工程师们已然掌握先机。加之台积电与ASML20多年的互相成就和革命情感,待EUV达到合适成本之后,台积电从ASML手中拿到它想要的EUV可谓分分钟的事。

业界知名专家莫大康认为,英特尔期望借High NA EUV缩小差距,但实际上风险较大,因为成本太高,且需要配套材料和设备配合,需要长时间的磨合。台积电之所以淡定,可能也是认定英特尔不可能借此实现超越,否则台积电一定会拼尽全力争得先手。

“开发2nm,台积电也可通过原来的EUV加多次曝光来实现,台积电应该是想要等High NA EUV更成熟一些、配套生态再完备一些再出手。”莫大康进一步分析说。

但台积电的危机或许并不在于High NA EUV导入的早晚问题。

上述分析师指出,尽管在先进工艺层面强者恒强,但最近由于华为麒麟芯片代工事宜,台积电被推上浪尖,下一步美国会不会采取举措限制台积电代工还不好说。而且英特尔芯片在持续迭代,未来两三年英伟达竞争对手的AI芯片也有可能发展快速,如果美国进行供应链的管控,有可能会有订单转向三星以及英特尔,这些因素均将影响后续先进工艺的竞争格局。

评论

文明上网理性发言,请遵守新闻评论服务协议

登录参与评论

0/1000