享誉业界的Arm Tech Symposia 年度技术大会于今日在上海浦东丽思卡尔顿酒店拉开帷幕。本届Arm Tech Symposia以“让我们携手重塑未来”为主题,汇聚多位全球顶尖的技术领袖、生态伙伴和开发者,共同展示和探讨AI时代下芯片技术创新成果和未来发展趋势。锐成芯微应邀参与此次盛会,并在现场展示了基于自研技术的完整IP平台解决方案,吸引了业界的广泛关注,为ARM构架的SoC方案提供更多样的、高质量的IP选型。

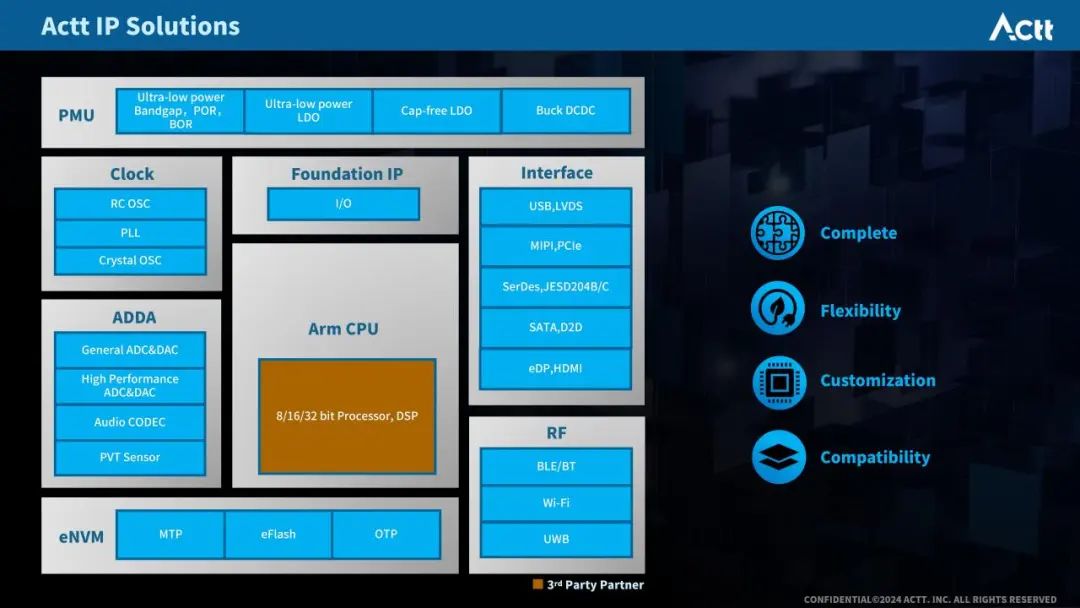

在人工智能的浪潮中,生成式AI、大语言模型、Chiplets、智能驾驶等前沿科技正不断突破,引领着应用场景创新。作为全球排名第10的物理IP提供商*,锐成芯微的IP平台化解决方案基于全球超30家晶圆代工厂、覆盖5nm~180nm的CMOS、FinFET、eFlash、BCD、HV、SiGe、FD-SOI等各类工艺平台,以充分挖掘工艺潜能及优化先进芯片设计竞争力,实现创新应用场景与芯片设计紧密联动。

得益于锐成芯微长期的生态建设,以及高性能低功耗模拟IP、高可靠性嵌入式存储IP、高性能无线射频通信IP、有线连接接口IP等系列IP技术和产品的多年研发和量产经验,已搭建完成的完整IP平台展现出了卓越的技术实力和市场竞争力。

高性能低功耗模拟IP

提供了高性能、低功耗的解决方案,广泛应用于电源管理、数据转换等领域。近期推出的基于8nm工艺的PVT Sensor IP,实现了IP的高集成度,简化了系统设计,节省芯片面积的同时,还具备先进的校准和补偿等技术以及低功耗、高精度和高分辨率、快速响应时间等优势。

高可靠性嵌入式存储IP

以高可靠性、低功耗的特点,满足了智能设备对存储性能的高要求。推出的SuperMTP®IP(车规级嵌入式非挥发性存储IP)顺利通过了AEC-Q100(B组)Grade 0可靠性等级认证,并获得了汽车芯片可靠性等级认证证书,为各类汽车芯片的高可靠性嵌入式存储IP方案提供了优质的选型。

高性能无线射频通信IP

已与全球头部数字基带IP厂商建立起官方的合作关系,锐成芯微能提供完整的Actt RF IP testchip + FPGA的蓝牙SoC demo方案,协助芯片设计公司快速完成系统集成和验证,加速产品面世时间。在2024年,锐成芯微成功在40nm车规工艺平台开发了应用于wBMS(无线电池管理系统)的蓝牙RF IP,并已授权给头部wBMS芯片厂商进行全光罩流片。

有线连接接口IP

涵盖180nm到6nm工艺节点、积累了24类物理层接口类IP的授权服务经验:在6/7/8nm,12/14nm,22nm,28nm等先进工艺节点完成56Gbps/28Gbps SerDeS IP研发。实现了16Gbps SerDeS IP,12.5Gbps JESD204B PHY,PCIE3.0 PHY,USB3.1 PHY,SATA3.0 PHY, MIPI PHY,GVI视频接口PHY,高性能PLL等IP产品的授权并量产,广泛应用于移动终端、存储设备、视频设备、人工智能、通信、高性能计算、FPGA芯片等高速接口领域。

锐成芯微在本次Arm Tech Symposia年度技术大会上的精彩亮相,不仅展示了其在芯片设计领域的强大实力,也为ARM构架的SoC方案注入了更多的活力。未来,锐成芯微将继续致力于技术创新和生态建设,携手全球合作伙伴共同推动芯片产业的繁荣发展。

关于锐成芯微

成都锐成芯微科技股份有限公司(简称:Actt;锐成芯微)成立于2011年,是集成电路知识产权(IP)产品设计、授权,并提供芯片定制服务的国家级“专精特新”高新技术企业。公司立足低功耗技术,逐步发展和构建完成以模拟及数模混合IP、嵌入式存储IP、无线射频通信IP及有线连接接口IP为主的产品格局,拥有国内外专利超140件,先后与全球超30家晶圆厂建立了合作伙伴关系,工艺覆盖5nm~180nm的CMOS、FinFET、eFlash、BCD、HV、SiGe、FD-SOI等各类工艺平台,累计在推广IP 750多颗,服务全球数百家集成电路设计企业,产品广泛应用于汽车电子、工业控制、物联网、无线通信、人工智能等领域。据 IPnest2023年排名,锐成芯微是全球排名第10的物理IP提供商,在IP细分领域具有显著的、持续的竞争优势,公司的模拟及数模混合IP排名全球第二、中国第一,无线射频通信IP和嵌入式存储IP分别排名中国第一和中国大陆第一。