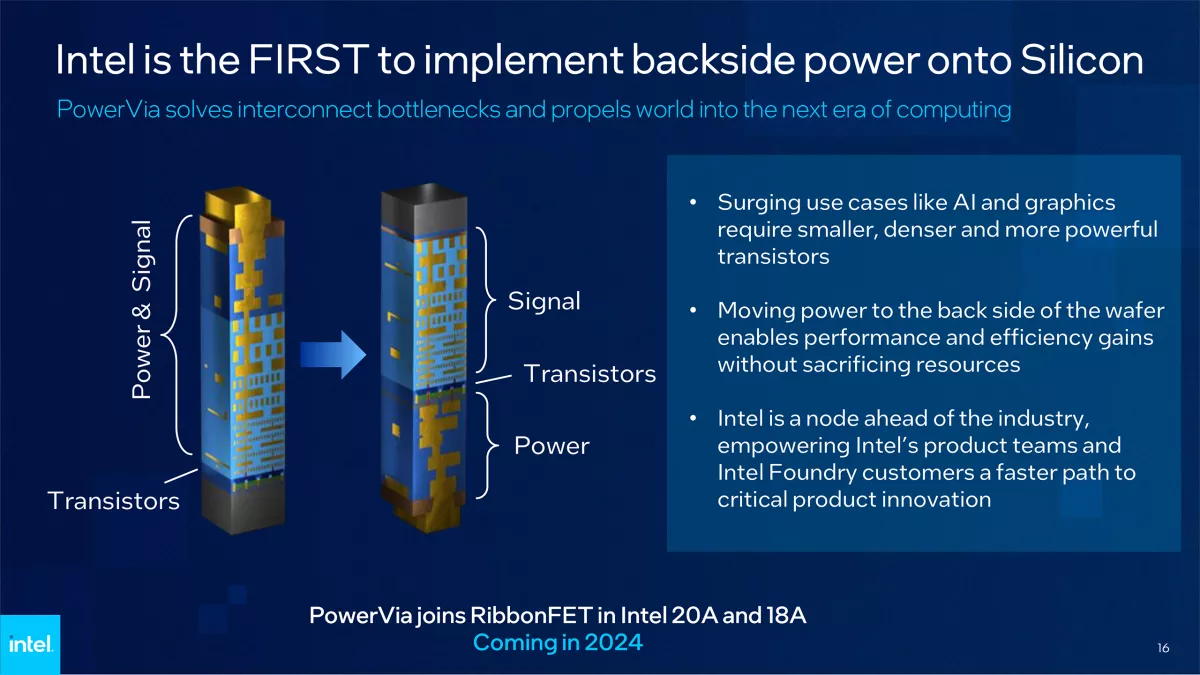

据Tom’s Hardware消息,英特尔于6月5日公布了其独家的BS PDN背面供电网络技术——PowerVia,幻灯片里展现了该技术最新的介绍以及特性详解,并公布该技术将用于英特尔18A、20A工艺节点,预计最早将在2024年投入制造。

英特尔18A、20A技术包含两项关键创新:RibbonFET栅极全环绕场效应管(GAAFET)以及PowerVia背部供电网络。前者英特尔此前已经介绍,爱集微也做过相关报道,本文将重点描述PowerVia技术。

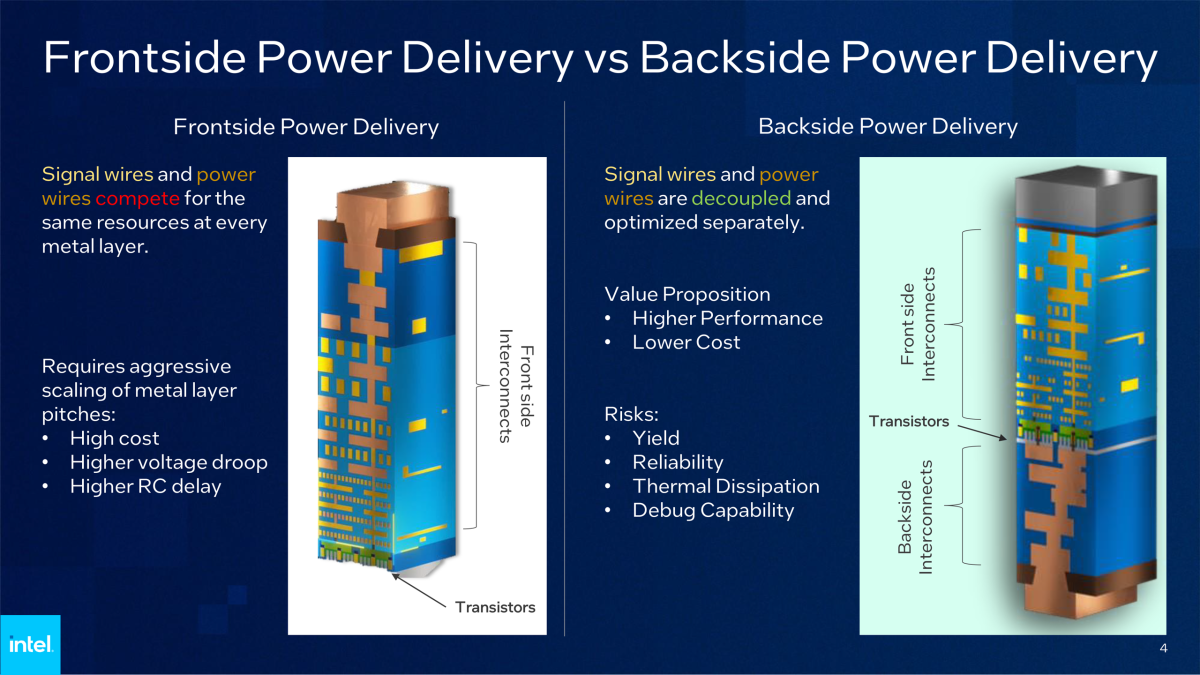

这项技术的目的在于分离芯片的供电电路和I/O数字信号电路,将此前电源网络布线转移至晶圆背部。这种方法可以解决线路后端通孔造成的电阻增加问题,最直接的好处是降低芯片的功耗,减少信号电路和电源之间的干扰,此外还有助于提高晶体管密度。

英特尔表示,随着时间推移,BS PDN背部供电网络将成为未来芯片的标配,这一技术将成为关键的芯片技术突破,其地位相当于2003年90nm节点的应变硅技术、2007年45nm节点的铪基高K金属栅极、2012年22nm节点推出的FinFET晶体管技术。

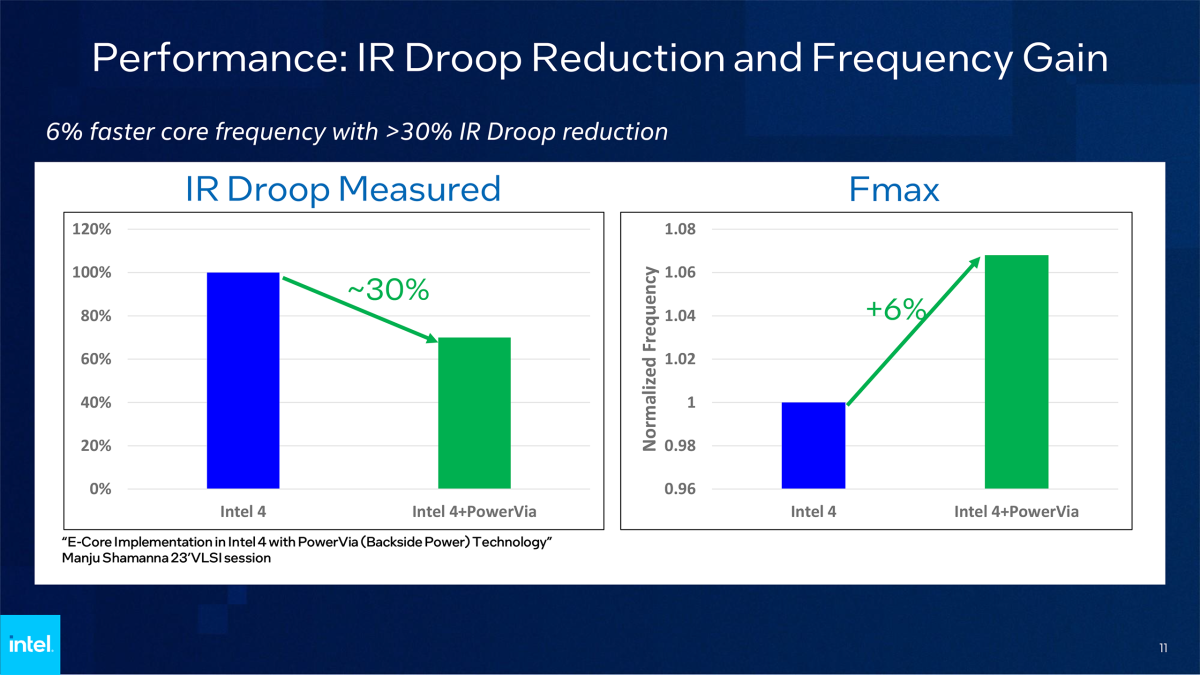

在实验室的测试中,采用PowerVia技术的芯片,主频可以提升6%以上,红外辐射降低了30%,并且使得E-core能效核心的电能利用率提升到了90%以上。

尽管该技术有明显的优势,但从芯片制造的角度看,想要实现还有许多的困难,生产流程有很大不同。如今生产最先进的芯片很近单,每片晶圆的制造都是从M0层开始,在Intel 4节点下,晶体管的宽度仅有30nm。使用EUV光刻机,对晶圆进行曝光蚀刻,然后反复重复沉积、掺杂、清洗、光刻等过程,逐层构建晶体管网络。

而如果想采用英特尔PowerVia BS PDN结构制造芯片,需要首先在晶圆正面搭建好逻辑层和信号线布线,然后翻转晶圆,再搭建供电电路网络。这会增加非常多的步骤,包括晶圆减薄、CMP清洁、测量、光刻等等。

这样的工艺可能不需要最先进的设备,但仍会增加制造成本。英特尔的幻灯片可以看出,传统的Intel 4工艺,晶圆包含15个金属层和1个再分布层(RDL),而Intel 4+PowerVia工艺,则包含正面14层、背面4层以及1个再分布层(RDL),使得晶圆的总层数达到至少18层。

英特尔技术开发副总裁Ben Sell表示,背部PDN结构有几个因素需要考虑:首先,它极大改变了晶圆加工工艺,英特尔必须找到一种高效的方法,以便保证芯片产量。其次,英特尔必须保证背面加工的PDN与目前使用的正面PDN一样可靠。第三,由于I/O电路和电源层位于晶体管的上下两侧,因此对芯片的冷却散热将会更有挑战性。第四,调试芯片的难度大大增加,因为背面的电源层挡住了晶体管。

英特尔的PowerVia工艺还有一个特点,那就是由于晶圆背部的单晶硅被大量移除,因此晶圆的刚性会明显减弱。这就需要引入一个承载晶圆放在信号层一侧进行固定,这对晶圆的加工也是一个挑战。

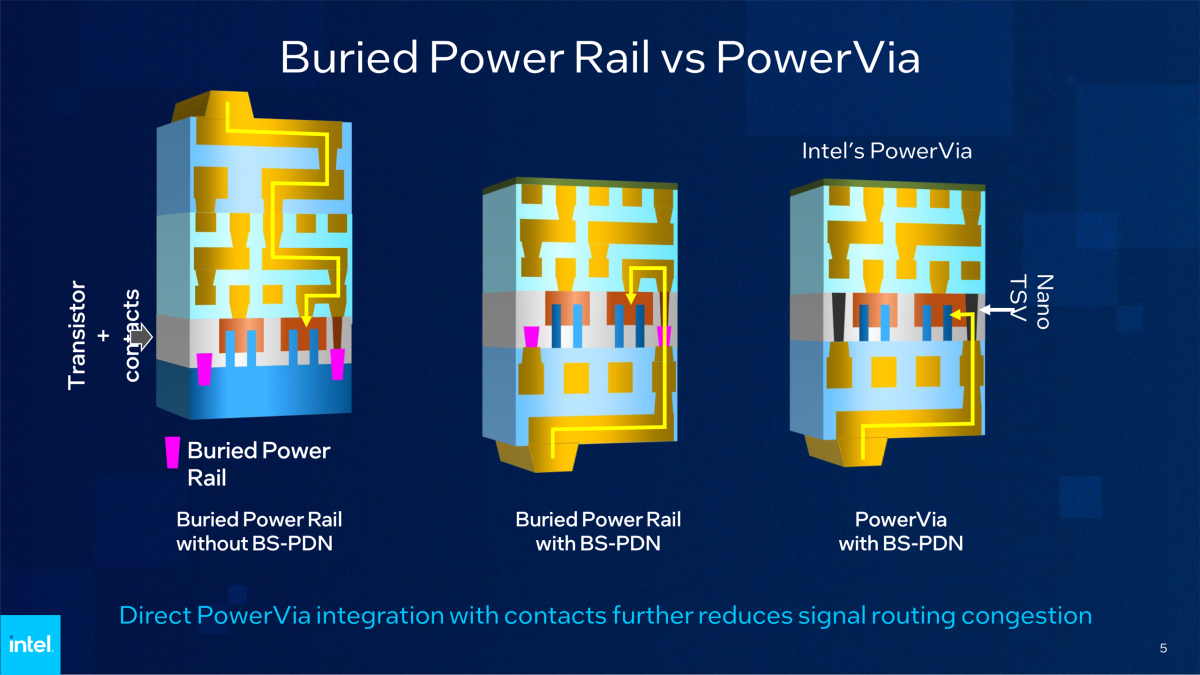

英特尔的PowerVia技术还有个特点,那就是相比通常的BS PDN,进一步减少了供电线路的长度,使用一个纳米硅通孔来直接将电流输送至晶体管。

为了测试PowerVia技术,英特尔基于其Intel 4节点工艺,构建了一个特殊的制造流程,英特尔起了一个名字叫Intel 4 + PowerVia,其中一款测试芯片名为Blue Sky Creek(蓝天溪)。这款芯片拥有两个晶片,每个都包含四个基于Crestmont微架构的高能效内核,在1.1V电压下,以3GHz主频运行。

良率方面,英特尔表示Intel 4和Intel 4 + PowerVia工艺,缺陷密度几乎相同,可靠性也符合预期,此外新工艺下芯片的运行温度也不会过高。英特尔已经开发了新的热管理方式,来提高冷却效率。

英特尔表示,20A 2nm节点将在2023年下半年开始试产,18A 1.8nm节点将在2024年上半年试产,这两代工艺都将应用PowerVia BS PDN技术。英特尔第一款采用20A工艺的CPU代号为Arrow Lake,预计将在2024年中期推出。

(校对/张杰)